# The Amstrad PPC Technical Reference Manual

SOFT 50031

AMSTRAD

<u>Cover</u> <u>Index</u> <u>Contents</u>

# **Preface**

This Technical Reference Manual is intended primarily to assist writers of software for the Amstrad PPC, although in conjunction with the PPC Service Manual it will be of interest to designers of add-on hardware.

It is assumed that the reader has a working knowledge of the Industry Standard architecture comprising of an 8086 (or 8088) with DMA, PIT, RTC and Interrupt Controller support chips; plus Colour Graphics Adapter (or Monochrome Graphics Adapter) with Floppy Disk, Serial and Parallel Adapters.

The information contained herein is largely unique to this document, with the exception of parts of the appendices which expand on the information contained in the PPC User Instructions and the Microsoft MSDOS Reference Manual.

Whilst the PPC implements a superset of the Industry Standard, this manual makes no attempt to identify those areas of the PPC specification which exceed the Industry Standard. Users should, therefore, exercise caution when writing software for a range of manufacturers' PCs and only use the "Lowest Common Denominator" facilities if simple portability is required.

Please note, that communications regulations do not allow the release of technical information relating to the circuitry or construction of the PC2000 modem.

© Copyright 1988 Amstrad Consumer Electronics Plc

Neither the whole nor any part of the information contained herein, nor the product described in this manual may be adapted or reproduced in any form except with the prior approval of Amstrad Consumer Electronics Plc ('Amstrad').

All information of a technical nature and particulars of the product are given by Amstrad in good faith. However, it is acknowledged that there may be errors or omissions in this manual.

All correspondence should be addressed to:

Amstrad Consumer Electronics Plc

Brentwood House

169 Kings Road

Brentwood

ESSEX CM14 4EF

All maintenance and service on the product must be carried out by Amstrad authorised dealers. Amstrad cannot accept any liability whatsoever for any loss or damage caused by service or maintenance by unauthorised personnel. This manual is intended to assist the reader in the use of the product, and therefore Amstrad shall not be liable for any damage or loss whatsoever arising from the use of any information or particulars in, or any error or omission in, this manual or any incorrect use of the product.

Written by Bill Weidenauer and edited by Susan Vass, Amstrad plc.

Published by Amstrad.

First Published 1987.

MS-DOS(R) is a registered trademark of Microsoft(R) Corporation

Amstrad is a registered trademark of Amstrad plc.

Unauthorised use of the trademark or the word Amstrad is strictly forbidden.

| Cover | Index | <u>Contents</u> |

|-------|-------|-----------------|

|       |       |                 |

<u>Intro</u> <u>Index</u> <u>Section 1</u>

# **Table of Contents:**

# **Section 1 - Hardware**

| <u>1.0</u> | <u>Introduction</u>                                |   | 1  |

|------------|----------------------------------------------------|---|----|

|            | 1.1 Central Processing Unit (CPU)                  |   | 1  |

|            | 1.2 Memory Layout                                  |   | 2  |

|            | 1.3 Main Board I/O Channels                        | ; | 3  |

|            | 1.4 Expansion Bus I/O Channels                     |   | 5  |

|            | 1.5 Direct Memory Access (DMA)                     |   | 5  |

|            | 1.5.1 DMA Page Registers                           |   | 6  |

|            | 1.5.2 DMA Initialization                           |   | 7  |

|            | 1.6 System Interrupts                              |   | 7  |

|            | 1.6.1 Interrupt Levels                             |   | 8  |

|            | 1.6.2 Interrupt Controller Initialization          | 1 | 8  |

|            | 1.6.3 NMI Mask Control                             | ! | 9  |

|            | 1.7 Programmable Interval Timers                   |   | 9  |

|            | 1.7.1 Timer Configuration                          |   | 10 |

|            | 1.7.2 Counter 1 initialization                     |   | 10 |

|            | 1.8 System Status and Control                      |   | 10 |

|            | 1.8.1 Port B - System Control                      |   | 11 |

|            | 1.8.2 Port A - Status-1 Input / Keyboard Code      |   | 12 |

|            | 1.8.3 Port C - Status-2 Input                      |   | 13 |

|            | 1.8.4 Write System Status-1                        |   | 14 |

|            | 1.8.5 Write System Status-2                        |   | 14 |

|            | 1.8.6 System Reset                                 |   | 14 |

|            | 1.9 Real Time Clock                                |   | 15 |

|            | 1.10 Parallel Printer Port                         |   | 15 |

|            | 1.10.1 Printer Data Latch                          |   | 16 |

|            | 1.10.2 Printer Control Latch                       |   | 16 |

|            | 1.10.3 Printer Status Channel                      |   | 17 |

|            | 1.11 The Internal display Adapter                  |   | 18 |

|            | 1.11.1 Colour Alpha Display                        |   | 19 |

|            | 1.11.2 Colour Graphics Display                     | : | 21 |

|            | 1.11.2.1 Low Resolution Graphics                   | : | 21 |

|            | 1.11.2.2 Medium Resolution Graphics                | : | 22 |

|            | 1.11.2.3 High Resolution (640 X 200) Graphics Mode | : | 23 |

|            | 1.11.3 Monochrome Display                          | : | 23 |

|            | 1.11.4 BIOS Modes                                  | ; | 24 |

|            | 1.11.5 Colour Mode Registers.                      | ; | 25 |

|            | 1.11.5.1 CGA Mode Control Register                 |   | 25 |

|            |                                                    |   |    |

| 1.11.5.2 Colour Select Register                 | 26 |

|-------------------------------------------------|----|

| 1.11.5.3 CGA Status Register                    | 27 |

| 1.11.5.4 CGA Mode CRTC initialization.          | 27 |

| 1.11.5.5 Set and Clear Light Pen Latch          | 29 |

| 1.11.5.6 Operation Control/Status Register      | 29 |

| 1.11.5.7 CRTC Index Readback                    | 30 |

| 1.11.5.8 CRTC Data Readback                     | 30 |

| 1.11.6 Monochrome Mode Registers.               | 31 |

| 1.11.6.1 MDA Mode Control Register              | 31 |

| 1.11.6.2 MDA Status Register                    | 32 |

| 1.11.6.3 Monochrome CRTC initialization.        | 32 |

| 1.12 Floppy Disk Controller                     | 34 |

| 1.12.1 FDC Hardware Conditions                  | 34 |

| 1.13 RS232C Asynchronous Serial Port            | 35 |

| 1.13.1 Serial Channnel Interface                | 35 |

| 1.13.2 Serial Channnel Pin Arrangement          | 36 |

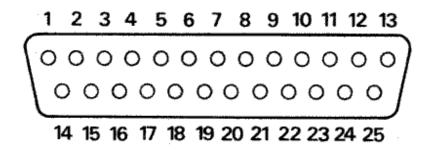

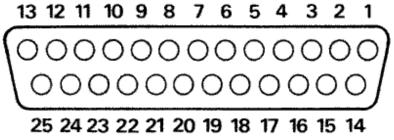

| 1.14 Parallel Printer Interface                 | 36 |

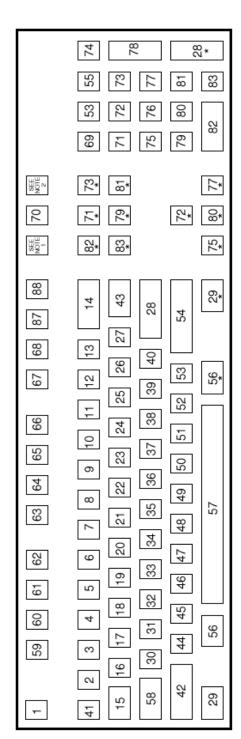

| 1.15 Keyboard Interface                         | 38 |

| 1.15.1 Serial Clock and Serial Data             | 38 |

| 1.15.2 Keyboard to Main Board Interface         | 38 |

| 1.15.3 Main Board to Keyboard Interface         | 38 |

| 1.15.4 Keycodes                                 | 39 |

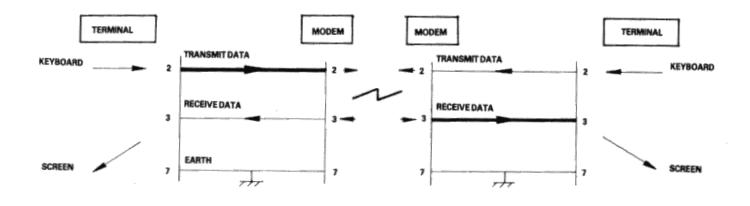

| 1.16 Modem Interface                            | 39 |

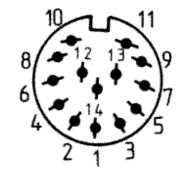

| 1.16.1 Modem Connector                          | 39 |

| 1.17 Light Pen Connector                        | 40 |

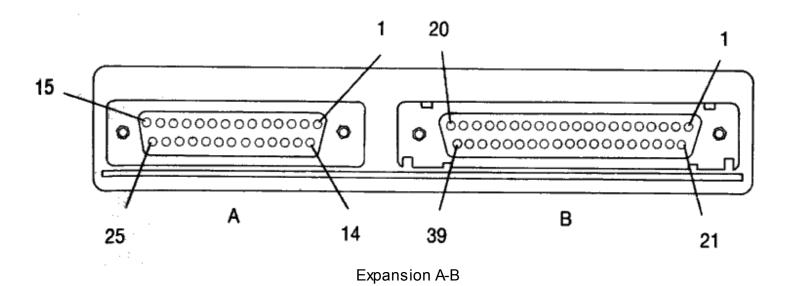

| 1.18 Expansion Interface Connectors             | 41 |

| 1.19 Video Connector                            | 44 |

| 1.20 Power Connectors                           | 45 |

| 1.20.1 The Adapter Power Connector              | 45 |

| 1.20.2 The Display Power Connector              | 45 |

| 1.21 PPC Switch Settings                        | 46 |

|                                                 |    |

| 2.0 Firmware                                    | 47 |

| 2.1 Power-Up Initialization and Self Test       | 47 |

| 2.2 Power-Up Self Tests                         | 52 |

| 2.2.1 Test Procedure.                           | 52 |

| 2.2.2 Test Methods.                             | 53 |

| 2.2.3 ROS Checksum Test.                        | 53 |

| 2.2.4 Direct Memory Access Controller test.     | 54 |

| 2.2.5 Programmable Interval Timer test.         | 54 |

| 2.2.6 Programmable Peripheral Interface test.   | 54 |

| 2.2.7 Real Time Clock test.                     | 54 |

| 2.2.8 Asynchronous Communications Element test. | 54 |

| 2.2.9 Printer Parallel Port test.               | 54 |

| 2.2.10 System RAM test.                         | 54 |

| 2.2.11 Programmable Interrupt Controller test.            | 55  |

|-----------------------------------------------------------|-----|

| 2.2.12 Disk test.                                         | 55  |

| 2.2.13 Keyboard Interface test.                           | 55  |

| 2.3 ROM Firmware Interrupts.                              | 55  |

| 2.3.1 Interrupt 2: Parity Error (NMI).                    | 55  |

| 2.3.2 Interrupt 5: Print Screen.                          | 56  |

| 2.3.3 Interrupt 8: System Clock Interrupt                 | 56. |

| 2.3.4 Interrupt 9: Keyboard Interrupt.                    | 57  |

| 2.3.4.1 Special Key Actions                               | 61  |

| 2.3.5 Interrupt 14: Floppy Disk Controller.               | 62  |

| 2.3.6 Interrupt 16: Video I/O.                            | 62  |

| 2.3.7 Interrupt 17: System Configuration.                 | 71  |

| 2.3.8 Interrupt 18: Memory Size.                          | 72  |

| 2.3.9 Interrupt 19: Disk I/O.                             | 72  |

| 2.3.9.1 Hard Disk Call Parameters and Registers           | 77  |

| 2.3.10 Interrupt 20: Serial I/O.                          | 79  |

| 2.3.11 Interrupt 22: Keyboard I/O.                        | 83  |

| 2.3.12 Interrupt 23: Printer I/O.                         | 87  |

| 2.3.13 Interrupt 24: System Restart.                      | 88  |

| 2.3.14 Interrupt 24: Disk Bootstrap.                      | 89  |

| 2.3.15 Interrupt 26: System Clock & Real Time Clock.      | 89  |

| 2.3.16 Interrupt 27: Keyboard Break Interrupt.            | 93  |

| 2.3.17 Interrupt 28: External Ticker Interrupt.           | 93  |

| 2.3.18 Interrupt 29: Video Parameter Table.               | 93  |

| 2.3.19 Interrupt 30: Disk Parameter Table.                | 95  |

| 2.3.20 Interrupt 31: Video Matrix Table.                  | 95  |

| 2.4 System RAM Variables.                                 | 96  |

| 2.5 Non Volatile RAM.                                     | 103 |

| 2.6 ROS Messages.                                         | 104 |

| 2.6.1 Non-Fatal ROS Messages.                             | 104 |

| 2.6.2 Fatal ROS Messages.                                 | 105 |

| 3.0 Reference Information.                                | 106 |

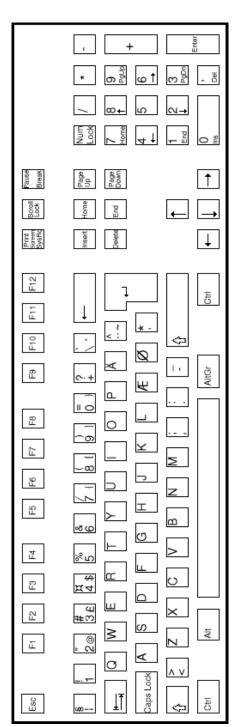

| 3.1 Language Links.                                       | 106 |

| 3.2 Processor Memory Usage.                               | 106 |

| 3.3 Asynchronous Communications Element (8250) Registers. | 107 |

| 3.4 High Performance Programmable DMA Controller          | 110 |

| (8237A-4) Registers                                       | 110 |

| 3.5 Programmable Interrupt Controller (8259A-2)           | 112 |

| Command Words.                                            | 445 |

| 3.6 Programmable Interval Timer (8253) Registers.         | 115 |

| 3.7 Real Time Clock (HD146818) Registers                  | 116 |

| 3.7.1 Time, Calendar and Alarm Locations                  | 117 |

| 3.7.2 RTC Register Locations                              | 119 |

| 3.8 Floppy Disk Controller (uPD765A).                     | 121 |

| <u>.</u>                     | <u>Index</u>                  | Section 1 |     |

|------------------------------|-------------------------------|-----------|-----|

| The RESTORE                  | Command                       |           | 221 |

| Appendix 18:                 |                               |           | 004 |

| Appendix 17:<br>The BACKUP ( | Command                       |           | 218 |

| The FDISK Util               | <u>ty Program</u>             |           |     |

| Appendix 16:                 | hy Drogram                    |           | 207 |

| The SHARE Ut                 | <u>lity Program</u>           |           | 200 |

| Appendix 15:                 |                               |           | 206 |

|                              | <u>Utility Program</u>        |           | 205 |

| Appendix 14:                 |                               |           | 005 |

| The EXIT Com                 | mand                          |           | 204 |

| The EXE2BIN U                | <u> </u>                      |           |     |

| Appendix 12:                 | Hility Program                |           | 202 |

|                              | <u>ility Program (DEBUG)</u>  |           | 100 |

| Appendix 11:                 |                               |           | 180 |

| COMMAND.CC                   | <u>M</u>                      |           | 179 |

| Appendix 10:                 | <del> </del>                  |           | ·   |

| Appendix 9:<br>The LINKER P  | ogram                         |           | 164 |

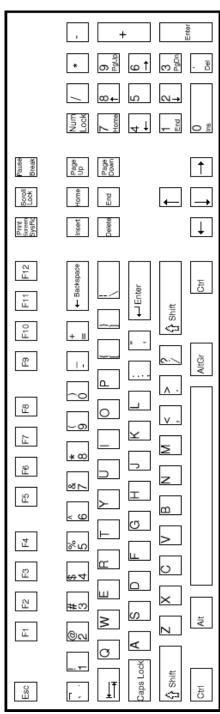

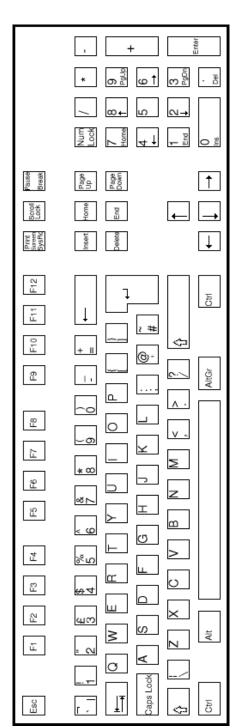

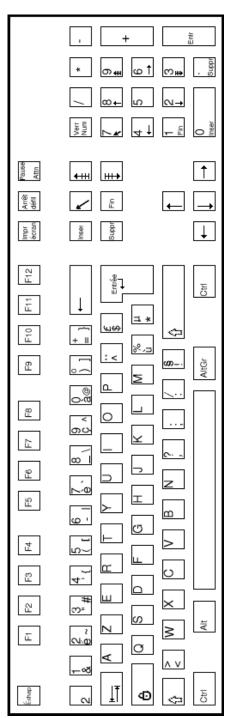

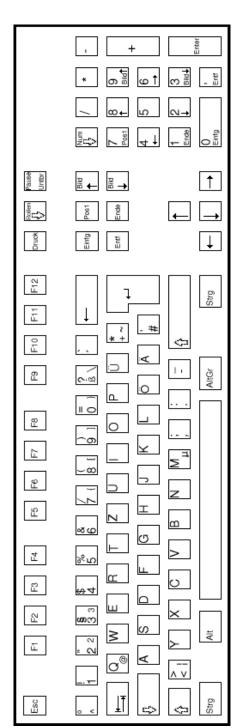

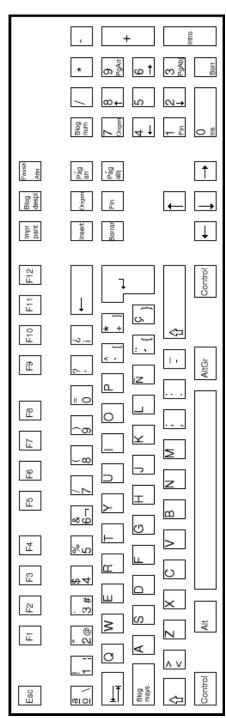

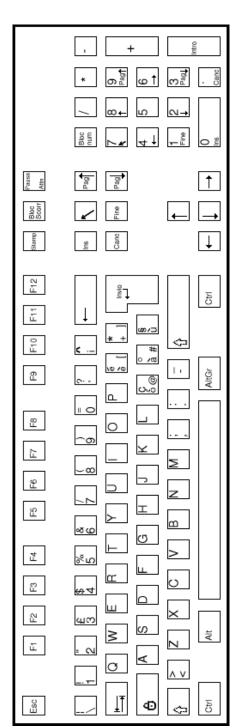

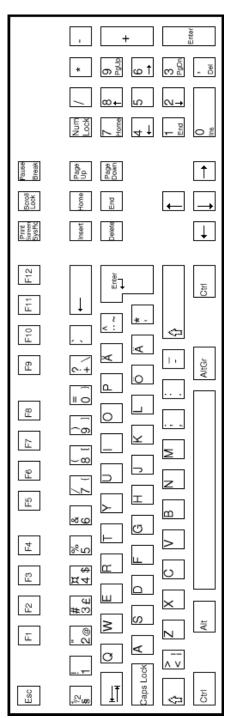

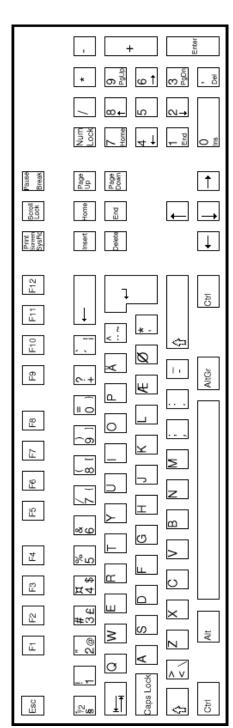

| Keyboard Layo                | <u>uis</u>                    |           |     |

| Appendix 8:                  | uto                           |           | 159 |

| Keyboard Keyo                | <u>odes</u>                   |           | 100 |

| Appendix 7:                  |                               |           | 158 |

| ROM Characte                 | <u>- Set</u>                  |           | 156 |

| Appendix 6:                  |                               |           | 150 |

| PPC Power Us                 | <u>age</u>                    |           | 155 |

| Appendix 5:                  | L-2/ Willing Opecinication    |           |     |

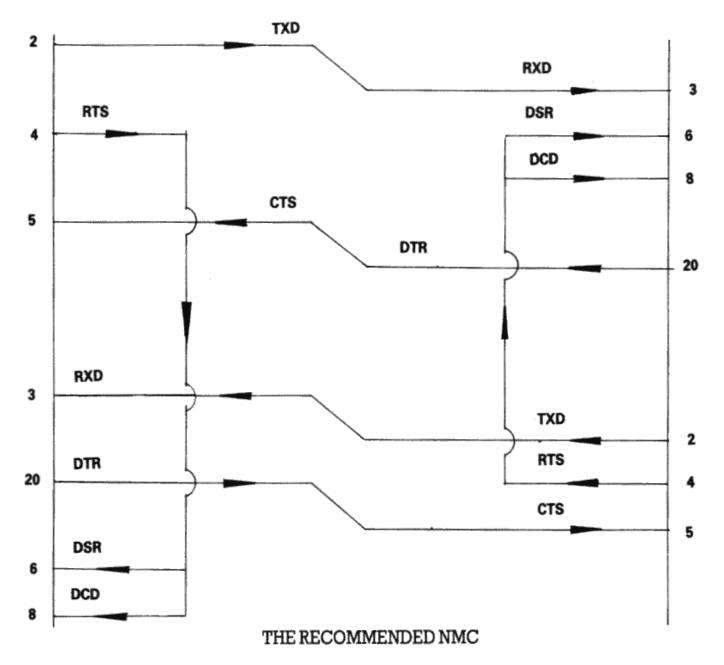

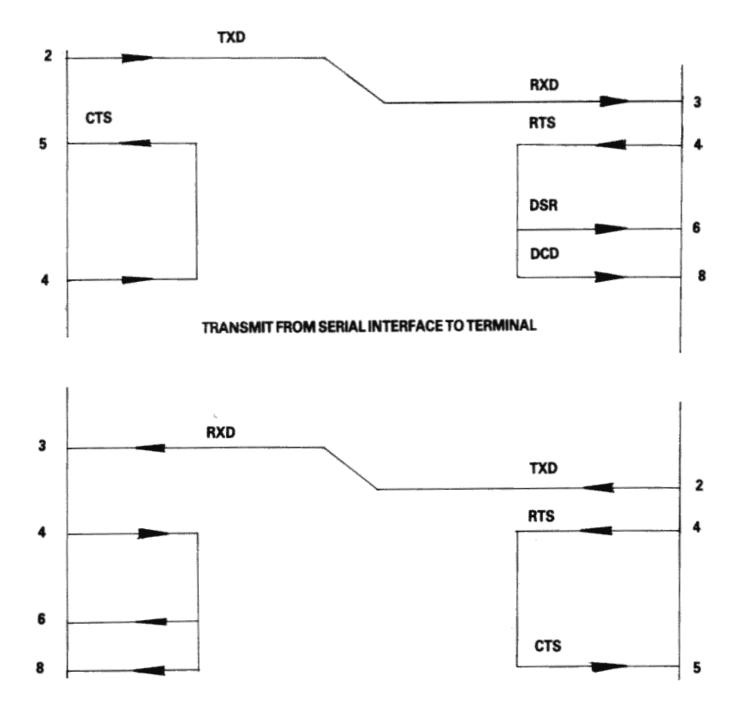

| Appendix 4:                  | L-2) Wiring Specification     |           | 153 |

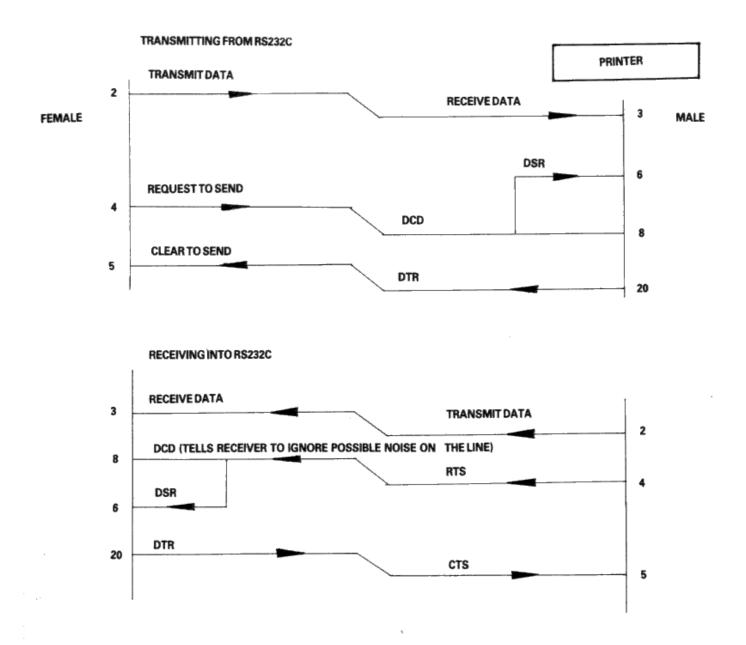

| RS232C Conn                  | <u>ections</u>                |           |     |

| Appendix 3:                  |                               |           | 14  |

| Country Depen                | dent Information for MS-DOS 3 |           | 144 |

| Appendix 2:                  | -                             |           | 144 |

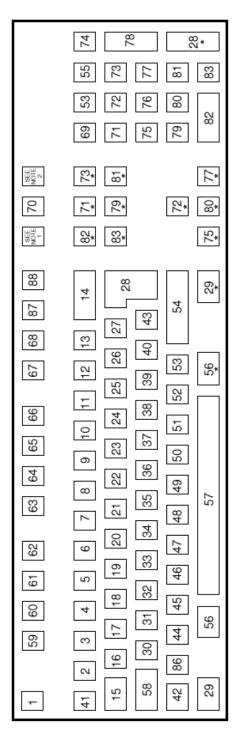

|                              | m Configuration               |           | 137 |

| Appendix 1:                  |                               |           |     |

# **Amstrad PPC Technical Manual**

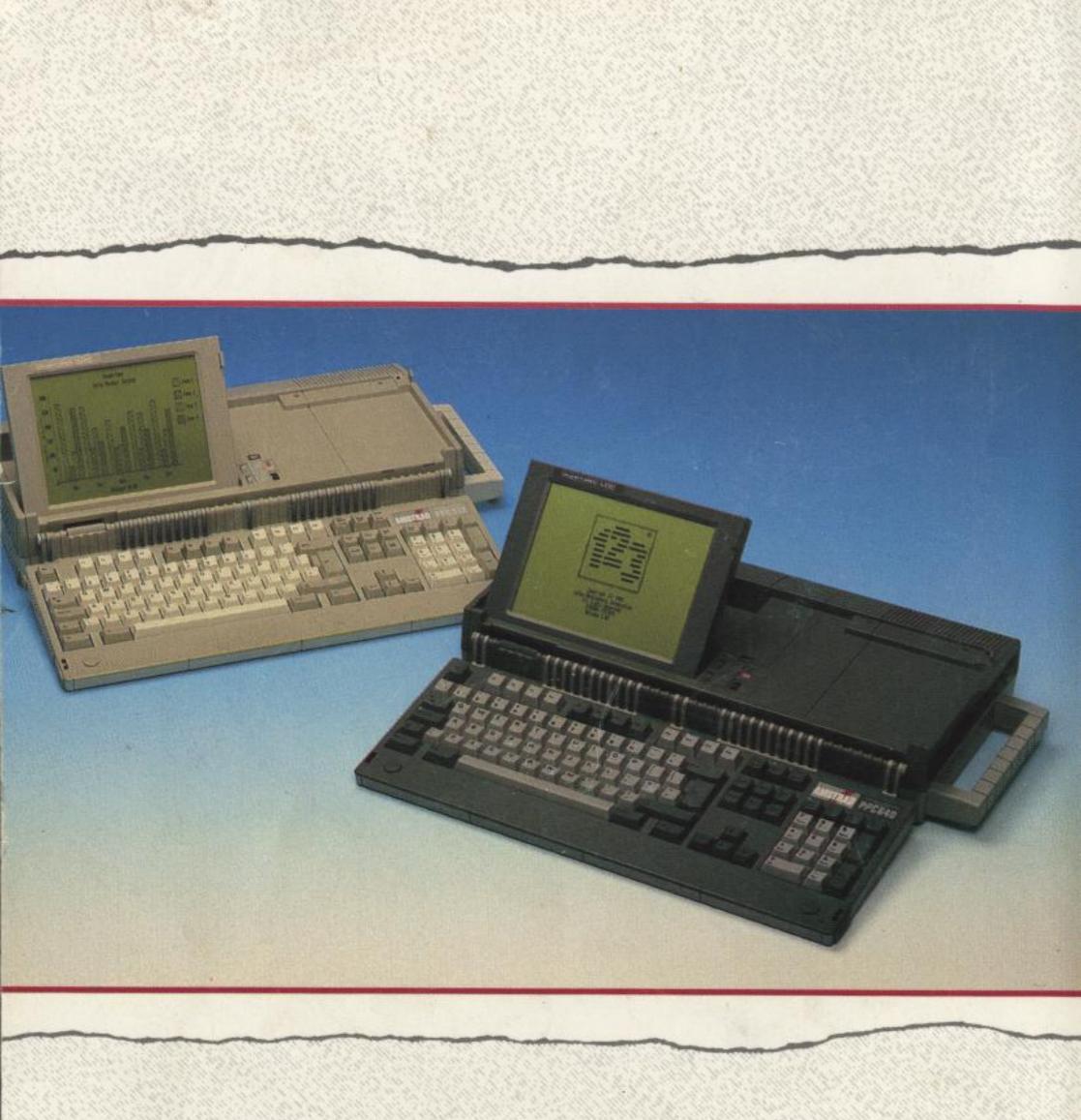

# 1.0 Introduction

This manual provides a comprehensive description of the Amstrad PPC hardware and firmware. General information about the PPC and the delivered operating system software is contained in the Amstrad PPC User Instructions. This manual is intended to satisfy the needs of advanced developers who must have access to the various resources available within the PPC640 and PPC512.

Note that all address constants in this document are hexadecimal. In addition hexadecimal quantities are noted with small letter 'h' terminator to denote that they are in hexadecimal form. Address quantities are not usually annotated this way since they are clearly hexadecimal. Values are presented in hexadecimal form when they are logically bit oriented quantities rather than of purely numerical significance.

# 1.1 Central Processing Unit (CPU)

The CPU is a low power 8086-2 microprocessor with 1 Megabyte memory addressing capability (See Figure 1.1), running at a clock frequency of 8MHz. The CPU is connected to an on-board 16-bit system memory bus requiring four 125nS timing cycles (T-States) per access resulting in a 500nS memory cycle for 16-bit memory. The CPU is also connected on an on-board 8 bit I/O and memory peripheral bus with a 4 MHz clock, which in turn connects to an external expansion bus. Operations on the 8-bit bus automatically incur 125nS wait states as follows:

| Operation                    | Wait States | Bus Cycle                   |

|------------------------------|-------------|-----------------------------|

| 8-bit (Memory)               | 4           | 1.0 µS                      |

| 16 to 8-bit convert (Memory) | 12          | 2.0 μS                      |

| 8-bit (I/O)                  | 6           | 1.0 μS<br>2.0 μS<br>1.25 μS |

| 16 to 8-bit convert (I/O)    |             | 2.5 μS                      |

The CPU is configured to run in maximum mode and the instruction set may be optionally extended by the addition of an 8087-2 Numeric Data Coprocessor. The 8087 BUSY output is connected directly to the 8086 NOT TEST input.

# 1.2 Memory Layout

The main board memory consists of 640K bytes of system RAM with parity checking and 16K bytes of system ROM without parity checking.

The 640K byte user RAM starts at CPU memory address 00000 and extends to 9FFFF. Note that the PPC512 has 512K bytes installed memory ending at address 7FFFFh and the address space from 80000h to 9FFFFh may be extended in external 32K byte blocks (up to the 640K maximum).

The 128K byte address space from A0000 to BFFFF is reserved for video regeneration buffers, and is not used by CPU programs. The PPC Internal Display Adapter (IDA) uses the 64K byte address range from B0000 to BFFFF. The segmentation of this memory range is dependent on the display mode (See <u>section 1.11</u>). External display adapters also use this memory address range for their display buffers.

The 192K byte address space from C0000 to EFFFF is reserved for external expansion ROM address space. Hard Disk controllers use the range from C8000 to C9FFF. Additional hard disk controllers may also use the area from CA000 to CD000. The PPC test board uses the ROM area from E0000 to E7FFF.

The 16K byte system ROM is at FC000 to FFFFF and contains the Resident Operating System (ROS) firmware. The 48K byte address range from F0000 to FBFFF is reserved for ROM space expansion. The 16K byte ROS area address bits are partially decoded such that the ROS ROM repeats four times in the F0000 to FFFFF address range.

#### **MEMORY LAYOUT**

| 00000  |       | ON-BOARD                          | 640K Byte          |

|--------|-------|-----------------------------------|--------------------|

|        | 9FFFF | DYNAMIC RAM                       | System Memory      |

|        | A0000 | 128K BYTES                        |                    |

|        | BFFFF | VIDEO DISPLAY BUFFERS             |                    |

| 1MBYTE | C0000 |                                   |                    |

| ADDR   |       | 192K BYTES EXPANSION ROMS         |                    |

| RANGE  | EFFFF |                                   |                    |

|        | F0000 | AND DATES DOS DOM DI OCIS DEDEATS | 0.414 D. 1         |

|        | FBFFF | 48K BYTES ROS ROM BLOCK REPEATS   | 64K Byte           |

|        | FC000 | 16K BYTES (ROS)                   | System ROM<br>area |

| ı      |       | RESIDENT OPERATING SYSTEM ROM     | aiea               |

| FFFFF  |       |                                   | •                  |

# 1.3 Main Board I/O Channels

The interfaces on the main board occupy the 8086 I/O addresses as follows:

| ADDRESS(hex) | OUTPUT USE                | INPUT USE                                 |

|--------------|---------------------------|-------------------------------------------|

| 000 - 00F    | 8237 DMA Controller       | 8237 DMA Controller                       |

| 010 - 01F    | Do Not Use                | Do Not Use                                |

| 020 - 021    | 8259 Interrupt control    | 8259 Interrupt control                    |

| 022 - 03F    | Do Not Use                | Do Not Use                                |

| 040 - 042    | 8253 PIT Load Count (0-2) | 8253 PIT Read Count (0-2)                 |

| 043          | 8253 PIT Load Mode        | Undefined                                 |

| 044 - 05F    | Do Not Use                | Do Not Use                                |

| 060          | No Effect                 | Port A - Keyboard Code or System Status 1 |

| 061          | Port B - System Control   | Port B - (Readback)                       |

| 062          | No Effect                 | Port C - System Status-2                  |

| 063          | No Effect                 | Do Not Use                                |

| 064          | Write System Status-1     | Do Not Use                                |

| 065          | Write System Status-2     | Do Not Use                                |

| 066          | System Reset              | Do Not Use                                |

| 067 - 06F    | Do Not Use                | Do Not Use                                |

| 070          | 146818 RTC Address        | Do Not Use                                |

| 071          | 146818 RTC Data           | 146818 RTC Data                           |

| 072 - 077    | Do Not Use                | Do Not Use                                |

| 078          | Reserved                  | Reserved                                  |

| ADDRESS(hex)     | OUTPUT USE                          | INPUTUSE                      |

|------------------|-------------------------------------|-------------------------------|

| 079              | Do Not Use                          | Do Not Use                    |

| 079<br>07A       | Reserved                            | Reserved                      |

| 07B - 07F        | Do Not Use                          | Do Not Use                    |

| 080              | Do Not Use                          | Do Not Use                    |

| 081              |                                     | Do Not Use                    |

| 082              | 3 3                                 | Do Not Use                    |

|                  |                                     |                               |

| 083<br>084 - 09F | DMA Page Register Ch 0,1 Do Not Use | Do Not Use                    |

|                  |                                     |                               |

| 0A0              | NMI Mask Control                    | Do Not Use                    |

| 0A1 - 0BF        | Do Not Use                          | Do Not Use                    |

| 0C0 - 0FF        | Reserved                            | Reserved                      |

| 2F8 - 2FF        | Modem UART Tx                       | Modem UART Rx<br>Data/Control |

| 270              | Data/Control                        |                               |

| 378              | Printer Data Latch                  | Printer Data Latch            |

| 379              | Do Not Use                          | Printer Status                |

| 37A              | Printer Control Latch               | Printer Control Latch         |

| 37B - 37F        | Do Not Use                          | Do Not Use                    |

| 3B0 - 3B7        | Mono Mode CRTC                      | Mono Mode CRTC                |

|                  | Registers Mono Mode Control         | Registers<br>Mono Mode CRTC   |

| 3B8 - 3BF        | Registers                           | Registers                     |

|                  | Colour Mode CRTC                    | Colour Mode CRTC              |

| 3D0 - 3D7        | Registers                           | Registers                     |

|                  | Colour Mode Control                 | Colour Mode Control           |

| 3D8 - 3DF        | Registers                           | Registers                     |

| 3F0 - 3F1        | Do Not Use                          | Do Not Use                    |

| 3F2              | Drive Selection                     | Do Not Use                    |

| 3F3              | Do Not Use                          | Do Not Use                    |

| 3F4              | Do Not Use                          | 765 FDC Status                |

| 3F5              | 765 FDC Data                        | 765 FDC Data                  |

| 3F6 - 3F7        | Do Not Use                          | Do Not Use                    |

|                  | COM1 8250 UART Tx                   | COM1 8250 UART Rx             |

| 3F8 - 3FF        | Data/Control                        | Data/Control                  |

# 1.4 Expansion Bus I/O Channels

The 8086 CPU I/O addresses on the expansion bus are as follows:

| ADDRESS(hex) | USE                             |

|--------------|---------------------------------|

| 200 - 20F    | External Game Control Interface |

| 210 - 217    | External Bus Expansion Unit     |

| 220 - 24F    | Reserved                        |

| 278 - 27F    | External Printer Port           |

| 2F0 - 2FF    | Reserved                        |

| 300 - 31F    | External Prototyping Card       |

| 320 - 32F    | External Hard Disk Controller   |

| ADDRESS(hex) | USE                                 |

|--------------|-------------------------------------|

| 380 - 38F    | External SDLC Serial RS232C Port    |

| 3A0 - 3AF    | Reserved                            |

| 3B0 - 3BB    | External Monochrome VDU Controller  |

| 3BC - 3BF    | Printer Port                        |

| 3C0 - 3CF    | External Graphics Controller        |

| 3D0 - 3DF    | External Colour/Graphics Controller |

I/O address above 03FFh, if accessed, wrap around and are mapped onto the range 0000h-03FFh.

External cluster controllers at 0790h-0793h, 0B90h-0B93h, 1390h-1393h and 2390h-2393h wrap around to I/O addresses 0390h-0393h respectively.

# 1.5 Direct Memory Access (DMA)

The Amstrad PPC supports four DMA channels on the system board, using an 8237-4 DMA controller and programmable page registers to extend its addressing range from 64k bytes to the full 1M byte processor address range. Each channel is able to transfer data in blocks of up to a maximum of 64K bytes within a page. The DMA channels are for 8-bit data transfers between (8-bit) I/O devices and 8-bit or 16-bit memory.

In peripheral (slave) mode, CPU I/O address lines A0 - A3 are connected conventionally so that 16 command codes appear in the order described in the 8237 data sheets (See <u>section 3.5</u>).

The DMA controller CLK is driven at 4MHz (+/- 0.1%). In master mode during DMA transfers on channels 1,2 and 3, one wait state is added resulting in a five-clock DMA bus cycle of 1.25 $\mu$ S. Channel 0 transfers have a four-clock bus cycle of 1 $\mu$ S.

The DMA channel request signals are as follows:

| DMA Channel | USE                                                                    |

|-------------|------------------------------------------------------------------------|

| 0           | 8253 Timer/Counter OUT1 output - for memory refresh.                   |

| 1           | Spare for use by expansion bus. Used by external SDLC Serial Port.     |

| 2           | 765 Floppy Disk Controller DRQ output. Available on the expansion bus. |

| 3           | Spare for use by expansion bus. Used by external Hard Disk Controller. |

# 1.5.1 DMA Page Registers

DMA channels 1, 2 and 3 can address the entire 1M byte addressing range of the CPU through the use of their associated DMA page registers. There are three DMA registers, one each for channels 1 through 3. Each page register defines for its channel which one of sixteen 64K byte pages in the 1M byte address range DMA transfers are to occur. The page registers are static so that modulo 64K byte addressing occurs at page boundaries.

The DMA page register bit assignments are as follows:

| Bit | Output Use      |  |

|-----|-----------------|--|

| 7-4 | Not Connected   |  |

| 3   | Address bit A19 |  |

| 2   | Address bit A18 |  |

| 1   | Address bit A17 |  |

Bit Output Use 0 Address bit A16

#### 1.5.2 DMA Initialisation

Following a reset, system (ROS) initialisation firmware (in the ROS) sets up the 8237 DMA controller for channel 0 (dynamic refresh) operation as follows:

|                  | 1 1 1 1                  |

|------------------|--------------------------|

| Function         | Initialised State        |

| Word Count       | 64K Transfers            |

|                  | Read                     |

| Mode             | Autoinitialise           |

| Register         | Increment                |

|                  | Single Mode              |

|                  | Disable Memory to Memory |

|                  | Enable Controller        |

| Command          | Normal Timing            |

|                  | Fixed Priority           |

| Register         | Late Write               |

|                  | DREQ Active High         |

|                  | DACK Active Low          |

| Mask<br>Register | Clear Channel 0 Mask Bit |

After power-up or system reset the DMA page registers are undefined and are initialised to zero by the ROS firmware and all 8237 internal locations for channels 1-3 are initialised to a state comparable to the channel zero initialisation above.

Following industry compatibility, memory to memory DMA is not supported on the PPC. It is prohibited due to timing considerations.

# 1.6 System Interrupts

Nine levels of hardware interrupt are provided for in the system by the CPU Non Maskable Interrupt (NMI) and by an 8259A-2 Interrupt Controller. All levels including NMI, are maskable under software control.

CPU I/O address line A0 is connected conventionally so that the command codes appear in the order described in the 8259 data sheets. The SP/EN pin is tied high signifying that the device is to be hardware un-buffered and designated as a master, not a slave.

# 1.6.1 Interrupt Levels

The interrupt levels are assigned as follows:

| Level | Assigned Function                            |  |

|-------|----------------------------------------------|--|

| NMI   | Memory Parity Error and 8087 NDP INT output. |  |

| 0     | 8253 Timer/Counter Out0 output.              |  |

| 1     | Keyboard Scan Code Receiver.                 |  |

| Leve | Assigned Function                                                                               |

|------|-------------------------------------------------------------------------------------------------|

| 2    | 146818 Real Time Clock IRQ output.                                                              |

|      | Available on the expansion bus.                                                                 |

|      | May be used by Enhanced Graphics Adapter                                                        |

| 3    | Used by Modem Serial Port (COM2)                                                                |

|      | and external SDLC Serial Port.                                                                  |

|      | Available on the expansion bus.                                                                 |

| 4    | Primary Serial port (COM1).                                                                     |

|      | Available on the expansion bus.                                                                 |

|      | Used by external SDLC Serial Port.                                                              |

| 5    | Hard Disk Controller. Available on the expansion bus.                                           |

| 6    | 765 Floppy Disk Controller INT output.                                                          |

|      | Available on the expansion bus.                                                                 |

| 7    | Parallel Printer Port.                                                                          |

|      | Available on the expansion bus.                                                                 |

|      | Used by external Printer Port (secondary) and Printer Port (ternary) on external Monochrome VDU |

|      | Controller.                                                                                     |

## 1.6.2 Interrupt Controller Initialisation

Following a reset, the initialisation firmware in the ROS sets the 8259 Interrupt Controller to operate as follows:

8086 system, Single (not cascaded),

Normal fully nested (not special),

Edge-triggered,

Buffered mode - slave,

Normal EOI (not auto),

Fixed priority - level 0 highest, level 7 lowest.

The system (ROS) firmware initialises the 8259 address bits such that IRQ0 through IRQ7 appear in the CPU interrupt vector space at interrupts 8 through 15 respectrively. NMI is configured to CPU interrupt vector 2.

#### 1.6.3 NMI Mask Control

The NMI Mask Control is a write only register at I/O address 0A0h and allows the CPU non-maskable interrupt (NMI) input to be enabled or disabled by software. The Bit assignments are as follows:

| Bit   | Output Use    |

|-------|---------------|

| 7     | Enable NMI.   |

| 6 - 0 | Not Connected |

Following a reset NMI is disabled.

NMI can be connected to the 8087 NDP, the on-board memory parity check circuit, and the expansion bus I/OCHCK (I/O Channel Check).

# 1.7 Programmable Interval Timers

Three programmable timer/counters are provided at I/O Addresses 040 - 043 by an 8253 Programmable

Interval Timer (PIT) device. They are defined as follows:

| Counter | Use                                              |

|---------|--------------------------------------------------|

| 0       | General Purpose Timer.                           |

| 1       | Used by DMA channel 0 (for dynamic ram refresh). |

| 2       | Tone Generation for Speaker.                     |

# 1.7.1 Timer Configuration

The 8253 timers are configured as follows:

| Function          | Configuration                                                                                                                       |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| CLK               | 1.193 MHz +/- 0.1% (54.925493 ms per count)                                                                                         |

| 0,1,2<br>GATE 0,1 | Always 'ON'.                                                                                                                        |

| GATE 2            | Controlled via Port B (System Control Channel) Speaker Modulate output.                                                             |

| OUT 0             | Interrupts on 8259 PIC IR0 input.                                                                                                   |

| OUT 1             | Requests on 8237 DMA DREQ0 input.                                                                                                   |

| 1()ロロン            | Logical 'AND' with Port B (System Control Channel) Speaker Drive output. Also goes to Port C (System Status-2 Channel) as an input. |

#### 1.7.2 Counter 1 initialisation

Following a reset, the system initialisation firmware in the ROS programs the 8253 PIT for counter 1 (dynamic ram refresh) operation as a rate generator producing a signal with a period of 15.13  $\mu$ S. There are no restrictions requiring the initialisation and programming of counters 0 and 2.

# 1.8 System Status and Control

Two system status input channels and four output channels are provided on-board. Ports A, B and C emulate a pre-programmed 8255 PPI device. They are located in the I/O address space in the range 060h - 06Fh. Port B is programmed for control output, Port A is programmed either for Status-1 input or for receiving data from the keyboard, and Port C is programmed for Status-2 input.

Ports A, B and C emulate an 8255 PPI that has been set up as follows:

Group A Mode 0, Group B Mode 0, Port A = input, Port B = output, Port C(U) = input. Port C(L) = input.

Unlike an 8255, power-up and reset do not affect this configuration.

# 1.8.1 Port B - System Control

The System Control channel is located at I/O Address 061h. Its bit assignment is as follows:

| Bit (PBn) | Output Use                                      |

|-----------|-------------------------------------------------|

| 7         | Enable Status-1/Disable Keyboard Code on Port A |

| 6         | Enable incoming Keyboard Clock.                 |

| Bit (PBn) | Output Use                                       |

|-----------|--------------------------------------------------|

| 5         | Prevent external parity errors from causing NMl. |

|           | (Also Disable any pending NMI).                  |

| 4         | Disable parity checking of on-board system Ram.  |

| 3         | Undefined (Not Connected).                       |

| 2         | Enable Port C LSB / Disable MSB. (See 1.8.3)     |

| 1         | Speaker Drive.                                   |

| 0         | 8253 GATE 2 (Speaker Modulate).                  |

When bit 7 is set high, Status-1 data is enabled on Port A, the keyboard data path and keyboard interrupts are disabled. When bit 7 is set low, keyboard input data is enabled on port A, the keyboard data path and keyboard interrupts are enabled. Applications software which sets PB7 must restore it to the cleared state else the keyboard may be rendered inoperable.

The keyboard interface operates as follows: Each incoming keycode is latched on-board, causing a keyboard interrupt (on level 1). While the interrupt remains pending, the incoming keyboard data signal is forced low as an acknowledgement to the keyboard that the keycode has been received. As soon as the interrupt has been cleared, the keyboard may use the Data signal to transmit the next keycode.

PB5 when set prevents an external parity error (ie. an I/OCHCK condition on the expansion bus) from causing NMI, even if NMI is unmasked. When NMI has been triggered and latched it may be cleared by pulsing PB5 (if the external device has removed its I/OCHCK signal).

PB2 when set enables the reading of the four LS bits of the RAM fitted indicator on Port C. When PB2 is clear the top (MS) bit of the RAM fitted indicator is read (see 1.8.3).

PB1 may be toggled to drive the speaker with a corresponding pulse train. The speaker may also be driven by a wave form from the 8253 PIT OUT2 output (simultaneously with PB1).

PB0 may be toggled to drive the 8253 gate input, hence modulate counter 2 operations and therefore driving the speaker which may all be performed simultaneously to create various audio effects.

# 1.8.2 Port A - Status-1 Input/Keyboard Code

Port A is a read only location located at I/O Address 060h. The bit assignments for Port A are as follows:

| Bit (PAn) | Status-1                            | Keyboard Input |

|-----------|-------------------------------------|----------------|

| 7         | Always 0.                           | KBD7           |

| 6         | Second Floppy disk drive installed. | KBD6           |

| 5         | DDM1 - Default Display Mode bit 1.  | KBD5           |

| 4         | DDM0 - Default Display Mode bit 0.  | KBD4           |

| 3         | Always 1.                           | KBD3           |

| 2         | Always 1.                           | KBD2           |

| 1         | 8087 NDP installed.                 | KBD1           |

| 0         | Always 1.                           | KBD0           |

When Port B, Bit 7 (PB7) is set to high, reading Port A loads Status-1. When PB7 is set low, reading Port A loads keyboard data.

The Default Display Mode bits (DDM1, DDM0) are set up by the ROS during system initialisation as follows:

| DDM1 | DDM0 | Default Display Mode Selected                                                                         |  |

|------|------|-------------------------------------------------------------------------------------------------------|--|

| 0    | 0    | External Extended Graphics Adapter Installed                                                          |  |

| 0    | 1 1  | Colour Graphics Adapter Emulation (or external CGA) with alpha, 40 X 25 chars, bright white on black. |  |

| 1    | 1()  | Colour Graphics Adapter Emulation (or external CGA) with alpha, 80 X 25 chars, bright white on black. |  |

| 1    | 1    | Monochrome Display Adapter Emulation (or external MDA) with alpha, 80 X 25 chars.                     |  |

When the Internal Display Adapter (IDA) is enabled then switches 1 - 3 determine the IDA configuration and switches 4 & 5 determine the default display mode. See section 1.22 for these details.

Following a reset, the ROS then sets the initial video state is based on the DDM value. <u>Section 2.3.7</u> gives additional details of the ROS Video Mode settings.

# 1.8.3 Port C - Status-2 Input

Port C is a read only location located at I/O Address 062h. Its bit assignments are as follows:

| Bit (PCn) | Input Use                                           |           |

|-----------|-----------------------------------------------------|-----------|

| 7         | On-board system RAM parity error.                   |           |

| 6         | External parity error (I/OCHCK from expansion bus). |           |

| 5         | 8253 PIT OUT2 output.                               |           |

| 4         | Undefined.                                          |           |

|           | LSB or MSB (depends on PB2)                         |           |

| 3         | RAM3                                                | Undefined |

| 2         | RAM2                                                | Undefined |

| 1         | RAM1                                                | Undefined |

| 0         | RAM0                                                | RAM4      |

PC7 is forced to the zero state when on-board system RAM parity checking is disabled by PB4.

When the I/OCHCK condition (external parity error) from the expansion bus is disabled from causing NMI (by PB5 set high), PC6 reflects the state of the I/OCHCK input else it reflects the latched state of I/OCHCK.

The value of RAM4-RAM0 denotes the amount of system RAM fitted to the system as follows:

| RAM4 | RAM3 | RAM2 | RAM1 | RAM0 |             |

|------|------|------|------|------|-------------|

| 0    | 1    | 1    | 1    | 0    | 512K bytes. |

| 0    | 1    | 1    | 1    | 1    | 544K bytes. |

| 1    | 0    | 0    | 0    | 0    | 576K bytes. |

| 1    | 0    | 0    | 0    | 1    | 608K bytes. |

| 1    | 0    | 0    | 1    | 0    | 640K bytes. |

See <u>section 1.8.1</u> for the Control Port B setting for reading RAM fitted segment bits.

# 1.8.4 Write System Status-1

The Write System Status-1 register (WSS1) is a write only register at I/O Address 064h and is initialised by the Resident Operating System (ROS) firmware based on values obtained from configuration switches 4 and 5. It is used in conjunction with the 8255 PPI Port Aemulation. The bit assignments are as follows:

| Bit    | Output Use                                |

|--------|-------------------------------------------|

| 7      | No effect.                                |

|        | PA6 - Second Floppy disk drive installed. |

| 5<br>4 | PA5 - DDM1.                               |

| 4      | PA4 - DDM0.                               |

| 3      | No effect.                                |

|        | No effect.                                |

| 1      | PA1 - 8087 NDP installed.                 |

| 0      | No effect.                                |

# 1.8.5 Write System Status-2

The Write System Status-2 register is a write only register at I/O Address 065h and is initialised by the Resident Operating System (ROS) firmware based on the memory size check performed during Power On Self Test. It is used in conjunction with the 8255 PPI Port C emulation. The bit assignments are as follows:

| Bit | Output Use             |

|-----|------------------------|

|     | PC2 (MSB) - Undefined. |

|     | PC1 (MSB) - Undefined. |

| 5   | PC0 (MSB) - Undefined. |

| 4   | PC3 (MSB) - RAM4.      |

| 3   | PC3 (LSB) - RAM3.      |

| 2   | PC2 (LSB) - RAM2.      |

| 1   | PC1 (LSB) - RAM1.      |

| 0   | PC0 (LSB) - RAM0.      |

# 1.8.6 System Reset

Any write access to I/O Address 066h regardless of the value written will cause the hardware to generate an immediate 512µS system reset and pulse the reset line on the expansion bus. The contents of the onboard system RAM is preserved following a system reset.

# 1.9 Real Time Clock

A HD146818 Real Time Clock plus RAM device is installed and backed up by the battery pack. The clock device provides a time of day clock with alarm, a one hundred year calendar, a programmable periodic interrupt, and 50 bytes of static RAM. The static RAM is called the Non-Volatile RAM (NVR) and is used to store time of last usage. The ROS firmware maintains a checksum of the NVR and will reset the RTC to default configuration during startup whenever the checksum value is incorrect.

When system power is off and the 146818 is on battery backup power, the functions which remain active are the clock and the retention of RAM data.

The input crystal oscillator runs at 32.768 KHz and the 146818 interrupt request is connected to the 8259 system interrupt controller on level 2 (which is also available on the expansion bus). The 146818 power-sense input PS is connected to a battery condition sensor. When the backup battery voltage is sufficiently low, the VRT bit in register D becomes set indicating that the time, the calendar and the NVR data are no longer valid. When this condition is noted during startup, the firmware outputs the message "Please fit new batteries" and resets the NVR to default values (See section 2.5).

All the features described in the 146818 data sheet are available with the exceptions that the CKOUT (clock output) and SQW (square wave output) pins are not connected on the main board.

Writing or reading the NVR involves a two step sequence for each byte that is accessed. The RTC Address channel (I/O Address 070) is first loaded with the NVR location to be accessed. Then the RTC Data channel (I/O Address 071) is either written or read to complete the I/O operation. This facility should be used with caution in order to avoid disturbing the system configuration data.

# 1.10 Parallel Printer Port

The printer port provides an interface for driving 8-bit and 7-bit Centronics compatible printers. The timing of the signals to the printer is under direct software control. There is a read/write control latch for sending control signals to the printer, an unlatched read-only printer status channel, and a read/write data latch for sending printer data.

In addition the printer control latch can be read to obtain system type and switch information.

#### 1.10.1 Printer Data Latch

The printer data latch is a read/write record at I/O address 378 and its layout is as follows:

| Bit (Dn) | Output/Input Use | Cable Polarity |

|----------|------------------|----------------|

| 7        | Data 7           | Hi             |

| 6        | Data 6           | Hi             |

| 5        | Data 5           | Hi             |

| 4        | Data 4           | Hi             |

| 3<br>2   | Data 3           | Hi             |

| 2        | Data 2           | Hi             |

| 1        | Data 1           | Hi             |

| 0        | Data 0           | Hi             |

The contents of the data latch are undefined following a power-up or system reset.

#### 1.10.2 Printer Control Latch

The printer control latch is a read/write record at I/O address 37A and its layout is as follows:

| Bit | Output/Input Use         | Reset State | Cable Polarity |

|-----|--------------------------|-------------|----------------|

| 7   | PPC SW 4 (inverted) [RO] |             |                |

| 6   | PPC SW 5 (inverted) [RO] |             |                |

| 5   | FDC Change Line [RO]     |             |                |

| 4   | Enable Int on ACK        | False       |                |

| 3   | Select Printer           | False       | Low            |

| 2   | Not Reset Printer        | True        | Low            |

| 1   | Select Auto Feed         | False       | Low            |

| 0   | Data Strobe              | False       | Low            |

Bit 7 is a read-only bit which reflects the state of switch 4 (at the side of the machine) and returns a logic "0" when the switch is in the "on" position and a logic "1" for the "off" position.

Bit 6 is a read-only bit which reflects the state of switch 5 and returns a logic "0" when the switch is in the "on" position and a logic "1" for the "off" position.

Bit 5 is diskette change line status and is true (logic "1") when the selected floppy disk's door is open or no diskette is installed. This signal is latched on the drive and remains true until the disk drive is selected and it receives a step pulse from the FDC. This bit is only valid when a floppy drive is active and selected.

When Interrupt on ACK is enabled an incoming Printer Acknowledge condition will cause a system interrupt on level 7 (which is also available on the expansion bus).

If the printer control lines normally driven via latched bits D0 - D3 are driven externally, the data read on input to this channel will be the logical OR of the latched bits and the externally driven bits, e.g. If a data bit is false and the corresponding cable bit is driven true by the external driver, the bit input will be true.

Following power-up or system reset, the control latch contents assume reset conditions as shown.

Note that this is a general purpose printer interface and that not all printers require all the control signals, hence the provision for non-standard printers to be able to drive some of the control signals as inputs to the main board. The timing requirements on Centronics compatible printers generally specify that data must be present at  $1\mu$ S before the strobe is made active, and must remain valid for at least  $1\mu$ S after strobe goes inactive. The strobe duration must be between  $1\mu$ S and  $500~\mu$ S. Printer Busy status can be inspected as soon as the strobe is inactive in order to determine when more data can be sent.

#### 1.10.3 Printer Status Channel

The Printer Status Channel is a read only register at I/O Address 0379h. Its layout is as follows:

| Bit | Input Use            | Cable Polarity |

|-----|----------------------|----------------|

| 7   | -Printer Busy        | High           |

| 6   | -Printer Acknowledge | Low            |

| 5   | Paper Out            | High           |

| 4   | Printer Selected     | High           |

| 3   | -Printer Error       | Low            |

| 2   | -LK3 fitted          |                |

| 1   | -LK2 fitted          |                |

| 0   | -LK1 fitted          |                |

LK1 - LK3 are general purpose factory installed option links on the main board which are used by the system ROM Operating System (ROS) firmware to distinguish national variant machine configurations. The ROS will produce its sign-on message and error messages in one of seven languages. The first seven states (0 - 6) are used for language variants and the eighth (7) state is used extended diagnostic mode testing (See section section 2.2). Since the link state is inverted, the value obtained from the lower three bits of the printer port must be exclusive or'ed (XOR) with 1's to obtain the language number.

| LK1 | LK2 | LK3 | ROS Language |

|-----|-----|-----|--------------|

| OFF | OFF | OFF | English.     |

| OFF | OFF | ON  | German.      |

| OFF | ON  | OFF | French.      |

| OFF | ON  | ON  | Spanish.     |

| ON  | OFF | OFF | Danish.      |

| ON  | OFF | ON  | Swedish.     |

| LK1 | LK2 | LK3 | ROS Language               |

|-----|-----|-----|----------------------------|

| ON  | ON  | OFF | Italian.                   |

| ON  | ON  | ON  | Diagnostic Mode. (English) |

Note that this is a general purpose printer interface and that not all printers implement all the status lines, nor do they all attach the same meanings to the error conditions.

Printer Busy normally indicates that a printer cannot receive data, for example during data entry, printing, when offline, or during a printer error condition.

Printer Acknowledge, if implemented is generally asserted by a printer to indicate that data has been received and the printer is ready to receive the next data. Note that Printer Acknowledge (ACK) can also be set to cause interrupts (See <u>1.10.3</u>).

Section <u>1.14</u> contains the printer connector pin assignments.

# 1.11 The PPC Internal Display Adapter.

The Internal Display Adapter (IDA) is implemented using a gate array and a 6845 CRTC. It provides video for either the internal Liquid Crystal Display (LCD) or video output to a standard (PC1640) video connector at the rear of the PPC. The IDA is completely software compatible with the industry standard MDA & CGA environments and when outputting to an external display (in VDU mode) the video signals and scan frequencies are compatible with industry standard monitors.

The IDA provides either a Colour Graphics Adapter (CGA) emulation mode or a Monochrome Display Adapter (MDA) emulation mode. The video screen memory (or regeneration buffer) starting address is configured to B8000 for CGA emulation mode and to B0000 for MDA emulation mode.

The CGA display mode supports text or graphics in 16 colours on a Colour Display (CD) with a maximum resolution of 640 dots by 200 lines. Since colours cannot be displayed on the internal LCD a pixel will either be ON or OFF depending on whether it is the foreground colour or the background colour.

The MDA display mode supports black and white text in normal, intense, inverse, blink, or underline with a character cell resolution of 8 x 14. There are no graphics modes in MDA emulation mode. When using the internal LCD in MDA emulation mode the software environment is the same as that of a standard MDA device, but the character cell resolution is 8 x 8, intensified or highlighted characters are displayed with the vertical bars of each character one dot thinner than they would otherwise be and underlining is not supported.

In CGA emulation mode, the colour palette consists of sixteen colours as follows:

| Intensity | Red | Green | Blue | Colour  |

|-----------|-----|-------|------|---------|

| 0         | 0   | 0     | 0    | Black   |

| 0         | 0   | 0     | 1    | Blue    |

| 0         | 0   | 1     | 0    | Green   |

| 0         | 0   | 1     | 1    | Cyan    |

| 0         | 1   | 0     | 0    | Red     |

| 0         | 1   | 0     | 1    | Magenta |

| 0         | 1   | 1     | 0    | Brown   |

| 0         | 1   | 1     | 1    | White   |

| 1         | 0   | 0     | 0    | Grey    |

| Intensity | Red | Green | Blue | Colour        |

|-----------|-----|-------|------|---------------|

| 1         | 0   | 0     | 1    | Light Blue    |

| 1         | 0   | 1     | 0    | Light Green   |

| 1         | 0   | 1     | 1    | Light Cyan    |

| 1         | 1   | 0     | 0    | Light Red     |

| 1         | 1   | 0     | 1    | Light Magenta |

| 1         | 1   | 1     | 0    | Yellow        |

| 1         | 1   | 1     | 1    | Intense White |

# 1.11.1 Colour Alpha Display

In colour mode, two Alpha modes are available: either 40 characters by 25 rows or 80 characters by 25 rows. The display RAM requirement is 2K bytes and 4K bytes of display RAM for 40 and 80 column modes respectively. The display regeneration buffer is from B8000h to BBFFFh for these modes and the ROS bios supports up to 8 or 4 separate display pages for 40 and 80 column modes respectively. This same display mapping is also repeated at BC000h.

The character set is formed by a ROM character generator and each of the 256 characters is made up of a 8 by 8 pixel matrix.

The starting address in the display RAM is programmed via the 6845 CRT (Cathode Ray Tube) Controller (CRTC). The starting address is on an even address boundary and it addresses the first (leftmost) character position in the top row of the display. The CRTC starting address register is a 16-bit register and it specifies the offset in two byte pairs from the display mode origin. This means for each change of one in the CRTC starting address register, the next even address is selected in the display RAM as the current regeneration buffer origin.

In order to display a single character, two bytes of display RAM are required, and for each pair of display RAM bytes, the even address is for the character code and the odd address is for the attribute byte. Subsequent characters are displayed along the row from left to right. When the end of a row is reached the next pair in the display RAM appears in the first character position of the next row down. Appendix 6 gives the 256 character codes and their respective default character representations.

The attribute byte allows a choice of either 16 foreground and 8 background colours per character, plus blinking, or a choice of 16 colours for both foreground and background without blinking.

The attribute byte for each is as follows:

| Bit (ATn) | Definition                                         |

|-----------|----------------------------------------------------|

| 7         | Intensity or Enable Blink (Background)             |

| 6         | Red (Background)                                   |

| 5         | Green (Background)                                 |

| 4         | Blue (Background)                                  |

| 3         | Intensity (Foreground) or Character Map A/B Select |

| 2         | Red (Foreground)                                   |

| 1         | Green (Foreground)                                 |

| 0         | Blue (Foreground)                                  |

Bit 7, the Intensity or Enable Blink Bit, changes function based the Mode Control Register. The Mode Control Register (I/O address 03D8h) bit 5 selects between Intensity or Blink.

When driving the internal LCD display in colour modes, the foreground and background colours are given the weightings such that Intensity = 1, Blue = 2, Red = 4, Green = 8 and compared. If the background has a higher value than the foreground the character is inverted. In addition, if bit 7 of the CGA mode control register (section 1.11.5) is set characters with non-black backgrounds are also inverted. These two inversion processes are cumulative so that characters may be doubly inverted and appear non-inverted. As with MDA characters on the LCD, text with an intensified foreground will have verticals one dot thinner.

## 1.11.2 Colour Graphics Display

CGA emulation mode supports graphics with 200 scan lines with a choice of two horizontal resolutions, either 320 pixels per scan line with four colours per pixel or 640 pixels per scan line with a two colours per pixel.

An additional low resolution mode is also supported with 100 scan lines and a horizontal resolution of 160 pixels per scan line with sixteen colours per pixel.

The regeneration buffer for colour graphics modes starts at B8000 and requires 16K bytes and is repeated at BC000. The ROS supports either 8 or 4 display buffer pages for the 320 or 640 resolution modes respectively.

#### 1.11.2.1 Low Resolution Graphics

Low resolution graphics mode is actually text mode and not a true bit mapped graphics mode in the sense that high and medium resolution graphics are. The CRTC is programmed such that there are 100 lines on the screen and the mode register is set up the same as text mode. There is no support for this mode in the ROS and the CRTC must be initialized as described in section 1.11.5.4.

In Low Resolution Graphics Mode (160x100), each logical pixel is mapped to a block of  $4 \times 2$  physical pixels on the LCD. Each logical pixel also has 4 bits to determine which of the 16 colours it should be displayed in. These 4 bits are mapped directly to both rows of 4 physical pixels representing the logical pixels in question this providing 16 different pixel patterns to represent the 16 colours on the LCD.

The mapping of display ram in this graphics mode is actually an extension of the text mode scheme. The even bytes are all filled with a special graphics character, 0DEh, which contains a vertical bar. The odd bytes are then programmed in two four bit pairs with the leftmost pixel being the four high order bits. Each display line therefore requires 160 bytes and for the full 100 line display 16000 bytes are required.

The mapping of the odd byte(s) of graphics RAM in low resolution mode is as follows:

| RAM Bit:   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|---|---|---|---|---|---|---|---|

| Pixel:     | 0 |   |   |   | 1 |   |   |   |

| Pixel Bit: | 3 | 2 | 1 | 0 | 3 | 2 | 1 | 0 |

#### 1.11.2.2 Medium Resolution Graphics

In Medium Resolution Graphics Mode (320x200), the display memory for one scan line (320 pixels) consists of 80 bytes. Each pixel requires two bits so that four pixels are specified by each byte. The leftmost pixel is contained in the two MS bits of the byte and the two bit pairs for the remaining pixels follow on logically in left to right fashion. The two bit field for each pixel specifies one of four colours in one of three palettes as follows:

| Colour | Palette 0  | Palette 1  | Palette 2  |

|--------|------------|------------|------------|

| 0      | Background | Background | Background |

| 1      | Green      | Cyan       | Cyan       |

| 2      | Red        | Magenta    | Red        |

| 3      | Yellow     | White      | White      |

In Medium Resolution LCD mode, each logical pixel is mapped to a pair of physical pixels on the LCD rather than a single pixel of a particular colour as described above. Changing palettes will not, therefore, change the display.

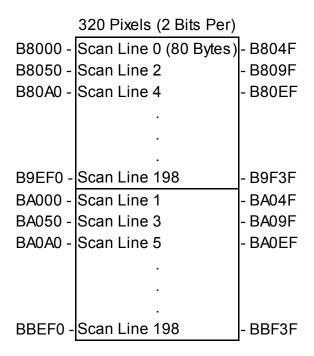

The display regeneration buffer for medium resolution graphics modes is mapped a split buffer configuration with the even scan lines (0, 2, 4, ... 198) contained in the graphics memory space from B8000 to B9F3F and the odd scan lines (1, 3, 5, ... 199) in the memory address range from BA000 to BBF3F. The memory map is as follows:

The layout of a byte of graphics RAM in medium resolution mode is as follows:

| RAM Bit:   | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|---|---|---|---|---|---|---|---|

| Pixel:     | 0 |   | 1 |   | 2 |   | 3 |   |

| Pixel Bit: | 1 | 0 | 1 | 0 | 1 | 0 | 1 | 0 |

## 1.11.2.3 High Resolution (640 x 200) Graphics Mode

In High Resolution Graphics Mode, the display memory for one scan line consists of 80 bytes. Each pixel requires one bits so that eight pixels are specified by each byte. The leftmost pixel is contained in the MS bit of the byte and the remaining pixels follow from left to right. In high resolution mode the two colours are either black (pixel bit off) or pixel bit on with video in one of the 16 colours as selected by a foreground palette register.

One byte of graphics RAM in medium resolution graphics is as follows:

PixeI: 01234567

The address mapping of the scan lines in display RAM for high resolution graphics is the split buffer configuration depicted for medium resolution mode. - All (100) even scan lines from B8000 to B9F3F followed by all (100) odd scan lines from BA000 to BBF3F.

# 1.11.3 Monochrome Display

In monochrome mode there is only one Alpha mode available, 80 characters by 25 rows. When driving an external monochrome display, the character output is 8 x 14 pixel characters, whereas on the LCD a 8 x 8 character matrix is used.

The display RAM requirement is 4K bytes of display regeneration buffer area from B0000h to B0FFFh and is repeated in 1000h boundaries up to and including B7000h.

The 6845 CRTC Starting Address is programmed in the same way as in colour modes and the two byte character and attribute pairs are arranged in the display RAM just as in the colour modes. The attribute byte, however assumes different functions from the colour attributes since there are no IRGB signals sent to the monitor, but Video and Intensity are produced. The monochrome attribute byte is as follows:

| Function   | Bits | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|------|-----|---|---|---|---|---|---|---|

| Blanked    | Bkg  | I/B | 0 | 0 | 0 | I | 0 | 0 | 0 |

| Underlined | Bkg  | I/B | 0 | 0 | 0 | I | 0 | 0 | 1 |

| Normal     | Bkg  | I/B | 0 | 0 | 0 | I | 1 | 1 | 1 |

| Inverse    | Bkg  | I/B | 1 | 1 | 1 | I | 0 | 0 | 0 |

Bit 7, the Background Intensity / Blink Enable (B/I) Bit, changes function based on the Mode control register. The Mode control Register (I/O address 03B8h) Bit 5 selects between Intensity or Blink Functions.

Bit 3 is the foreground intensity bit and controls the intensity when not in inverse video or blanked. The internal LCD displays higher intensity characters using a hardware algorithm to display the vertical lines one dot thinner than in normal intensity. Also, underlining is not supported on the LCD.

#### 1.11.4 BIOS Modes

The ROS sets up the hardware to support eight different modes for the various displays available on the PPC range. The following table gives the modes supported by the ROS.

| ROS Mode       | 0     | 1     | 2     | 3     | 4     | 5     | 6     | 7     |

|----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Туре           | Text  | Text  | Text  | Text  | Graph | Graph | Graph | Text  |

| Columns        | 40    | 40    | 80    | 80    | 320   | 320   | 640   | 80    |

| Rows           | 25    | 25    | 25    | 25    | 200   | 200   | 200   | 25    |

| Colour(s)      | 16    | 16    | 16    | 16    | 4     | B/W   | 2     | Mono  |

| Char Cell Size | 8x8   | 8x14  |

| Regen Origin   | B8000 | B0000 |

| Regen Size     | 16384 | 16384 | 16384 | 16384 | 16384 | 16384 | 16384 | 4096  |

| Page Size      | 2048  | 2048  | 4096  | 4096  | 16384 | 16384 | 16384 | 4096  |

| Number Pages   | 8     | 8     | 4     | 4     | 2     | 2     | 2     | 1     |

The Regeneration Buffer Origin is stated in hexadecimal notation since it is an address quantity. All other

values are in decimal notation.

The ROS Video I/O supports multiple display pages and can be called to select an alternate page. The default (base page) upon initial mode selection is always zero and it begins at the origin address. The successive pages are located higher by the page size increment in the table. The equation for page origin is: Page Origin = Regen Origin + (Page Number - Page Size). Since the 'Page Size' quantity is a pure binary multiple it becomes a shift factor for the selected page number. Page are numbered from 0 to n-1 where 'n' is the number of pages available.

## 1.11.5 Colour Mode Registers

In colour mode there are seven registers for mode, colour selection, additional control functions.

#### 1.11.5.1 CGA Control Register

The CGA Mode Control Register is a read/write register located at I/O address 3D8h. It is used to control the state of the video circuitry, selecting Alpha or Graphics mode and the various sub options available within Alpha and Graphics modes. On an industry standard CGA this is a write only register.

The layout of the CGA Mode control register is as follows:

| Bit | Output Use                                              |

|-----|---------------------------------------------------------|

| 7   | LCD Inverse                                             |

| 6   | LCD Lo-Res Graphics                                     |

|     | Enable Blinking Chars (disable intensified backgrounds) |

| 4   | Select Graphics Mode 2 (de-select graphics mode 1)      |

| 3   | Enable Video Display                                    |

| 2   | Select Palette 2 (de-select palettes 0,1)               |

| 1   | Select Graphics modes (de-select Alpha modes)           |

| 0   | Select Alpha 80 Char mode (de-select 40 Char mode)      |

Bit 0 is used for controlling 40 or 80 column text selection. When bit 0 is reset to "0" 40 column text is enabled. When bit 0 is set to "1" then 80 column text is enabled. Bit 0 has no effect Graphics modes.

Bit 1 selects between text and graphics modes. When bit 0 is reset to "0" then text mode is selected and when bit 0 is set to "1" then graphics mode is selected.

The Select Palette 2 bit (bit 2) has no effect in Alpha modes or in Graphics mode 2. It is used in conjunction with bit 5 of the VDU colour select register to control graphics mode 1 palette. To select palette 2, bit 5 of the CGA colour select register (below) should be reset and bit 2 of the VDU mode control register should then be set.

When bit 3 is reset to "0" the display is blanked by disabling foreground video. When bit 3 is set to "1" foreground video is enabled.

Bit 4 Selects between high resolution and medium resolution graphics modes. When bit 4 is set to "1" then 640x200 graphics resolution is selected and when bit 4 is reset to "0" then 320x200 graphics resolution is selected. Bit 4 has no effect in Alpha modes.

When bit 5 is set in Alpha modes, the foreground will blink for all displayed characters with attribute bit 7 also set. Bit 5 has no effect in Graphics modes.

Bit 6 provides hardware support for the CGA low resolution 160 x 100 sixteen colour graphics mode. It has no effect in external video mode but in LCD mode it enables each of the 16 colours to be displayed as a unique dot pattern.

Bit 7 adds an extra programmable feature to the interpretation of CGA text attributes when displayed on the LCD. When bit 7 is set to "1" in text mode, characters with non-black backgrounds will be displayed in inverse video. This inversion process is in addition to the non-programmable inversion which takes place place when the background colour is greater than the foreground. A character which is inverted by both of these processes will appear non-inverted. This inversion process effects the entire text screen on a character by character basis. This bit has no effect when driving an external CD display.

To avoid unsightly effects on the screen, this register should be updated during frame flyback time. Any kind of mode changing should preferably be done with video disabled. Mode changing involves the use of bits 1 and 0 and usually some re-programming of the CRTC.

#### 1.11.5.2 CGA Colour Select Register

The CGA Colour Select Register is a write only register located at I/O address 03D9h and is used for controlling border colour in alpha modes and for selecting palette, border and pixel colour options in the graphics modes. The layout of the CGA Colour select register is as follows:

| Bit | Alpha Modes        | Graphics Mode 1                            | Graphics Mode 2   |

|-----|--------------------|--------------------------------------------|-------------------|

| 7,6 | No Effect          | No Effect                                  | No effect         |

| 5   | No Effect          | Select Palette 1 (Deselect palette 0)      | No effect         |

| 4   | No Effect          | Foreground Intensity for palettes 0, 1 & 2 | No effect         |

| 3   | Intensity (Border) | Intensity (Backgnd and Border)             | Intensity (Pixel) |

| 2   | Red (Border)       | Red (Background and Border)                | Red (Pixel)       |

| 1   | Green (Border)     | Green (Background and Border)              | Green (Pixel)     |

| 0   | Blue (Border)      | Blue (Background and Border)               | Blue (Pixel)      |

In 640 x 200 two-colour graphics mode the overall screen palette is controlled by setting the CGA Colour Select register (which is initialized to 07h by the ROS on selection of mode 6). This means that the colour resolution is really one of 16 colours for foreground on a black background. Most applications software however control 640 x 200 mode graphics as black and white graphics.

To avoid unsightly effects on the screen this register should only be updated during frame flyback time.

#### 1.11.5.3 CGA Status Register

The CGA Status Register is a read only register located at I/O address 03DA. It may be read at any time to determine the following:

| Bit   | Input Use                   |

|-------|-----------------------------|

| 7 - 4 | Not used (always reset).    |

| 3     | Frame Flyback (VSYNC) Time. |

| 2     | Light-pen switch made.      |

| 1     | Light-pen latch set.        |

| 0     | Display Enabled.            |

Frame flyback time starts at the same time as the bottom border and lasts for 46 horizontal scan periods,

ending 16 scans before the end of the subsequent top border.

Bit 2 reflects the state of the light-pen push button switch. Bit 2 = "1" when the light-pen switch is closed and bit 2 = "0" when the light-pen switch is open.

When bit 1 is set, it indicates that the light pen latch is set, triggered either by a pulse from the light pen or by writing data to set the light pen channel. Writing any data to the Clear Light Pen channel clears the latch.

Bit 0 = zero when the Video signal is enabled and bit 0 = "1" when either the vertical or horizontal retrace signals are active. This is a real time indication of the raster scan line status.

#### 1.11.5.4 CGA Mode CRTC initialization.

The 6845 CRTC is controlled by way of two I/O addresses, the CRTC Address register and the CRTC Data I/O location. The CRTC Address register is a write only register located at I/O address 3D4 and the lower 5 bits are used select the data register at I/O address 3D5. Addresses greater than 17 (11h) produce no results. Note that this set of I/O addresses is partially decoded such that all even I/O addresses between 3D0 - 3D6 access the CRTC index register and all odd I/O address between 3D1 - 3D7 access the selected CRTC data register.

The PPC gate array implementation incorporates a special "Auto-Switch" feature which enables the LCD to appear as a standard display device despite the fact that non-standard CRTC settings are required when dealing with the LCD. The auto-switch prevents CRTC registers 0 - 11 from being altered when bit 6 of the operation control port is set. Any attempt to write to these registers are trapped and PPC unique readback ports are provided so that the ROS's NMI service routine can readback the values written to these registers. Any write access to either the prohibited CRTC registers, the Operation Control port or the CGA control port will trigger a Non-Maskable Interrupt (NMI) when bit 7 of the Operation Control port is set. Bits 5-7 of the CRTC Index readback register can then be read by the NMI service routine to determine which of the three events triggered the NMI. In this way the NMI service routine is alerted to any attempted mode change and can change modes itself by loading the CRTC registers with the appropriate values for the operation in the desired LCD mode. The auto-switch also prevents accidental (non-ROS) changes to bits 6 and 7 of the CGA Control port.

The CRTC registers must be programmed according to the mode of operation required in conjunction with the CGA Mode and Colour Select Registers previously described. A mode changing operation should be performed in the following sequence: Disable video, reprogram the CRTC as required, reprogram the Mode and Colour select registers as required, (maintaining video disabled), initialize display RAM as required, enable video.

The CRTC registers are initialized for LCD CGA mode as follows:

| Register<br>Number<br>(Hex) | Register Name         | Char Mode | Alpha 80<br>Char Mode<br>(Decimal) | Low-res | Graphics<br>High-res<br>(Decimal) |

|-----------------------------|-----------------------|-----------|------------------------------------|---------|-----------------------------------|

| 00                          | Horizontal Total (-1) | 41        | 83                                 | 83      | 43                                |

| 01                          | Horizontal Displayed  | 40        | 80                                 | 80      | 40                                |