## AMSTRAD CPC CRTC COMPENDIUM V1.2

LOGON SYSTEM

This document is licensed under a CC BY-NC-ND 4.0 license Attribution-Non Commercial-NoDerivatives 4.0 International <u>https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode</u>

## TABLE OF CONTENTS

| TA | BLE ( | OF CONTENTS                               | 2  |

|----|-------|-------------------------------------------|----|

| 1  | PRI   | EFACE                                     | 9  |

| 2  | VEI   | RSION HISTORY                             | 10 |

| 3  | GE    | ENERAL                                    | 11 |

|    | 3.1   | TERMINOLOGY                               | 11 |

|    | 3.2   | ACRONYMS                                  | 12 |

| 4  | CR    | RTC & CPC                                 | 13 |

|    | 4.1   | GENERAL                                   | 13 |

|    | 4.2   | CRTC TYPES                                | 15 |

|    | 4.3   | GENERAL VIEW OF THE REGISTERS             |    |

|    | 4.4   | CRTC ACCESS                               | 19 |

|    | 4.4   | 4.1 GENERAL                               | 19 |

|    | 4.4   | 4.2 Z80A INSTRUCTIONS                     | 21 |

|    | 4.4   |                                           |    |

|    | 4.4   | 4.4 OUTs DISSECTION                       | 23 |

| 5  | OT    | THER CIRCUITS                             | 27 |

|    | 5.1   | ACCESS                                    | 27 |

|    | 5.2   | CPC + / GX 4000                           | 28 |

| 6  | BU    | JILDING A SCREEN                          |    |

|    | 6.1   | GENERAL LOGIC                             | 29 |

|    | 6.1   | 1.1 CHARACTER COUNTING                    | 29 |

|    | 6.1   | 1.2 SYNCHRONIZATIONS                      | 29 |

|    | 6.1   | 1.3 CHARACTER DISPLAY                     | 29 |

|    | 6.1   | 1.4 VIDEO POINTER                         | 30 |

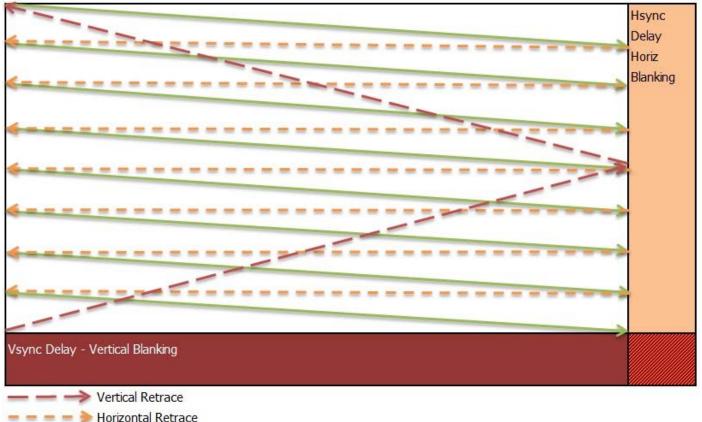

|    | 6.1   | 1.5 DIAGRAMS                              | 30 |

| 7  | SYI   | NCHRONIZATION                             | 33 |

|    | 7.1   | PRINCIPLES                                | 33 |

|    | 7.2   | VSYNC SYNCHRONIZATION                     | 34 |

|    | 7.3   | FAKE VSYNC                                | 37 |

| 8  | DIS   | SPLAY, Z80A & GATE ARRAY                  | 39 |

|    | 8.1   | INSTRUCTION LD(HL),reg8 (2 µsec)          | 39 |

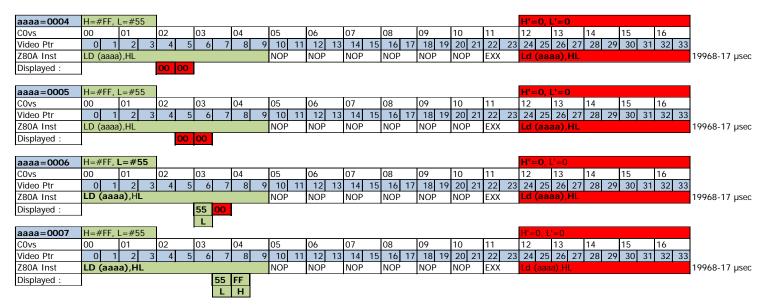

|    | 8.2   | INSTRUCTION LD (aaaa),HL (5 µsec)         | 39 |

|    | 8.3   | INSTRUCTION PUSH reg16 (4 µsec)           | 40 |

| 9  | GA    | ATE ARRAY                                 |    |

|    | 9.1   | PIXELS                                    | 42 |

|    | 9.2   | COLOURS                                   |    |

|    |       | V1.2 – 01.2022 – Page <b>2</b> / <b>2</b> | 26 |

| 9.2.1  | BORDER AND GRAPHIC MODE 2                    | 44 |

|--------|----------------------------------------------|----|

| 9.2.2  | SPEED OF PROCESSING                          | 44 |

| 9.3 GF | RAPHIC MODE                                  | 46 |

| 9.3.1  | GENERAL                                      | 46 |

| 9.3.2  | MODE SPLITTING                               | 48 |

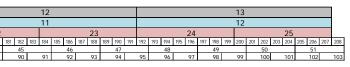

| 10 COU | NTER : REGISTER R9                           | 68 |

| 10.1   | GENERAL                                      | 68 |

| 10.2   | TIME LIMITS                                  | 69 |

| 10.3   | COUNTING RULES                               | 69 |

| 10.3.1 | CRTC 0                                       | 70 |

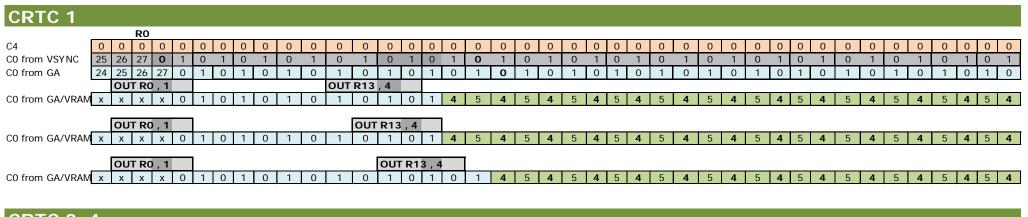

| 10.3.2 | CRTC 1                                       | 71 |

| 10.3.3 | CRTC 2                                       | 71 |

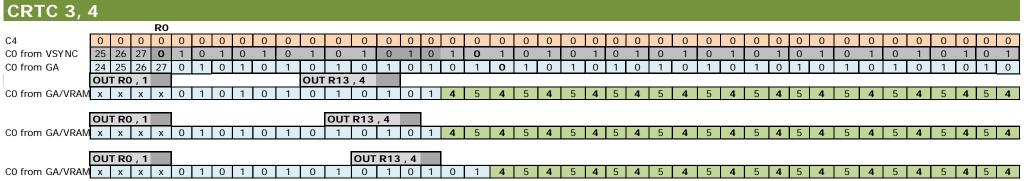

| 10.3.4 | CRTC 3, 4                                    | 72 |

| 11 COU | NTER : REGISTER R5                           | 75 |

| 11.1   | GENERAL                                      | 75 |

| 11.2   | COUNTING IN VERTICAL ADJUSTEMENT             | 76 |

| 11.2.1 | GENERAL                                      | 76 |

| 11.2.2 | CRTC 0                                       | 76 |

| 11.2.3 | CRTC 1, 2                                    | 77 |

| 11.2.4 | CRTC 3, 4                                    | 78 |

| 11.3   | UPDATING R5 DURING AN ADJUSTMENT             | 78 |

| 11.4   | CRTC 0 : UNSOLICITED ADJUSTMENT              | 78 |

| 11.5   | RUPTURE FOR DUMMIES (R.F.D.) ON CRTC 1       | 79 |

| 11.5.1 |                                              |    |

| 11.5.2 | IVM ON/OFF                                   | 80 |

| 11.5.3 | R.F.D. IN SUMMARY.                           | 82 |

| 11.5.4 | R.F.D. AND OTHERS CRTC                       | 82 |

| 11.6   | R6 AND VERTICAL ADJUSTMENT                   | 82 |

| 11.7   | INTERLACE ADJUSTMENT                         | 82 |

| 12 COU | NTING : REGISTER R4                          | 84 |

| 12.1   | GENERAL                                      | 84 |

| 12.2   | CRTC 0                                       | 84 |

| 12.2.1 | CASE STUDY : LINE-TO-LINE RUPTURE (R.L.A.L.) | 85 |

| 12.3   | CRTC 1                                       | 86 |

| 12.4   | CRTC 2                                       | 86 |

| 12.4.1 | CASE STUDY: LINE-TO-LINE RUPTURE (R.L.A.L.)  | 87 |

| 12.5   | CRTC 3, 4                                    | 90 |

| 13 COU | NTING : REGISTER RO                          | 91 |

|        |                                              |    |

| 13.1  | GE          | NERAL                                             | . 91 |

|-------|-------------|---------------------------------------------------|------|

| 13.2  | CR          | TC 0                                              | . 92 |

| 13.2  | 2.1         | CASE STUDY: R0=1                                  | . 95 |

| 13.2  | 2.2         | CASE STUDY: R0=0                                  | . 96 |

| 13.2  | 2.3         | CASE STUDY: VERTICAL RUPTURE LAST LINE (R.V.L.L.) | . 97 |

| 13.3  | CR          | TC 1                                              | . 99 |

| 13.3  | 3.1         | CASE STUDY : VERTICAL INVISIBLE RUPTURE (R.V.I.)  | 100  |

| 13.4  | CR          | TC 2                                              | 104  |

| 13.4  | l.1         | CASE STUDY: VERTICAL RUPTURE LAST LINE (R.V.L.L.) | 105  |

| 13.5  | CR          | TC 3, 4                                           | 106  |

| 13.6  | R0          | UPDATE                                            | 107  |

| 13.6  | 5.1         | DELAYS                                            | 107  |

| 13.6  | <b>b</b> .2 | EXCEPTIONS                                        | 109  |

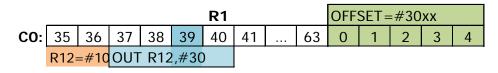

| 13.7  | OF          | FSET ACCORDING TO CO                              | 110  |

| 13.7  | 7.1         | 4 µsec SCREENS (R0=3)                             | 111  |

| 13.7  | 7.2         | 2 µsec SCREENS (R0=1)                             | 112  |

| 13.7  | 7.3         | 1 µsec SCREENS (R0=0)                             | 113  |

| 14 SY | 'NCH        | RONISATION : REGISTER R3                          | 114  |

| 14.1  | GE          | NERAL                                             | 114  |

| 14.2  | VS          | YNC LENGTH                                        | 115  |

| 14.3  | HS          | YNC GATE ARRAY VERSUS CRTC                        | 115  |

| 14.4  |             | YNC AND SCREEN POSITION                           |      |

| 14.5  | HS          | YNC AND INTERRUPTIONS                             | 116  |

| 14.6  | UP          | DATING R3 DURING HSYNC                            | 116  |

| 14.6  | 5.1         | CRTC 0, 2                                         | 117  |

| 14.6  | b.2         | CRTC 1                                            | 118  |

| 14.6  | 5.3         | CRTC 3, 4                                         | 119  |

| 14.6  | <b>b</b> .4 | ZOOM ON R3.JIT                                    | 119  |

| 14.7  | AB          | SENCE OF HSYNC                                    | 123  |

| 14.8  | HS          | YNC START-UP                                      | 123  |

| 14.8  | 3.1         | CRTC 0, 1, 2                                      | 123  |

| 14.8  | 3.2         | CRTC 3, 4                                         | 124  |

| 15 SY | 'NCH        | RONIZATION : REGISTER R7                          | 126  |

| 15.1  | GE          | NERAL                                             | 126  |

| 15.2  | CO          | NDITIONS TO CONSIDER                              | 127  |

| 15.2  | 2.1         | CRTC 0                                            | 127  |

| 15.2  | 2.2         | CRTC 1                                            | 128  |

| 15.2  | 2.3         | CRTC 2                                            | 128  |

|       |             | V1.2 – 01.2022 – Page 4 / 2                       | 226  |

| 15.2.4   | CRTC 3, 4                                  | 129 |

|----------|--------------------------------------------|-----|

| 15.3 L   | IMITLESS VSYNC !                           | 130 |

| 15.4 T   | HE RIGHT MOMENT                            | 132 |

| 16 SYNC  | HRONIZATION : REGISTER R2                  | 133 |

| 16.1 G   | ENERAL                                     | 133 |

| 16.2 H   | SYNC WHEN R2 IS PREDEFINED                 | 135 |

| 16.3 U   | PDATING R2 DURING HSYNC                    | 136 |

| 16.4 V   | SYNC CONSIDERATION DURING HSYNC            | 140 |

| 16.4.1   | GENERAL                                    | 140 |

| 16.4.2   | CRTC 0, 1                                  | 140 |

| 16.4.3   | CRTC 3, 4                                  | 141 |

| 16.4.4   | CRTC 2                                     | 141 |

| 16.5 B   | ORDER AND HSYNC                            | 143 |

| 16.5.1   | CRTC 0, 1, 3, 4                            | 143 |

| 16.5.2   | CRTC 2                                     | 143 |

| 16.6 T   | HE RIGHT MOMENT                            | 143 |

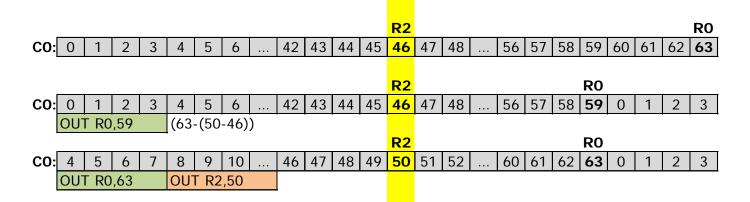

| 16.6.1   | Go from R2=46 to R2=50 on 64 µsec lines.   | 144 |

| 16.6.2   | GO from R2=50 to R2=46 on lines of 64 µsec | 144 |

| 17 DISPL | AY : REGISTER R1                           | 145 |

| 17.1 G   | ENERAL                                     | 145 |

| 17.2 D   | ISPLAYS ACCORDING TO R1                    | 147 |

| 17.2.1   | DISPLAY WITH R1 <= R0                      | 147 |

| 17.2.2   | DISPLAY WITH R1 > R0                       | 148 |

| 17.3 D   | YNAMIC R1 UPDATE                           | 149 |

| 17.4 V   | MA'/VMA WHEN C4=0                          | 152 |

| 17.4.1   | CRTC 0, 3, 4                               | 152 |

| 17.4.2   | CRTC 1                                     | 152 |

| 17.4.3   | CRTC 2                                     | 153 |

| 17.5 A   | CKNOWLEDGMENT R1=0                         | 154 |

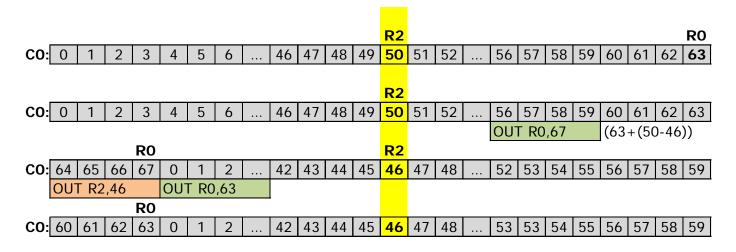

| 17.5.1   | CRTC 0, 1, 2                               | 154 |

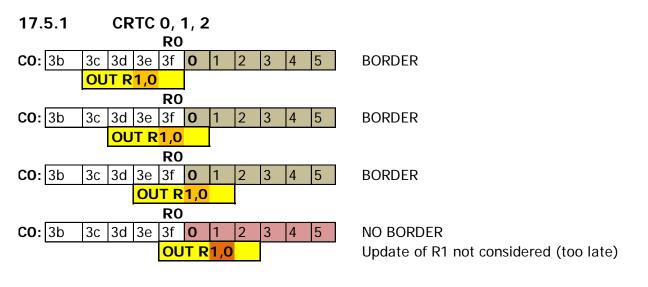

| 17.5.2   | CRTC 3, 4                                  | 154 |

| 17.6 II  | NTERLINE BORDER                            | 155 |

| 17.6.1   | R1=R0 AND C0=R0                            | 155 |

| 17.6.2   | R1>R0 AND C0=R0                            | 155 |

| 18 DISPL | AY : REGISTER R6                           | 157 |

| 18.1 G   | ENERAL                                     | 157 |

| 18.2 B   | ORDER R6 DEADLINES AND PRIORITIES          | 157 |

| 18.2.1   | GENERAL                                    | 157 |

|          | V1.2 – 01.2022 – Page 5 /                  | 226 |

| 18.2.2               | CRTC 0, 2                              | 157         |

|----------------------|----------------------------------------|-------------|

| 18.2.3               | CRTC 1                                 | 158         |

| 18.2.4               | CRTC 3, 4                              | 158         |

| 18.3 R6              | CONFLICTS                              | 158         |

| 18.3.1               | GENERAL                                | 158         |

| 18.3.2               | CRTC 0, 2                              | 159         |

| 18.3.3               | CRTC 1                                 | 160         |

| 18.3.4               | CRTC 3, 4                              | 160         |

| 19 DISPLA            | Y : REGISTER R8                        | 161         |

| 19.1 GE              | NERAL                                  | 161         |

| 19.2 FU              | NCTIONS « SKEW-DISPTMG »               | 162         |

| 19.2.1               | BORDER ON                              | 162         |

| 19.2.2               | BORDER OFF                             | 162         |

| 19.2.3               | BORDER DELAY +1 / +2                   | 162         |

| 19.2.4               | NO CONDITION CO=R1                     | 163         |

| 19.2.5               | DISINTEGRATION OF THE BORDER ON CRTC 0 | 165         |

| 19.3 IN <sup>-</sup> | TERLACE FUNCTIONS                      | 167         |

| 19.3.1               | GENERAL                                | 167         |

| 19.3.2               | THE TWO INTERLACE MODES                | 168         |

| 19.3.3               | LIMITATIONS                            | 170         |

| 19.3.4               | UNLOVED FEATURE                        | 170         |

| 19.4 VE              | RTICAL INTERLACE PROGRAMMING           | 171         |

| 19.4.1               | CRTC 0                                 | 171         |

| 19.4.2               | CRTC 1                                 | 171         |

| 19.4.3               | CRTC 2                                 | 172         |

| 19.4.4               | CRTC 3 & 4                             | 172         |

| 19.5 PA              | RITY                                   | 172         |

| 19.5.1               | GENERAL                                | 172         |

| 19.5.2               | CRTC 0                                 | 173         |

| 19.5.3               | CRTC 1                                 | 174         |

| 19.5.4               | CRTC 2                                 | 175         |

| 19.5.5               | CRTC 3 & 4                             | 176         |

| 19.6 CO              | UNTING IN INTERLACE VIDEOMODE          | 177         |

| 19.6.1               | CRTC 0                                 | 177         |

| 19.6.2               | CRTC 1                                 | 183         |

| 19.6.3               | CRTC 2                                 | 187         |

| 19.6.4               | CRTC 3, 4                              | 194         |

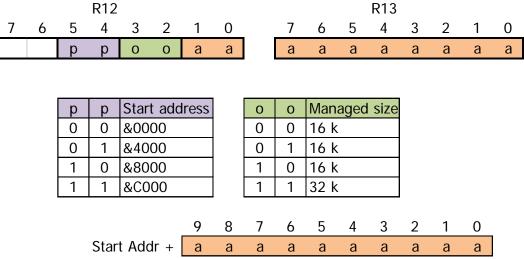

| 20 VIDEO             | POINTER:REGISTERS R12/R13              | 199         |

|                      | V1.2 – 01.2022 – P                     | age 6 / 226 |

| 20.1  | GE    | NERAL                               | 199     |

|-------|-------|-------------------------------------|---------|

| 20.2  | VID   | DEO POINTER CALCULATION             | 199     |

| 20.3  | UPE   | DATE CONDITIONS                     | 200     |

| 20.3  | 3.1   | CRTC 0                              | 200     |

| 20.3  | 3.2   | CRTC 1                              | 200     |

| 20.3  | 3.3   | CRTC 2                              | 201     |

| 20.3  | 3.4   | CRTC 3 & 4                          | 201     |

| 20.4  | Dea   | adlines                             | 201     |

| 20.5  | OVI   | ERSCAN-BITS                         | 202     |

| 21 RI | EAD R | EGISTERS                            | 203     |

| 21.1  | GE    | NERAL                               | 203     |

| 21.2  | RE/   | ADING THE CONTENTS OF THE REGISTERS | 203     |

| 21.2  | 2.1   | CRTC 0                              | 203     |

| 21.2  | 2.2   | CRTC 1, 2                           | 203     |

| 21.2  | 2.3   | CRTC 3, 4                           | 204     |

| 21.3  | REA   | ADING STATUS                        | 204     |

| 21.3  | 3.1   | GENERAL                             | 204     |

| 21.3  | 3.2   | CRTC 0, 2                           | 205     |

| 21.3  | 3.3   | CRTC 1                              | 205     |

| 21.3  | 3.4   | CRTC 3, 4                           | 206     |

| 21.4  | DUI   | MMY REGISTER                        | 207     |

| 22 Fl | JLLSC | REEN & CENTERING                    | 208     |

| 22.1  | For   | eword                               | 208     |

| 22.2  | HO    | RIZONTAL FULLSCREEN                 | 209     |

| 22.3  | VEF   | RTICAL FULLSCREEN                   | 209     |

| 23 TI | PS AN | ND TRICKS                           | 210     |

| 23.1  | R12   | 2/R13 UPDATES                       | 210     |

| 23.2  | COI   | MMON USE OF REGISTER(S)             | 210     |

| 23.3  | WA    | ITING VSYNC                         | 211     |

| 23.4  | ZEF   | RO VALUE                            | 211     |

| 23.5  | OU    | TI/OUTD AND STATUS REGISTER         | 212     |

| 23.6  | COI   | NDITIONAL ITERATIONS AND BRANCHING  | 212     |

| 23.7  | WA    | STING TIME                          | 213     |

| 24 DI | URAT  | ION OF INSTRUCTIONS ON THE CPC      | 214     |

| 25 IN | ITERR | PUPTS                               | 217     |

| 25.1  | GE    | NERAL                               | 217     |

| 25.2  | MA    | NAGEMENT OF R52 COUNTER             | 217     |

| 25.3  | TRI   | GGER CONDITIONS                     | 217     |

|       |       | V1.2 – 01.2022 – Page               | 7 / 226 |

|    | 25.3.7 | 1     | TRIGGER ON R52=0                      | 217 |

|----|--------|-------|---------------------------------------|-----|

|    | 25.3.2 | 2     | TRIGGERING ON VSYNC                   | 218 |

|    | 25.3.3 | 3     | Z80A AND INTERRUPTIONS                | 218 |

| 2  | 5.4    | INTE  | ERRUPT MODE 1                         | 218 |

| 2  | 5.5    | INTE  | ERRUPT MODE 2                         | 219 |

| 2  | 5.6    | CRT   | C & INTERRUPTS                        | 219 |

|    | 25.6.  | 1     | GENERAL                               | 219 |

|    | 25.6.2 | 2     | CRTC 0, 1, 2                          | 220 |

|    | 25.6.3 | 3     | CRTC 0, 1                             | 221 |

|    | 25.6.4 | 4     | CRTC 2                                | 221 |

|    | 25.6.5 | 5     | CRTC 3, 4                             | 221 |

|    | 25.6.6 | 6     | PERSPECTIVE                           | 221 |

| 2  | 5.7    | THR   | EESOME                                | 222 |

| 26 | CRT    | TC ID | PENTIFICATION                         | 223 |

|    | 26.1.2 | 1     | VIA C4 AND/OR C9 OVERFLOW             | 223 |

|    | 26.1.2 | 2     | VIA VSYNC MANAGEMENT DURING HSYNC     | 223 |

|    | 26.1.3 |       | VIA CONSIDERATION OF VSYNC ACTIVATION |     |

|    | 26.1.4 | 4     | VIA VSYNC LENGTH                      | 223 |

|    | 26.1.5 | 5     | VIA HSYNC LENGTH                      | 223 |

|    | 26.1.6 | 6     | VIA THE BORDER, VISUALY               | 224 |

|    | 26.1.7 | 7     | VIA THE INTERLACE MODE                | 224 |

|    | 26.1.8 | 8     | VIA STATUS REGISTER &BE00             | 224 |

|    | 26.1.9 | 9     | VIA READ REGISTER &BF00               | 224 |

|    | 26.1.1 | 10    | VIA R10/R11 STATUS REGISTERS          | 224 |

| 27 | CPC    | : IDE | NTIFICATION                           | 225 |

| 2  | 7.1    | IDE   | NTIFICATION METHODS                   | 225 |

|    | 27.1.1 | 1     | ENABLING EXTENDED FEATURES            | 225 |

|    | 27.1.2 | 2     | BUG PPI PORT C                        | 225 |

|    | 27.1.3 | 3     | BUG PPI PORT B                        | 225 |

# **1 PREFACE**

The objective of this document is to provide detailed information on the operation of the various CRTC 6845 circuits implemented in the CPC's created by AMSTRAD. The CRTC is a controller circuit capable of providing an interface between microcomputers and cathode ray screens that manage video scanning.

The document also discusses the operation of some circuits associated with the CRTC's, especially the GATE ARRAY.

Game or demo programmers still working on these machines designed in the 1980s and the 1990s may find the information presented here useful.

It can also serve as a reference for anyone wishing to create an emulator by adapting code ad hoc for specific programs.

Finally, this document may provide useful information to users of other machines equipped with similar CRTC's. However, it must be noted that the timing between the processor, the CRTC and the associated video circuit of another machine can significantly modify the behaviours described here. Furthermore, the document only describes the CRTC functions used on the CPC; "text" mode and the "cursor" are therefore not discussed here.

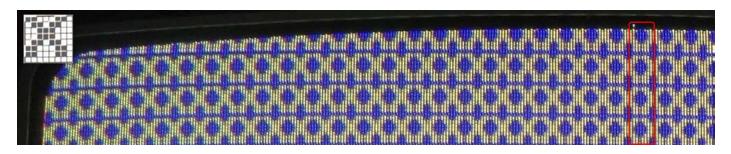

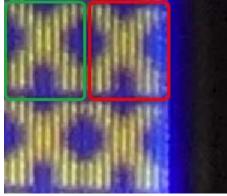

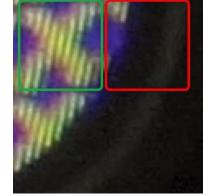

Part of the information presented in this document has been checked using a benchmarking program called SHAKER. It was tested for each CRTC on several machines, and the photos obtained from the results of each test have been compiled into separate documents, one per CRTC.

Truth takes up little space, but error occupies an infinite number of places. This document is subject to revision and change.

Serge Querné Longshot / Logon System serge.querne@logonsystem.fr

Acknowledgements

Arnaud STORQ (*NoRecess*) for his endless patience and his hidden cameraman talents that he put to good use by sending me the results of SHAKER when my CPC's were out of reach.

Claire DUPAS (*Cheshirecat*) for her tests, feedback on HSYNCs and her ideas that are sometimes not so far-fetched ;-)

David MANUEL (*DManu78*), author of the excellent Amspirit emulator, for our discussions and constructive tests to improve this document.

Stéphane SIKORA (*Siko*) for the help provided on some GATE ARRAY tests.

Marc MAC PHAIDIN (*Lmimmfn*), for the English translation of this document.

## **2 VERSION HISTORY**

| Version | Date       | Update                                                                                                                                                                                                                                                                                                                                                    |

|---------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.0     | 01/01/2021 | Document created.<br>Proofreading: Arnaud Storq, Claire Dupas, Sébastien Broudin, Edouard Bergé                                                                                                                                                                                                                                                           |

| 1.1     | 15/12/2021 | Diagrams reimported. Corrections made in §4.3, 4.5, 7.2.<br>Statuses grouped together in § 21 with addition of read registers and definition<br>of CRTC 3 & 4 statuses.<br>CPI/CPD/CPIR/CPDR instruction duration corrected.                                                                                                                              |

| 1.2     | 01/01/2022 | Major update. Precisions, corrections and clarifications on some chapters (especially on CRTC 0: VSync, C9 freeze on R0=0, Interlace Modes).<br>New chapters on the GATE ARRAY (horizontal splitting mode, hsync, interrupts). Description of the RFD. Vertical scroll at 1/64th of a pixel.<br>Proofreading: David Manuel, Claire Dupas, Olivier Antoine |

This document is licensed under a CC BY-NC-ND 4.0 license Attribution-Non Commercial-NoDerivatives 4.0 International

# **3 GENERAL**

### **3.1TERMINOLOGY**

The CRTC is a circuit that spends its time counting and comparing.

It therefore mainly consists of counters, the limit value of which is generally defined in the programmable registers of the circuit.

With the goal of constructing screens made of several vertical characters, in turn made of several vertical lines, which in turn is made of several horizontal characters, certain terms are associated with these registers and counters.

We therefore speak of "*horizontal total number of characters*", "*vertical total number of characters*" and "*Maximum Raster*" to define the value of certain registers, with some differences on occasion depending on the technical documentation under consideration. Some emulators use "unofficial" acronyms to define the names of associated counters: HCC, VTAC, VLC, VCC, ... to name a few.

These terms are no longer appropriate when working at a level other than that intended for the construction of a "standard" screen.

Indeed, at a certain level, the logic of "horizontal" and "vertical" counting practically disappears. It then becomes difficult to speak of "characters" without tripping on one's shoelaces, as depending on the circuit's programming, a vertical character can also be a horizontal character.

This notion exists at most in relation to the synchronization logic of the constructed screen.

Since it is possible to reduce the size of a line to 1  $\mu$ sec, to reduce the size of a vertical character to 1 line and to reduce the size of a screen to 1 character, the horizontal and vertical qualifiers somewhat lose their meaning.

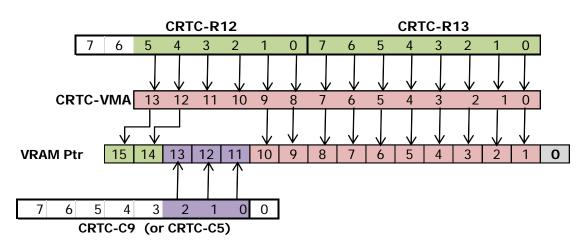

For these reasons, I will generally denote the CRTC registers in this document as **Rn** and the associated counters as **Cn**. "Characters" will denote the words processed by the GATE ARRAY from the address provided by the CRTC. I have named the CRTC's two internal pointers VMA and VMA'.

I invite the authors of emulators based on this document to adopt these notations. Here are equivalents for some of the terms that I have encountered:

| Names identified in certain emulators | Counters                   |  |  |  |  |  |  |

|---------------------------------------|----------------------------|--|--|--|--|--|--|

| HCC (Horizontal Char Counter)         | CO                         |  |  |  |  |  |  |

| VLC (Vertical Line Counter)           | С9                         |  |  |  |  |  |  |

| VCC (Vertical Character Counter)      | C4                         |  |  |  |  |  |  |

| VSC (Vertical Sync Counter)           | C3h                        |  |  |  |  |  |  |

| HSC (Horizontal Sync Counter)         | C3I                        |  |  |  |  |  |  |

| VTAC (Vertical Total Adjust Counter)  | C5 or C9 (on CRTC 0)       |  |  |  |  |  |  |

| VMA (byte pointer)                    | VMA or VMA' (word pointer) |  |  |  |  |  |  |

### 3.2ACRONYMS

**ASIC**: Application Specific Integrated Circuit : Integrated circuit which groups on the same chip all the functions necessary for a specific application. The GATE ARRAY is an ASIC.

**CRTC :** Cathode Ray Tube Controller: Circuit used to interface a computer with a cathode ray monitor capable of handling raster lines.

**HBL**: Horizontal BLank Line: Refers to the period during which the monitor's electron beam, which has reached the right side of the monitor, turns off the beam to return to the left of the screen.

**HSYNC :** Horizontal SYNC: Refers to the signal emitted by the CRTC which allows the monitor (via the GATE ARRAY on CPC) to synchronize the screen horizontally.

**IVM :** Interlace Video Mode.

**IS**: Interlace Sync.

**PIXEL-M2**: Definition of a pixel displayed in graphics mode 2 (0.0625 µsec).

**RFD**: Rupture for Dummies on CRTC 1.

**RLAL**: Rupture Ligne à Ligne (from French). Definition of a rupture where the video address can be updated on each each raster line of the screen.

**RV**: Rupture Verticale (from French): Definition of a rupture whose axis is not "horizontal", and where horizontal zones can be created.

**RVI** : Rupture Verticale Invisible (from French) : Refers to vertical ruptures occurring during the Hsync and not visible.

**RVLL** : Rupture Verticale Last Line (from Frenglish): Refers to vertical ruptures using the C4 « last line » processing on CRTC's 0 and 2.

**VBL**: Vertical BLank Line : Refers to the period during which the monitor electron beam, which has reached the bottom of the screen, deactivates the beam to return to the top of the screen.

**VMA** : Video Memory Address : CRTC pointer to the words addressed in memory and supplied to the GATE ARRAY for display.

**VSYNC :** Vertical SYNC : Signal emitted by the CRTC which allows the monitor (via the GATE ARRAY on CPC) to synchronize the screen vertically.

## 4 CRTC & CPC...

## 4.1GENERAL

On the AMSTRAD CPC, the duration of a CRTC character is 1 µsec..

This CRTC character represents 2 bytes in memory.

The memory pointer is **communicated by the CRTC to the GATE ARRAY**, **which will always read the "central ram" of 64k**. The GATE ARRAY cannot read the data in ROM or in the additional RAM of 6128s (or memory extensions) except for TotOs intervention.

The CRTC is programmed so that the image thus created is supported by a monitor. A language shortcut is to use the term NOP instead of  $\mu$ sec (microsecond) because it is the time taken by this instruction in Z80A on CPC.

On CPC, the Z80A instructions are aligned by rounding the M cycles of an instruction to a multiple of 4 T cycles. This alignment is linked to the need for the GATE ARRAY to interrupt the Z80A to access the ram whose address is provided by the CRTC. This operation slows down some instructions relative to the clock frequency. Achieving accurate code requires knowing the exact time taken by each instruction. See Chapter 24, page 214, for details of these durations for each instruction.

#### A bit of history

Old Cathode ray monitors and televisions lined up their display frequency with the electricity distribution network of the country of marketing.

In Europe in particular, televisions built to support SECAM and PAL formats operate with a horizontal frequency of 15625 Hz, and a vertical frequency of 50 Hz.

Note that the American (and Japanese) format was the NTSC (National Television System Committee) with a horizontal frequency of 15734 Hz and vertical of 60 Hz.

The horizontal frequency of 15625 Hz comes from the use of 64  $\mu$ s delay line, invented for the design of the Secam format by the engineer Henri de France. As a reminder, 64 $\mu$ s = 0.000064 seconds (just enough time to have a strong coffee).

The CRTC follows this logic and processes about 1 million characters per second because its frequency is 1 MHz.

Without diabolical intervention on the position of the HSYNC, it is in principle programmed to generate complete lines of 64 µsec.

To get closer to the desired frequency, the CRTC is generally programmed to display 312 lines of 64µs, or exactly 19968 µsec (0.019968 seconds).

This frequency being linked to a clock, we can see drifts between 2 machines after a certain time.

The standard format initialized by the CPC ROM in a European country is :

- Lines of 64 horizontal "CRTC" characters of 1 µs each (composed of 40 characters displayed and 24 not displayed).

- 312 vertical lines, subdivided into vertical characters of 8 lines, or 39 characters.

- Formula : ((R4+1) x (R9+1)) + R5

- Of these 39 character lines, 25 are displayed.

- CRTC table ROM address: **&5C5**

The standard format initialized by the CPC ROM in the United States is:

- Lines of 64 horizontal "CRTC" characters of 1 μs each (composed of 40 characters displayed and 24 not displayed).

- 262 vertical lines, sub divided into vertical characters of 8 lines, or 32 characters + 6 lines of adjustment

- Formula : ((R4+1) x (R9+1)) + R5

- Of these 32.75 character lines, 25 are displayed.

- CRTC table ROM address: **&5D5**

**Note 1**: It is the bit 4 of port B of the PPI (LK4) that allows you to test which table to use.

<u>Note 2</u>: Initializing the CRTC is one of the first things the CPC's LOW ROM does when the machine is turned on and reset. Register initialization begins 64 µsec after the Z80A reads the first ROM instruction. Registers are updated from register 15 to register 0.

CTM monitors use the PC1031 (GT65 green monochrome monitor) and PC1378 (CTM 644 colour monitor) circuits. These circuits are used to drive the horizontal deflector to produce the signal the beam needs for scanning.

The GATE ARRAY of the CPC produces, via its pin 5, a composite synchronization signal combining VSYNC and HSYNC, which arrives at the DIN connector provided for the monitor (via a 220 Ohm resistor (R137)).

This composite signal is decoded by the circuits (PC1031 or PC1378) of the monitor. [Since the monitor is not a TV, the signals for the image are always RGB]

The CRTC has registers to manage a cursor and read data sent by an "optical pen". Cursor registers are not used on CPC, which does not handle a hardware cursor, usually provided when a text mode is handled.

However, they are a point of interest, because actions on other registers in or out of a synchronization period, with small values, could lead to consequences on other registers.

The operation of these registers is not covered (at the moment) in this document.

## 4.2 CRTC TYPES

AMSTRAD had the brilliant idea of using CRTC 6845 circuits manufactured by different manufacturers in its machines. They even designed ASIC's that could emulate its operation.

#### A bit of history

While Amstrad wanted to attack the US market with the CPC 6128, a problem was identified in ROM with registry value 5 (vertical adjustment).

This value was set at 6 in accordance with the desired frequency of 60Hz in the USA (262 lines), but (wrongly) ignored the interrupt system managed by the GATE ARRAY. Indeed, on a European CPC, interruptions start 2 lines (we will consider that we have 1 HSYNC per line) after the occurrence of the VSYNC signal by the CRTC.

These interruptions have a period of 52 "HSYNC lines", which gives exactly 6 periods during the 312 lines (see Chapter 25.6 on INTERRUPTS). To stall 5 periods of 52 lines, it would have been necessary to program 260 lines and not 262 as was done, and therefore that R5 is programmed with 4 instead of 6.

These 2 more lines cause the interruption to arrive on not the same line on which the CRTC reports the start of VSYNC, BUT before it.

That is, on a US CPC, a program whose main code tests the VSYNC wait via the PPI can be interrupted during this wait. If the interruption lasts too long, when it returns, the VSYNC waiting loop has missed the signal (the bit has returned to 0), and a risk of "deadlock" exists.

This could lead to compatibility issues for programs produced in Europe. AMSTRAD then decided to remedy the problem by ....changing the 60 Hz table to ROM.... No... I'm kidding... too simple.

To avoid this "deadlock" without modifying the ROM, Amstrad engineers thought they could "limit the problem" by increasing the duration of the VSYNC. This was perfectly possible using the CRTC's Registry 3, which had been programmed with 8 lines ..... in the ROM.

It is likely that they thought that there were CRTC models without the function used to set the number of VSYNC lines (these models set the number of lines at 16) and thus decided that the American CPCs would only be equipped with CRTC's 1 and 2, without this function.

If AMSTRAD engineers were aware of the existence of these differences, it can be assumed that the first CRTC's used were type 0s, since this function is used and programmed by the ROM.

From there to be able to say that without a bug related to a 4 instead of a 6 in the ROM, there would be only one type of CRTC used in all CPC's, it is to ignore the commercial considerations in the component market compared to the success of the machine in Europe.

Several companies have created different versions of the circuit, implementing additional functions, such as programming the number of lines of the VSYNC that I have just mentioned.

It can be deduced, however, that the designers of the BASIC ROM:

- originally worked with a CRTC with the ability to program the number of lines for VSYNC.

- felt that 8 lines of VSYNC were sufficient to vertically synchronize the image on a CTM monitor.

Beyond the functional and technical differences documented in circuit manufacturers' guides (called "datasheets" with 2 "e"'s), these CRTC's tend to behave differently when starting to modify registers:

- multiple times during a frame.

- during or outside HSYNC/VSYNC periods.

- with a value of 0, which is a special case for managing multiple registers.

These differences impact the compatibility of programs, especially when the address of the video pointer is updated.

This technique is still commonly called "*Rupture*" because... it is simpler and more generic than to say "*Offset Split Screen*".

Differences in counter management (which can overflow in a few situations) usually lead to a horizontal (R2) and/or vertical (R7) synchronization defect.

If a Z80A code "waits" for the VSYNC signal or uses interrupts (which depend on HSYNC), the mess is accentuated.

#### A bit of history

To my knowledge, the first program to have carried out a CRTC test was the game "Get Dexter" ("Crafton & Xunk" in French), written by Rémi Herbulot and Michel RHO in 1986. In this game, the screen update takes place through horizontal scrolling, which uses register 2 (positioning the HSYNC on another character).

This method, on a MOTOROLA CRTC, causes a loss of vertical synchronisation when VSYNC occurs during a HSYNC (Ghost Vsync). In other words, in this situation, the CRTC falsely believes it is generating a VSYNC signal for the monitor.

I guess Rémi Herbulot had to have access, at Ere Informatique game company, to a CPC with a HITACHI CRTC (like mine at the time) and another with a MOTOROLA CRTC. Having made this observation, he created a test based on the reading in &BF00 of register 12, which makes it possible to distinguish the CRTC HITACHI from the CRTC MOTOROLA.

And so, he managed a display with and without scrolling on the screen.

That is why there is no scrolling in this game on CPC's equipped with a UMC CRTC, while this CRTC does allow it without issue, because as with the MOTOROLA CRTC, its register 12 is not readable.

#### A bit of history (yet !)

When the first "rupture" techniques began to be used massively in demos, the differences between CRTC soon began to be a problem. And especially when independent programmers (often high school or university students) began to form the "demo" scene and their demos began to circulate in a less discretionary way. Initially, these first demos were mostly introductions for cracked games that circulated in schoolyards. [ I believe there is a game from the 80s that encountered this type of problem with the CRTC (to be checked) ]

The first demo programmers had not yet built up a "network" (the demoscene) and usually had only one machine on hand. The first intros and demos circulated in a small and very regional circle. The "network" consisted, in the 80s, of postal exchanges, Minitel's (a French ancestor of the internet, like Prestel in the UK) and ruinous telephone exchanges, with very little or no relations with other countries.

Communication with people from other regions first went through the consultation of classified ads in the few computer magazines of the time, because it was difficult to find contact details in the introduction preceding a cracked game. Programmers could hardly see the result produced by their code on other machines, and the inertia was enormous. It was difficult to adapt the code via postal exchanges, without having the machine (or even wanting to do it, simply). The problems encountered could range from image synchronization-loss to outright crashing of the machine.

It was difficult to be categorical about the actual origin of these problems, and especially about their extent. Nevertheless, with the grouping of the demomakers and the enlargement of the demoscene, it became possible to compare the code on different machines.

The presence of some electronics engineers in the ranks of the demomakers made it possible to identify the culprits... (Mr. SUGAR is still at large).

Some "universal" rules resulting from empirical approaches have been described in secret documentation which did not remain so for long ("You should not do this operation here in order for it to work everywhere", for example).

It should be noted that some techniques are still currently considered impossible to port from one CRTC to another (until this document...).

CRTC 2 (MOTOROLA) quickly proved to be the problematic one for one of the most widely used techniques, which is to place R4=R9=0.

The code needed to ensure CRTC compatibility can be much more complex than just knowing when to modify register 9 or 4, we'll see...

In order to exploit the rules allowing compatibility, it was first necessary to identify the different CRTC's.

Many methods exist today. See Chapters 26, page 223, and 27, page 225.

The numbering has remained fixed to this day from the order where I discovered these circuits with the help of some members of the group of demomakers Logon System.

We discovered the CRTC emulated "Pre ASIC" after the release of the AMSTRAD PLUS, and that's why its number is greater than 3, although it came out earlier chronologically.

| Туре | Brand                                     | Model      |

|------|-------------------------------------------|------------|

| 0    | HITACHI                                   | HD6845S(P) |

| 0    | U.M.C. (United Microcircuits Corporation) | UM6845     |

| 1-A  | U.M.C. (United Microcircuits Corporation) | UM6845R    |

| 1-B  | U.M.C. (United Microcircuits Corporation) | UM6845R    |

| 2    | MOTOROLA                                  | MC6845(P)  |

| 3    | AMSTRAD                                   | ASIC 40489 |

| 4    | AMSTRAD                                   | ASIC 40226 |

**Note 1**: CRTC's 3 and 4 are CRTC's emulated by ASIC's, but are nevertheless CRTC! Without enabling the complementary functions of ASIC 40489, the behaviour of these two CRTC's cannot be differentiated at present.

**Note 2 :** The "Pre-ASIC" (CRTC 4) was most certainly designed with the AMSTRAD PLUS in mind, as its C9 counter is intended to be interrupted on any line. This is why positioning R9 at 0 can be done on the last line of a character (CRTC 0 compatibility) or on the first line of a character (CRTC 1 compatibility).

**Note 3 :** It cannot be excluded even at present, that some series of CPC's may be equipped with different CRTC models, available from the 3 manufacturers. (Please let me know if you discover another model, and you are sure that it was not your little sister who replaced it for a laugh). Additionally, HITACHI's CRTC HD6845S, which is identified as type 0, behaves exactly like UMC's CRTC UM6845. Probably a business deal between the firms where it is just the manufacturer marking that has changed... The UMC documentation specifies this in its comparison table with other circuits. There is currently no test that allows the distinction of these two circuits, but it may be possible via the "Interlace" mode or the special management of C0 by the HD6845S.

**Note 4 :** Programming R3 with &8x is a very bad habit, since CRTC's 1 and 2 also exist in European machines, and they do not respect this value...

<u>Note 5</u>: Scheduling a specific update to a CRTC register in an interrupt routine that does not interrupt perfectly synchronized code is a very bad idea. (And may suggest (wrongly) a CRTC difference).

<u>Note 6</u>: The difference observed between two CRTC's UM6845R may not be linked to the CRTC. Nevertheless, there is a noticeable difference. (See Chapter 11.5)

## 4.3 GENERAL VIEW OF THE REGISTERS

|           |                                       |           |     |   |   | CRTC 0 |   |   |   |   |    |  |     |   |   | CRTC 1, 2 |     |   |    |    |   |     |   |     |   | CRTC 3, 4 |     |     |    |  |  |  |  |  |

|-----------|---------------------------------------|-----------|-----|---|---|--------|---|---|---|---|----|--|-----|---|---|-----------|-----|---|----|----|---|-----|---|-----|---|-----------|-----|-----|----|--|--|--|--|--|

| Register  | Definition                            | Unit      | r/w | 7 | 6 | 5      | 4 | 3 | 2 | 1 | 0  |  | r/w | 7 | 6 | 5         | 4 3 | 2 | 1  | 0  | r | ~/w | 7 | 6   | 5 | 4         | 3 2 | 2 1 | 0  |  |  |  |  |  |

| R0        | Horizontal total character number     | Char      | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | ۷ | N   |   |     |   |           |     |     |    |  |  |  |  |  |

| R1        | Horizontal displayed character number | Char      | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | ۷ | N   |   |     |   |           |     |     |    |  |  |  |  |  |

| R2        | Position of horizontal sync. pulse    | Char      | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | ۷ | N   |   |     |   |           |     |     |    |  |  |  |  |  |

| R3        | Pulse width of horizontal sync. pulse | Function  | W   | V | V | V      | V | h | h | h | h  |  | W   |   |   |           | h   | h | h  | h  | ۷ | N   | V | ٧ľ  | V | v h       | ۱h  | h   | h  |  |  |  |  |  |

| R4        | Vertical total character number       | Char Row  | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | ۷ | N   |   |     |   | T         |     |     |    |  |  |  |  |  |

| R5        | Total raster adjust                   | Scan Line | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | ۷ | N   |   |     |   |           |     |     |    |  |  |  |  |  |

| R6        | Vertical displayed character number   | Char Row  | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | ٧ | N   |   |     |   |           |     |     |    |  |  |  |  |  |

| R7        | Position of vertical sync. pulse      | Char Row  | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | ۷ | N   |   |     |   |           |     |     |    |  |  |  |  |  |

| R8        | Interlace Mode and Skew               | Function  | W   | С | С | d      | d |   |   | i | i. |  | W   |   |   |           |     |   | i. | i. | ۷ | N   | С | C I | d | d         |     | i   | i. |  |  |  |  |  |

| R9        | Max Scan Line Address                 | Scan Line | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | ۷ | N   |   |     |   |           |     |     |    |  |  |  |  |  |

| R10       | Cursor start                          | Scan Line | W   |   | b | р      |   |   |   |   |    |  | W   |   | b | р         |     |   |    |    | r |     | S | 1   | S | s s       | s s | S   | S  |  |  |  |  |  |

| R11       | Cursor end                            | Scan Line | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | r |     | S | 0   | S | 1 ร       | s s | S   | S  |  |  |  |  |  |

| R12       | Display start address (High)          | Pointer   | r/w |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | r | -/w |   |     |   |           |     |     |    |  |  |  |  |  |

| R13       | Display start address (Low)           | Pointer   | r/w |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | r | -/w |   |     |   |           |     |     |    |  |  |  |  |  |

| R14       | Cursor address (High)                 | Pointer   | r/w |   |   |        |   |   |   |   |    |  | r/w |   |   |           |     |   |    |    | r | ~/w |   |     |   |           |     |     |    |  |  |  |  |  |

| R15       | Cursor address (Low)                  | Pointer   | r/w |   |   |        |   |   |   |   |    |  | r/w |   |   |           |     |   |    |    | r | ~/w |   |     |   |           |     |     |    |  |  |  |  |  |

| R16       | Light Pen (High)                      | Pointer   | r   |   |   |        |   |   |   |   |    |  | r   |   |   |           |     |   |    |    | r |     |   |     |   |           |     |     |    |  |  |  |  |  |

| R17       | Light Pen (Low)                       | Pointer   | r   |   |   |        |   |   |   |   |    |  | r   |   |   |           |     |   |    |    | r |     |   |     |   |           |     |     |    |  |  |  |  |  |

| Access po | rts to the CRTC on CPC                |           | r/w | 7 | 6 | 5      | 4 | 3 | 2 | 1 | 0  |  | r/w | 7 | 6 | 5         | 4 3 | 2 | 1  | 0  | r | ·/w | 7 | 6   | 5 | 4         | 3 2 | 2 1 | 0  |  |  |  |  |  |

| &BC00     | Register selection                    | Number    | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | ۷ | N   |   |     |   |           |     |     |    |  |  |  |  |  |

| &BD00     | Register write                        | Value     | W   |   |   |        |   |   |   |   |    |  | W   |   |   |           |     |   |    |    | ۷ | N   |   |     |   |           |     |     |    |  |  |  |  |  |

| &BE00     | Register status                       | Function  |     |   |   |        |   |   |   |   |    |  | r   |   | L | b         |     |   |    |    | r |     |   |     |   |           |     |     |    |  |  |  |  |  |

| &BF00     | Register read                         | Value     | r   |   |   |        |   |   |   |   |    |  | r   |   |   |           |     |   |    |    | r |     |   |     |   |           |     |     |    |  |  |  |  |  |

See Chapters 21, 26.1.8 and 26.1.9 for more information on the content of the status register and reading this register according to the different CRTC's.

## 4.4 CRTC ACCESS

#### 4.4.1 GENERAL

Access to I/O with a Z80A usually requires the use of specific instructions.

These instructions (OUT, OUTI, INI, IND...) are in principle intended to use devices whose addresses are defined on the least significant 8 bits of the 16-bit address bus.

The 16-bit address bus is specified in the **BC** register, but some instructions (OUTD, OUTI, INI, IND, ...) also use **B** as counter.

From a computer design perspective, it is not advisable to place the address of devices that can use these instructions on the most significant byte of the 16-bits address bus.

This wise advice from Mr. ZILOG was not listened to by Mr. SUGAR.

Also access to devices on CPC mainly goes through **A8..A15 bits of the address bus** (FDC 765 being an exception in part).

Device selection bits should therefore be set to B.

Welcome to the CPC!

| Examples                  |                                       |                         |

|---------------------------|---------------------------------------|-------------------------|

| Selection register 12     |                                       |                         |

|                           | BASIC                                 | OUT &BC00,12            |

|                           | Z80A                                  | LD BC,&BC00+12:OUT(C),C |

| Sending valeur &30 in re  | gister 12                             | (previously selected)   |

|                           | BASIC                                 | OUT &BD00,&30           |

|                           | Z80A                                  | LD BC,&BD30:OUT (C),C   |

| Describer and the 10 (see | · · · · · · · · · · · · · · · · · · · |                         |

| Reading register 12 (pre  | 3                                     |                         |

|                           | BASIC                                 | PRINT INP(&BF00)        |

|                           | Z80A                                  | LD BC,&BF00 : IN A,(C)  |

| Reading status register   |                                       |                         |

|                           | BASIC                                 | PRINT INP(&BE00)        |

|                           | Z80A                                  | LD BC,&BE00 : IN A,(C)  |

|                           |                                       |                         |

The use of register B prevents the use of interesting instructions to send or read a series of successive values on a port, such as OTIR, OTDR, INIR, INDR.

Indeed, these instructions use B as the counter of the number of values to be read in a table and decrement this counter until it reaches the value 0.

#### **Digressive Remark :**

These repetitive instructions can be used experimentally, to process more than one value, on a device whose selection bits do not participate in the counter (most significant bits), such as the GATE ARRAY. It is possible to issue one of these instructions and savagely interrupt it by positioning it judiciously before an interruption occurs. This interruption will nevertheless have to "forget" the return address placed on the stack before re-authorizing other interruptions. This interesting aspect is however very limited (and especially playful) and can activate other devices depending on the number of values read in the table.

However, it is still possible to use

- OUTI or OUTD instructions to send one by one the data from a table (pointed by HL) to the CRTC.

- INI or IND instructions to read one by one the data from a table (pointed by HL) of the CRTC.

The advantage is that these instructions are "fast" according to the number of operations performed.

The use of the OUTI/OUTD statement is possible by first incrementing B between each instruction for OUTI/OUTD because B is decremented before accessing the port. For the CRTC, which uses bits 0 and 1 of B as an index, this implies that B is pre-loaded with the port address + 1 for the OUTI/OUTD instructions to work.

For reading instructions, the addressed device is defined by BC before B is decremented, so it must contain the normal address of the port before reading.

| Example in | <u>n Z80A :</u> |                                                             |

|------------|-----------------|-------------------------------------------------------------|

| -          | LD BC,&BC02     | ; Hsync position register selection                         |

|            | OUT (C),C       |                                                             |

|            | LD HL, TABHSYNC | ; Pointer to Hsync position table                           |

|            | LD B,&BD+1      | ; IO Address sending data+ 1 : &BE                          |

|            | OUTI            | ; OUTI decrease B by 1, send TABHSYNC[0] on the &BD IO Addr |

|            |                 | ; and then increase the pointer by 1                        |

|            | INC B           | ; B is set again to &BE                                     |

|            | OUTI            | ; OUTI decrease B by 1, send TABHSYNC[1] on the &BD IO Addr |

|            |                 | ; and then increase the pointer by 1                        |

| TABHSYNC   | DB 50, 10       |                                                             |

#### 4.4.2 Z80A INSTRUCTIONS

Instructions in Z80A for processing Input/Output :

| INSTR.     | DURATION | DESCRIPTION                                                                                                                                                                                                                                                   |

|------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT (C),r8 | 4 µsec   | r8=[A or B or C or D or E or H or L]<br>Writing to devices defined in BC the value contained in the r8 register.                                                                                                                                              |

| OUT (n),A  | 3 µsec   | The input-output address is defined by the couple An, and the data sent to the device is A. This double constraint drastically limits the number of values available to one device without causing a collateral effect on another device (selection + value). |

| OUT (C),0  | 4 µsec   | Writing value 0 to the device(s) defined in BC. An interesting instruction for a demomaker! But not only that                                                                                                                                                 |

| OUTI       | 5 µsec   | Decrement B, then read the value pointed by HL, incrementing HL and sending the value read on the port sent by BC.                                                                                                                                            |

| OUTD       | 5 µsec   | Decrement B, then read the value pointed by HL, decrementing HL and sending the value read to the port sent by BC                                                                                                                                             |

| IN r8,(C)  | 4 µsec   | r8=[A or B or C or D or E or H or L]<br>Read in the r8 register the value sent by the device defined in BC. If<br>several devices are selected, there is no doubt that a game of musical<br>chairs will take place                                            |

| IN A,(n)   | 3 µsec   | The input-output address is defined by the couple An, and the data read will modify A.                                                                                                                                                                        |

| IN (C)     | 4 µsec   | It is an "unofficial" instruction. The value present on the data bus is read and its evaluation affects F.                                                                                                                                                    |

| INI        | 5 µsec   | Reading the value on the port addressed by BC and writing this value to the address pointed by HL, HL decrement, B decrement                                                                                                                                  |

| IND        | 5 µsec   | Reading the value on the port addressed by BC and writing this value to the address pointed by HL, HL decrement, B decrement                                                                                                                                  |

#### 4.4.3 ACCESS DELAYS

The following table indicates for some I/O write instructions the timing of the register update in the CRTC and for some I/O read instructions the timing when the value from the circuit is updated in the Z80A register or RAM.

| INSTRUCTIONS | DURATION | I/O CONSI            | DERATION  |

|--------------|----------|----------------------|-----------|

| INSTRUCTIONS | DURATION | CRTC 0, 1, 2         | CRTC 3, 4 |

| OUT (C),r8   | 4 µsec   | 3rd µsec             | 4th µsec  |

| OUT (C),0    | 4 µsec   | 3rd µsec             | 4th µsec  |

| OUT (n),A    | 3 µsec   | 3 <sup>rd</sup> µsec | 3rd µsec  |

| OUTI         | 5 µsec   | 5th µsec             | 5th µsec  |

| OUTD         | 5 µsec   | 5th µsec             | 5th µsec  |

| IN r8,(C)    | 4 µsec   | 4th µsec             | 4th µsec  |

| INI          | 5 µsec   | 4th µsec             |           |

| IND          | 5 µsec   | 4th µsec             |           |

| IN A,(n)     | 3 µsec   | 3rd µsec             | 3rd µsec  |

It is important to note however, that consideration of a write during the update microsecond does not take place at the same "time" according to the instructions used, and this can therefore affect the management of the value by the circuit.

One way to measure this difference is to use processes that are not "slowed down" by the CRTC and the GATE ARRAY, such as the HSYNC display for example. See Chapter 16, page 133.

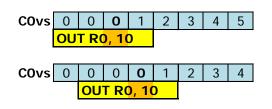

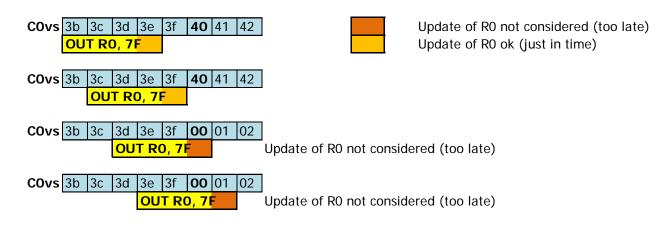

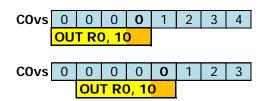

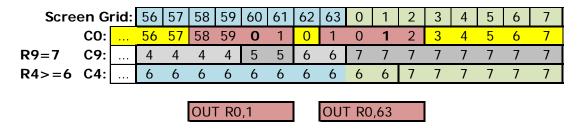

We can also measure this difference, for example, between what happens with an I/O on the 3rd NOP of an OUT(C),R8 and the 5th NOP of an OUTI on a CRTC 1. See Chapter 13.6.2, page 109.

It should also be noted that on CRTC's 3 and 4, the CRTC misses the I/O on the 3rd µsec of OUT(C),R8 instruction and retrieves it on the 4th µsec of the instruction. Which delays register updates by 1 µsec if this instruction is used. This shift does not occur if the OUTI/OUTD instructions are used. See next Chapter.

The majority of the diagrams that refer to Input-Outputs in this document are performed on the basis of the OUT(C),R8 instruction. For CRTC's 3 and 4, the Input-Output is positioned on the 4th µsecond.

In practice, for code produced for CRTC's 3 or 4, it is necessary to position a write I/O **instruction 1 µsec before the one which would have been placed for CRTC**'s 0, 1 or 2.

This is established!

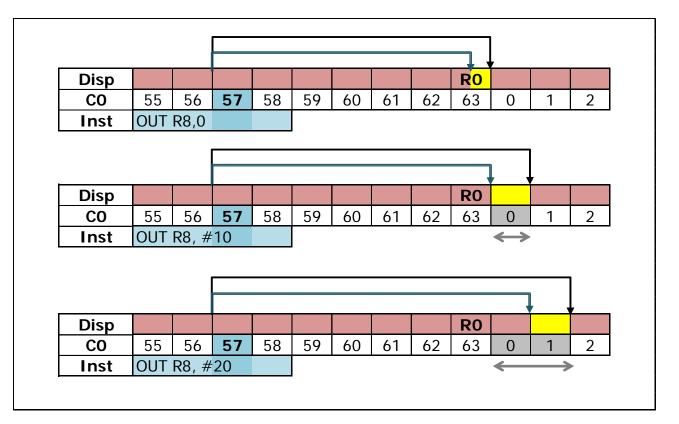

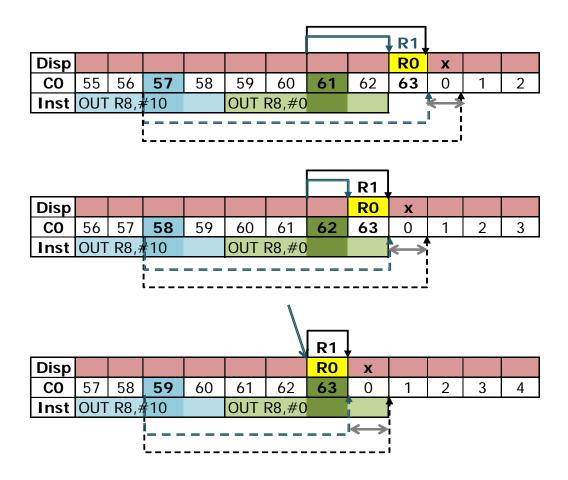

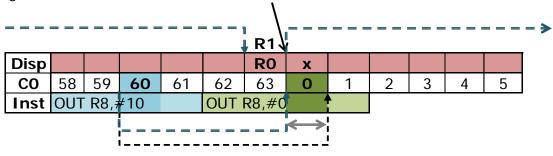

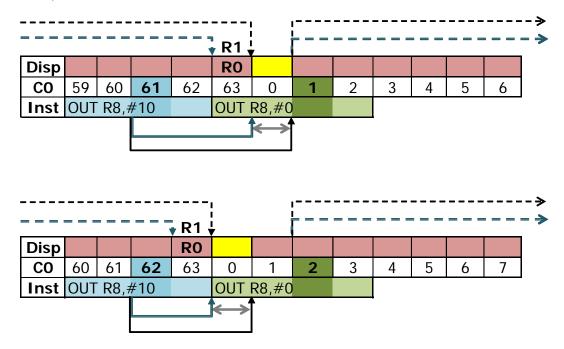

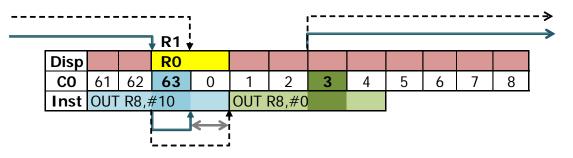

#### 4.4.4 OUTS DISSECTION

This chapter aims to try to explain why an output entry with an "OUT(C),R8" occurs on the 3rd NOP for a CRTC equipped with a GATE ARRAY, and on the 4th NOP for an ASIC that emulates a CRTC (CRTC's 3 and 4), but also why there is a difference (whether on a CRTC or ASIC) between an input/output performed with an "OUT(C),R8" and that performed with an "OUTI".

The GATE ARRAY, within the CPC, is THE conductor for many components. It is clocked at the staggering speed of 16 MHz (which allows it to display pixels Mode 2 at 0.0625  $\mu$ Sec). It gives a 1 MHz rate for the AY-3-8912 (sound generator), the CRTC, and clocks the Z80A at 4 MHz.

One of the objectives of the gate array designers was to use Z80A's ability to slow down its execution to retrieve the RAM access priority for addresses pointed to by the CRTC.

The instructions of a z80a consist of periods of execution (called cycles M) in which several subperiods occur (called cycles T). Each "T" sub-period duration is 0.25 µsec (the size of 4 pixels in graphic mode 2).

The common point of all Z80A instructions is the need to access the RAM to read the code(s) of the instruction to be executed (called "**opcode**" for operation code). This reading, called "**opcode** fetch", is performed during a first cycle called M1. Each cycle M performs a basic instruction :

- Reading a RAM opcode ("opcode fetch").

- Reading or writing in a byte by the Z80A internal code that executes the opcode.

- Reading or writing an input / output port ("IO REQ").

- Bus: request or acknowledge.

- Interruption: request or acknowledge.

A cycle M consists of several T cycles, some of which place a wait signal in the active state to indicate to another circuit that the Z80A agrees that it should be slowed down. This wait cycle is commonly named Tw. This is particularly the case for the instructions:

- OPCODE FETCH, during the 2nd cycle T.

- Reading or writing memory, during the **2nd cycle T**.

- IO REQ, during the 3rd cycle T.

When the Z80A "performs" a cycle Tw, it looks at its Wait line (in this case that connected to the gate array) and if it is active, then it will generate another cycle TW. This makes it possible to block the processor indefinitely if the circuit that drives the line wait decides to.

This blocking is only possible if the processor has allowed it in a **Tw** cycle and the GATE ARRAY/ASIC made the blocking request at that time.

The trick of the **GATE ARRAY/ASIC** designers has been to **continually generate 3 Tw followed by a "no Tw" cycle**. When the Z80A, for a Cycle T that makes a wait, falls on one of these cycles Tw, it will run the "remaining" sequence of Tw, which has the effect of "**linearizing**" the instructions over 4 T Cycles.

In other words, if an instruction started on an "aligned" T-cycle and ends with a number of T-cycles which is not a multiple of 4, then the next instruction will be "stretched" during its first cycle "M".

To illustrate this, diagram A on the following pages describe an **OUT(#nn)**,**A** instruction (1 opcode #D3) that needs 11 cycles to run. This instruction has an odd number of T-cycles (so no multiple of 4) and is immediately followed by a second **OUT (#nn)**,**A**.

When running the first **OUT(#nn)**,**A**, none of the WAIT signals of the Z80A falls at the same time as a WAIT signal from GATE ARRAY. The instruction is executed in 11 T-Cycles (0.25 x 11 = 2.75  $\mu$ Sec).

When the second **OUT(#nn)**, **A** is executed, the WAIT signal from the Z80A during cycle M1 occurs at the same time as the WAIT signal from the GATE ARRAY. This causes the generation of a 2nd wait T-cycle by the Z80a (see "**Wait extent**" on the diagram A). During this 2nd wait cycle, the GATE ARRAY does not send a WAIT signal, which stops the generation of wait cycles by the z80a. Therefore this 2nd OUT (#nn), finds itself "stretched" by 0.25 µsec to match the memory access pattern defined by the gate array. Its execution then takes 3 µsec (12 t-cycles).

And so on. As long as the "rectified" instruction itself contains an "unaligned" number of T-cycles, the duration of the following instruction will also be rectified. Thus in the previous example, if a NOP (4 t-cycles) is added behind the 2nd **OUT(#nn)**,**A**, then the cycle T2 of the M1 cycle will generate a wait at the same time as the gate array, which will lengthen the NOP duration of 0.25  $\mu$ sec (so 1.25 $\mu$ sec in total). Another NOP after this first NOP will be aligned. Indeed, the T2 cycle of its M1 cycle will be aligned with the "non-wait cycle" of the GATE ARRAY, and the instruction will then run in 4 T-Cycles (1  $\mu$ sec).

The same goes for all the instructions whose M1 cycle lengthens according to the timing of the gate array in order to maintain priority on the RAM accesses to the address provided by the CRTC every 4 T-Cycles.

As part of an I/O writing operation, this mechanism is used to stall, compared to the beginning of a µsec, the moment when I/O begins. In this case on **the cycle T2 of the I/O M cycle**. The Z80A puts the I/O address on the data bus (a reminder of address &BD00 for writing to a CRTC register).

The GATE ARRAY clocks the CRTC at 1 MHz (but not quite at the same time as for the AY-3-8912). The CRTC periodically checks whether the Z80A IORQ signal is active in order to determine if it is affected by the I/O. If this is the case when writing, it can recover the value to select one of its registers or update the one that is selected.

Depending on the instruction which generates the I/O, the data is not immediately present when the CRTC is in a state to update its registers, which may have the consequence of deferring the writing of registers between 2 different instructions within the same micro-second. This is particularly the case between the instruction OUT(C),reg and OUTI, whose difference can be highlighted with R2.jit or R3.jit techniques, for example. Diagram B on the following pages parallels these two instructions.

In principle, the ASIC's do not clock the CRTC exactly like the GATE ARRAY ("CRTC's" 3 and 4). There is undoubtably a lag of the type which I represented on diagram C, which has the consequence of modifying the time of register updates relative to what happens with the GATE ARRAY.

It also explains why the update of a CRTC register takes place on the 5th  $\mu$ sec of the OUTI instruction, regardless of the type of CRTC, while there is a difference of 1  $\mu$ sec when the update takes place with the OUT(C),R8 instruction.

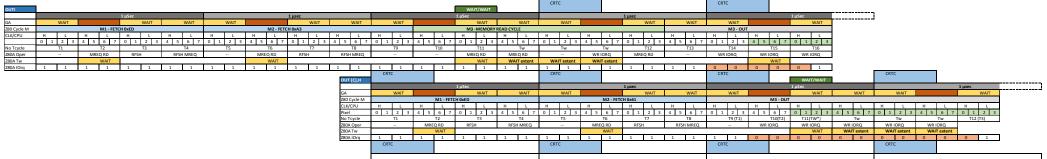

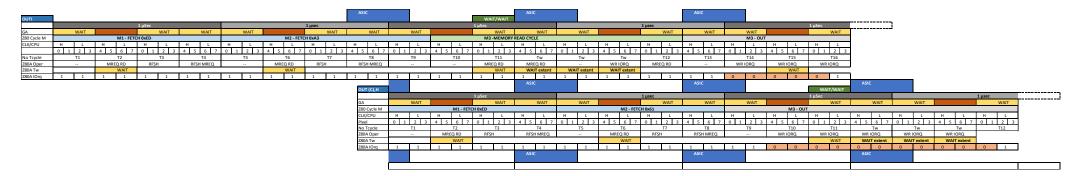

#### Diagram A : OUT(#NN),a + OUT (#nn),A + NOP + NOP

| OUT(#nn),A                                                           |                   |                                                                         |                 |                                                |                   |                   |                               |                                                |                   |                                                                       |         |                      |

|----------------------------------------------------------------------|-------------------|-------------------------------------------------------------------------|-----------------|------------------------------------------------|-------------------|-------------------|-------------------------------|------------------------------------------------|-------------------|-----------------------------------------------------------------------|---------|----------------------|

|                                                                      |                   |                                                                         | 1 μSec          |                                                |                   |                   | 1 µsec                        |                                                |                   |                                                                       | 1 μSec  |                      |

| GA                                                                   | WAIT              |                                                                         | WAIT            | WAIT                                           | WAIT              |                   | WAIT                          | WAIT                                           | WAIT              |                                                                       | WAIT    |                      |

| Z80 Cycle M                                                          |                   | M1 - FETCH                                                              | 0xD3            |                                                |                   | M2 -READ CYCLE    |                               |                                                | M3 - OUT          |                                                                       |         |                      |

|                                                                      | 8 9 10 11         | 12 13 14 15                                                             | 0 1 2 3         | 4 5 6 7                                        | 8 9 10 11         | 12 13 14 15       | 0 1 2 3                       | 8 9 10 11                                      | 12 13 14 15       | 0 1 2 3                                                               | 4 5 6 7 |                      |

| No Tcycle                                                            | T1                | T2                                                                      | Т3              | T4                                             | T5                | T6                | T7                            | Т8                                             | Т9                | T10                                                                   | T11     |                      |

| Z80A Oper                                                            |                   | MREQ RD                                                                 | RFSH            | RFSH MREQ                                      |                   | MREQ RD           | MREQ RD                       |                                                | WR IORQ           | WR IORQ                                                               | WR IORQ |                      |

|                                                                      |                   |                                                                         |                 |                                                |                   |                   |                               | -                                              |                   |                                                                       |         |                      |

| Z80A Tw                                                              |                   | WAIT                                                                    |                 |                                                |                   | WAIT              |                               |                                                |                   | WAIT                                                                  |         |                      |

| Z80A Tw                                                              | ]                 | WAIT                                                                    |                 |                                                |                   | WAII              | J                             |                                                |                   | WAIT                                                                  | l       |                      |

|                                                                      | 2                 | WAIT                                                                    |                 |                                                |                   | WAII              | ]                             |                                                |                   | WAIT                                                                  | I       |                      |

|                                                                      | 2                 | WAIT                                                                    |                 | 1 µsec                                         |                   | WAII              |                               | 1 µSec                                         |                   | WAIT                                                                  | I       | 1 μsec               |

|                                                                      | 2<br>WAIT         | WAIT                                                                    |                 | 1 µsec<br>WAIT                                 | WAIT              | WAIT              |                               | 1 μSec<br>WAIT                                 | WAIT              | WAIT                                                                  |         | 1 µsec               |

| OUT(#nn),A<br>GA                                                     |                   |                                                                         | 0xD3            |                                                | WAIT              |                   | M2 -READ CYCLE                |                                                | WAIT              |                                                                       |         | 1 µsec               |

| OUT(#nn),A<br>GA                                                     |                   | WAIT                                                                    | 0xD3<br>0 1 2 3 |                                                | WAIT<br>8 9 10 11 |                   | M2 -READ CYCLE<br>12 13 14 15 |                                                | WAIT<br>8 9 10 11 | WAIT                                                                  | 0 1 2 3 | <b>1 µsec</b><br>4 5 |

| OUT(#nn),A<br>GA<br>Z80 Cycle M                                      | WAIT              | WAIT<br>M1 - FETCH                                                      |                 | WAIT                                           |                   | WAIT              |                               | WAIT                                           |                   | WAIT<br>M3 - OUT                                                      |         |                      |

| Z80A Tw<br>OUT(#nn),A<br>GA<br>Z80 Cycle M<br>No Tcycle<br>Z80A Oper | WAIT<br>8 9 10 11 | WAIT           M1 - FETCH           12         13         14         15 | 0 1 2 3         | WAIT           4         5         6         7 | 8 9 10 11         | WAIT<br>8 9 10 11 | 12 13 14 15                   | WAIT           0         1         2         3 | 8 9 10 11         | WAIT           M3 - OUT           12         13         14         15 | 0 1 2 3 |                      |

| NOP         | 3         |             |             |         |           | NOP 4       |            |         |           |

|-------------|-----------|-------------|-------------|---------|-----------|-------------|------------|---------|-----------|

|             |           |             |             | 1 µsec  |           |             |            | 1 μSec  |           |

| GA          | WAIT      | WAIT        |             | WAIT    | WAIT      | WAIT        |            | WAIT    | WAIT      |

| Z80 Cycle M |           | M1 - FETCH  | l 0x00      |         |           |             | M1 - FETCH | 0x00    |           |

|             | 8 9 10 11 | 12 13 14 15 | 0 1 2 3     | 4 5 6 7 | 8 9 10 11 | 12 13 14 15 | 0 1 2 3    | 4 5 6 7 | 8 9 10 11 |

| No Tcycle   | T1        | T2          | Tw          | T3      | T4        | T1          | T2         | Т3      | T4        |