# MUSIC MACHINE

THE COMPLETE HOME COMPUTER MUSIC SYSTEM

AMSTRAD

USER GUIDE

RAM Electronics and Flare Technology thank you for choosing one of our products; we hope that you have as much fun using The Music Machine as we did designing and building it.

#### About RAM:

RAM Electronics are manufacturers of a wide range of computer peripherals. Perhaps they are best known to you for their successful Spectrum Turbo joystick interface? If you want to know more about their other Spectrum hardware, just look out for their adverts in the home computer press or drop them a line at the address below.

#### About Flare:

All of the people who work for Flare used to work for Sinclair Research, so is it any wonder that The Music Machine (which Flare designed) is so good? Look out for future exciting products from this team.

Please remember to complete and return the guarantee card which is enclosed with The Music Machine. Not only will doing this help you (see your rights as a purchaser on the card), but it will enable us to keep you informed of additions to the range of Music Machine software from time to time. Thank you.

Whilst we have made every effort to ensure that the contents of this manual are accurate, we reserve the right to make hardware and software improvements from time to time.

1986 RAM Electronics (Fleet) Ltd

1986 Flare Technology Ltd

RAM Electronics (Fleet) Ltd Unit 16, Redfields Industrial Park, Redfield Lane, Church Crookham, Aldershot, Hants GU13 0RE

# **CONTENTS**

| 0. | CAN'T WAIT TO TRY IT, HUH?                                                           |    |  |  |

|----|--------------------------------------------------------------------------------------|----|--|--|

|    | For the experienced only!                                                            |    |  |  |

| 1. | INTRODUCTION                                                                         | 2  |  |  |

|    | What The Music Machine can do                                                        |    |  |  |

| 2. | PLUGGING EVERYTHING TOGETHER                                                         |    |  |  |

|    | How not to get your wires crossed                                                    |    |  |  |

|    | 2.1 Connecting The Music Machine to your<br>Amstrad                                  |    |  |  |

|    | 2.2 Plugging in The Music Machine and an                                             |    |  |  |

|    | amplifier or headphones; where to put your microphone                                |    |  |  |

|    | 2.3 Loading the software from tape or disk                                           |    |  |  |

| 3. | GETTING STARTED QUICKLY                                                              | 10 |  |  |

|    | How to start making sounds before reading the rest of                                |    |  |  |

|    | this manual                                                                          |    |  |  |

|    | 3.1 Playing the sounds, rhythms, and songs supplied on the software cassette or disk |    |  |  |

|    | 3.2 Some quick experiments for making your own sounds                                |    |  |  |

| 4. | DETAILED DESCRIPTIONS OF WHAT DOES WHAT                                              | 18 |  |  |

|    | How to get your sounds, tunes and songs together                                     |    |  |  |

|    | 4.1 Playing using the Amstrad keyboard                                               |    |  |  |

|    | 4.1.1 The bar editor                                                                 |    |  |  |

|    | 4.1.2 The tune editor                                                                | -  |  |  |

|    | 4.2 The drum machine                                                                 |    |  |  |

|    | 4.2.1 The rhythm editor                                                              |    |  |  |

|    | 4.3 Recording real-life sounds                                                       |    |  |  |

|    | 4.3.1 Editing captured sounds                                                        |    |  |  |

|    | 4.4 Playing using an external keyboard                                               |    |  |  |

|    | 4.4.1 MIDI in, out and through                                   |

|----|------------------------------------------------------------------|

|    | 4.4.2 Combining tunes and drums                                  |

|    | 4.5 The effects box; echo and reverberation                      |

|    | 4.6 Recording and replaying your compositions                    |

|    | 4.6.1 Cassette and disk storage                                  |

| 5. | TECHNICAL SPECIFICATION OF THE                                   |

|    | MUSIC MACHINE                                                    |

|    | What you can and can't expect it to do                           |

|    | 5.1 Technical Spec.                                              |

|    | 5.2 Capacity in terms of stored sounds, tunes, songs and rhythms |

|    | 5.3 Additional notes                                             |

|    |                                                                  |

#### 0. CAN'T WAIT TO TRY IT, HUH?

This chapter is for those users who want to use the Music Machine before they read the manual. Only start here if you really know what you are doing. If you are in any doubt at all, read chapters 2 and 3 NOW. Do not hurt yourself by using an amplifier stupidly!

- 1. Power off everywhere.

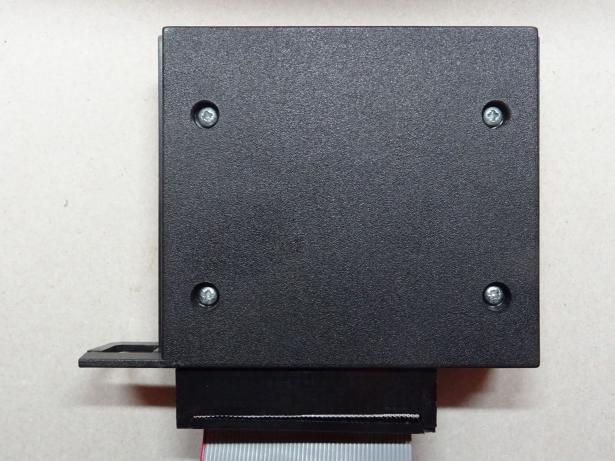

- 2. Connect Music Machine to bus using ribbon cable supplied.

- 3. Plug in amplifier or phones.

- 4. Plug in microphone.

- 5. Power on computer (and amp if you are using one).

- 6. Load software.

- 7. Select function by pressing capital letter associated with menu choice.

- 8. Play the drum rhythm supplied by pressing 'P'.

- 9. Play the song supplied by pressing 'M' then '7' then 'Q' then 'P'.

- 10. Experiment, then read chapter 4.

#### 1. INTRODUCTION

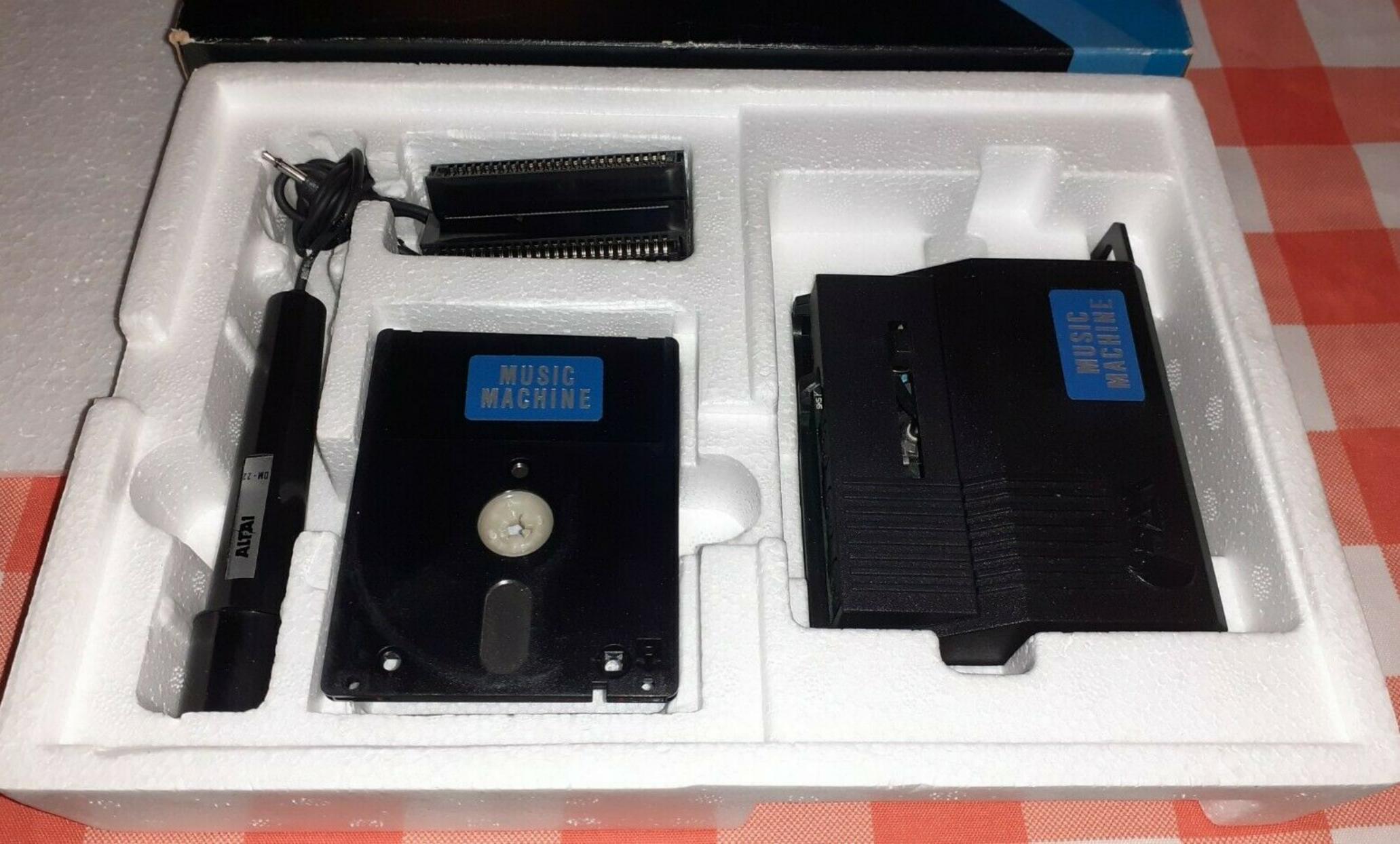

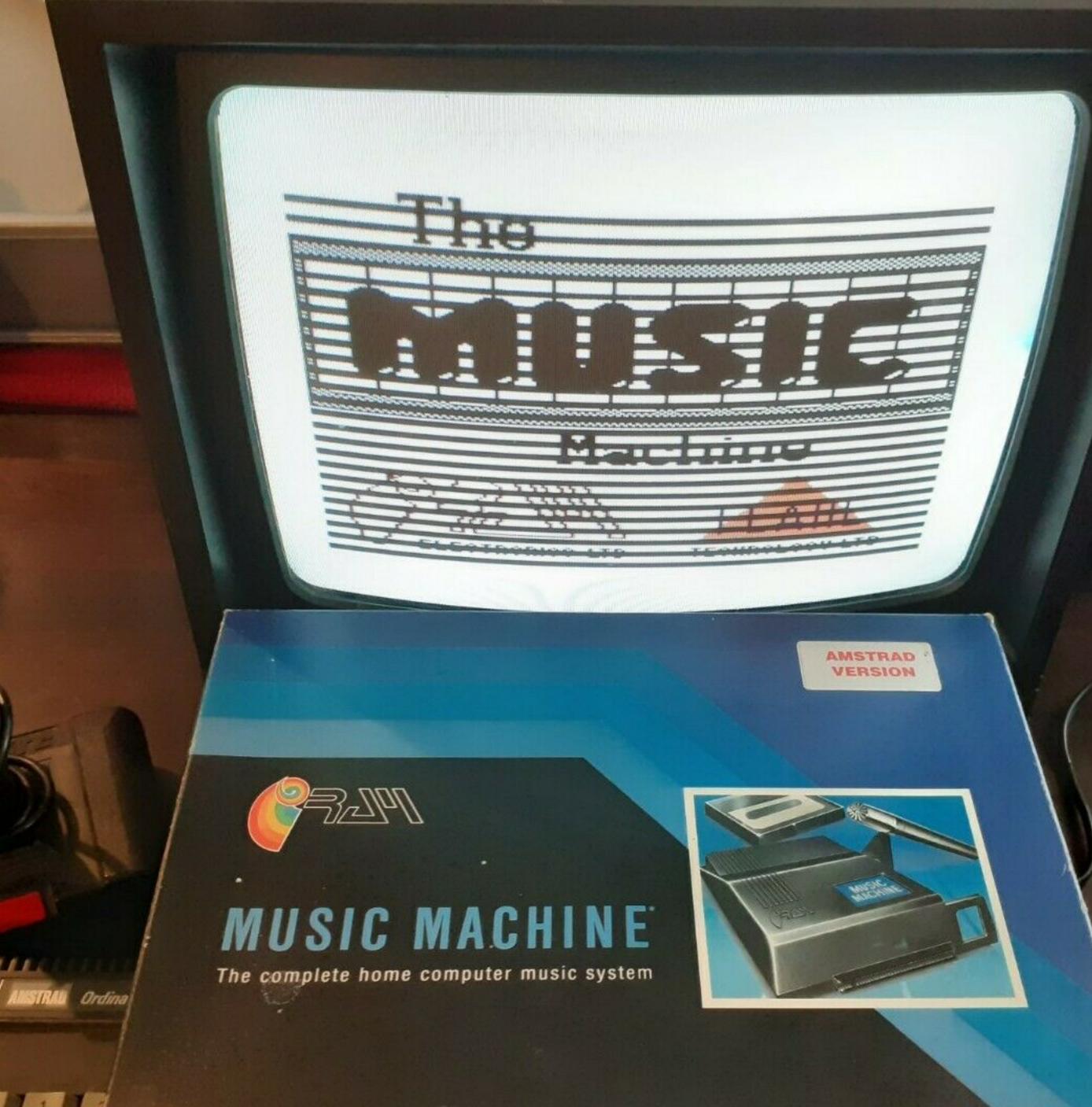

We believe that The Music Machine is the most powerful and exciting Amstrad add-on ever to reach the market. If your friends have already told you about the amazing things it can do, then skip this section of the manual and go to Chapter 2.

O. What is The Music Machine?

A. It is a peripheral that plugs into the back of the Amstrad CPC 464, 664, and 6128 computers. There is also a version for the Sinclair Spectrum range of computers.

The machine lets you compose your own sounds, tunes, songs and drum rhythms - even if you don't know much about music at all. It also lets you do special effects.

Q. What sort of things can The Music Machine do?

A. This question would be easier to answer if it asked what The Machine cannot do!

It can do ALL of the following:

The Amstrad version of the Machine can act as a one-voice synthesiser and can also play the computer's programmable sound generator. By using the computer keyboard, it can play both simple notes and complex sounds. Effects can be based on the sound of a piano or an electric guitar or a trombone: in fact, it can be made to sound similar to any musical instrument you care to name.

You can even make it sound like your own voice (try N-n-n-n-nineteen for example!), or a dog barking, or a police car, or a window breaking. Any noise that can be picked up by microphone can be played back at different pitches by the computer.

Eight sounds are supplied on the software cassette with The Machine and this User Manual tells you how to make others.

The machine can be used to make drum sounds. You can play up to three drums simultaneously from a selection of eight. If you don't like any of the percussion sounds supplied, you can use your own. Perhaps you would rather replace the tom-tom with a telephone ring? Simple!

You can compose songs from individual bars of music. You can edit bars on the screen, and merge them with bars from other tunes to make new songs. You can build up a library of tunes, record and save sounds and instruments, and record and save drum sounds and rhythms.

The Music Machine can be used as a digital delay box. Play music or speak through the microphone and you will be able to alter the delay rate (short or long echoes, for example) of the sounds as they come through your amplifier's loudspeaker.

If you have a MIDI synthesiser keyboard, you can plug this into The Machine in order to send and receive MIDI data. This means that your own sounds and effects can be played by The Machine by hitting keys on the synthesiser keyboard.

Also, sounds produced by The Machine can be mixed with the synthesiser's own voices. It is possible to send notes from The Machine to the MIDI keyboard, (or, because several MIDI devices can be plugged in simultaneously, some other MIDI peripheral).

The Machine enables songs created with the screen editor to generate MIDI data, and will allow you to play MIDI together with your drum rhythms. At the same time as The Machine sends songs to the synthesiser and plays the drums, you can play accompaniments on the keyboard.

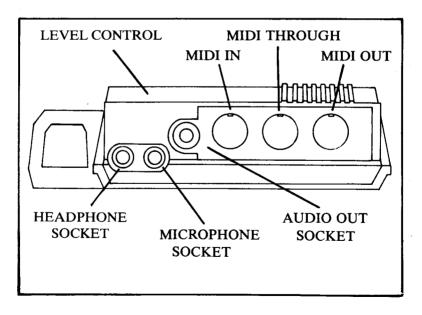

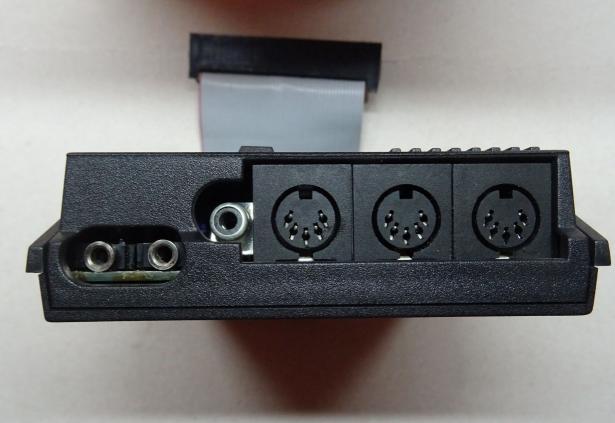

- Q. What can I plug into The Machine?

- A. The Machine has the following connectors:

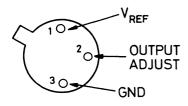

Amstrad bus connector

An audio-out phono socket for connection to your hi-fi

An earphone socket so that you can use your personal stereo headphones

A socket into which you plug the supplied microphone for capturing sounds

MIDI in, out, and through for hooking up MIDI devices such as synthesisers or sequencers.

- Q. What will the software let me do?

- A. All of the things described above. Example bars, songs, sounds and rhythms are supplied with the tape in program form.

If you have bought a cassette version of the software, on the reverse side of the tape is an audio track that you can play through a tape-recorder in order to hear what The Machine can do. We hope to bring you other clever and sophisticated software in the future.

- Q. Is there anything else like the Music Machine available for the Amstrad?

- A. Some suppliers sell peripherals that do one or two things that the Machine does, but you can't easily use lots of their peripherals together. And even if you could, you would have to spend about three times as much.

- Q. Can the Music Machine be used with the Amstrad's programmable sound generator?

- A. Yes. It can play one instrument and several percussive preselected sounds.

#### 2. PLUGGING EVERYTHING TOGETHER

Because The Music Machine can do so many things, we have provided you with a range of sockets into which you can plug various pieces of equipment. However, before you start sticking plugs into sockets, you must connect The Music Machine to your Amstrad.

If you have never used an Amstrad before, then please read your User Instructions before going any further.

#### 2.1 Connecting The Music Machine to your Amstrad

Although it is not absolutely necessary, we recommend that you unplug the monitor and keyboard leads from your Amstrad before you start. This will make things easier for you when you assemble your music system.

However, you MUST unplug the mains cable from your computer and remove any peripherals from the bus before you start. (Did you know that the most common way of blowing-up computers and peripherals is by plugging and unplugging them while the power supply is connected? Don't ruin your computer system before you've had a chance to use your terrific Music Machine!)

## Here we go:

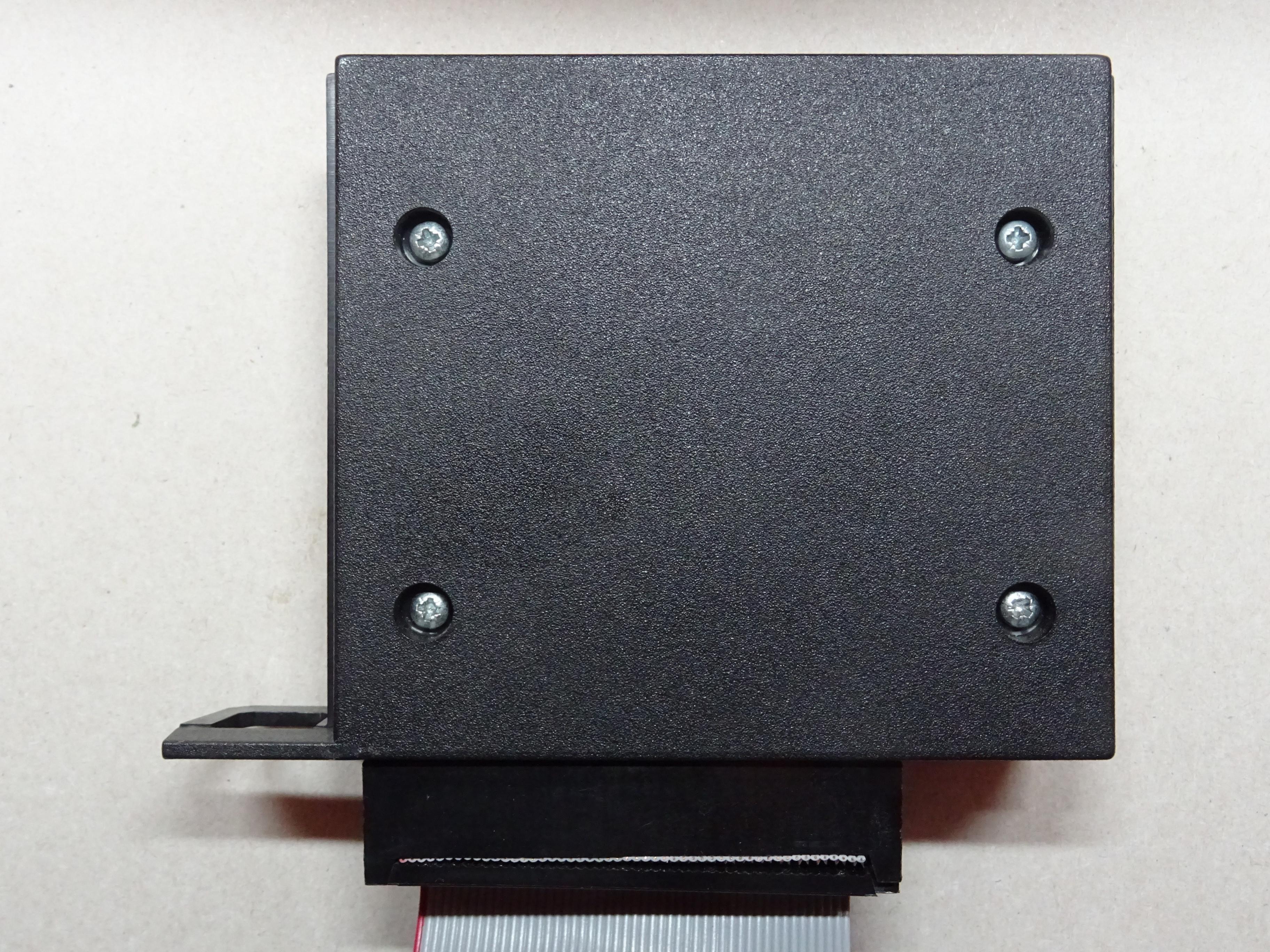

- (a) With the mains disconnected from your Amstrad connect the ribbon cable supplied onto the front of the Music Machine and then push the other end onto the expansion bus edge connector. Look at the user instructions if you aren't sure where the expansion bus connector is.

- (b) Re-connect the Amstrad monitor and keyboard.

- (c) Switch on the power to your computer.

You should now get the standard Amstrad copyright message screen.

(If you don't get this screen, switch off the power, disconnect The Music Machine, then try the computer by itself. If the copyright message screen still does not appear, then you may not have plugged everything in and switched on properly. See your Amstrad User Instructions.

You are now ready to plug other leads in.

Please remember the golden rule: ALWAYS UNPLUG THE POWER SUPPLY LEAD BEFORE ADDING OR REMOVING PERIPHERALS THAT USE THE EDGE CONNECTOR.

# 2.2 Plugging in The Music Machine and an amp/phones/mic

In order to hear the fabulous quality of the sound produced by The Music Machine, we have supplied you with both an amplifier socket and a headphone socket.

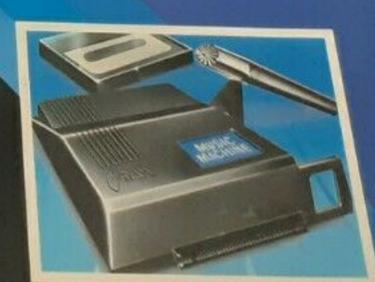

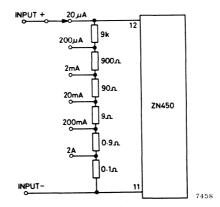

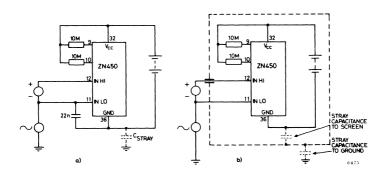

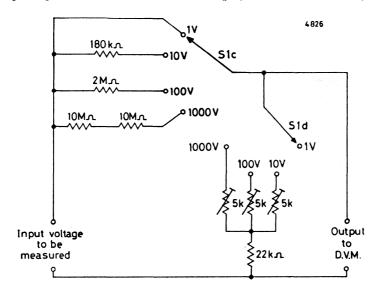

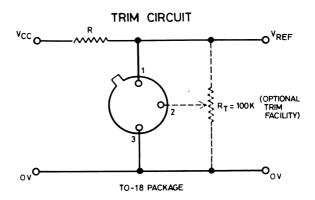

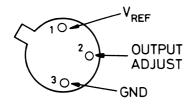

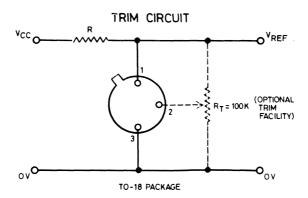

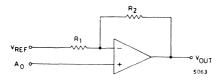

Figure 1 shows you the position of the phono socket which carries the audio output signals. Into this can be plugged a lead to your hi-fi amplifier, or maybe a guitar amplifier. Because there are so many different amplifier plugs and sockets on the market, we have not been able to supply leads that will suit everybody's equipment. However, it should not be difficult for you to get an appropriate lead from either your local hi-fi supplier or an electrical shop.

IF YOU ARE IN ANY DOUBT AT ALL ABOUT WHAT TO DO, GET HELP FROM AN ADULT OR A SPECIALIST. NEVER FOOL AROUND WITH ELECTRICITY AS IT CAN KILL YOU. Remember that we cannot be held responsible for any dangerous things that you do. Please be careful!

Before you connect your hi-fi to The Music Machine, turn the volume right down on the amplifier, plug the lead into a spare socket (probably marked 'AUX' or 'Auxillary', and select the appropriate input on the amplifier's controls. If you are using a guitar or PA amp, it should be obvious which socket you should use - but again, don't forget to turn the volume down.

If plugging The Machine into an amplifier is too much like hard work right now, then why not use a pair of personal-stereo headphones? Simply plug these into the headphone socket shown in Figure 1.

Finally, plug the supplied microphone into the small jack socket shown in Figure 1. Make a mental note of the position of the gain control (this is a bit like a volume control) on the top of The Music Machine, as you will need to use this as soon as you start experimenting with sounds.

Don't worry about the three DIN sockets (marked MIDI in, out and through) for the time being. We'll come back to these later.

#### 2.3 Loading the software from the tape or disk

Almost ready now! As soon as you've loaded the program, you can begin your music-making.

Figure 1, Music Machine Connector details

### Tape loading

- (a) Place the cassette in your player with side A uppermost.

- (b) Rewind the tape to the beginning of side A.

- (c) Type RUN "MM" and press RETURN,

If you get stuck, read your Amstrad User Instructions.

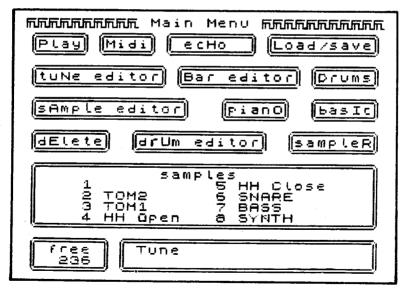

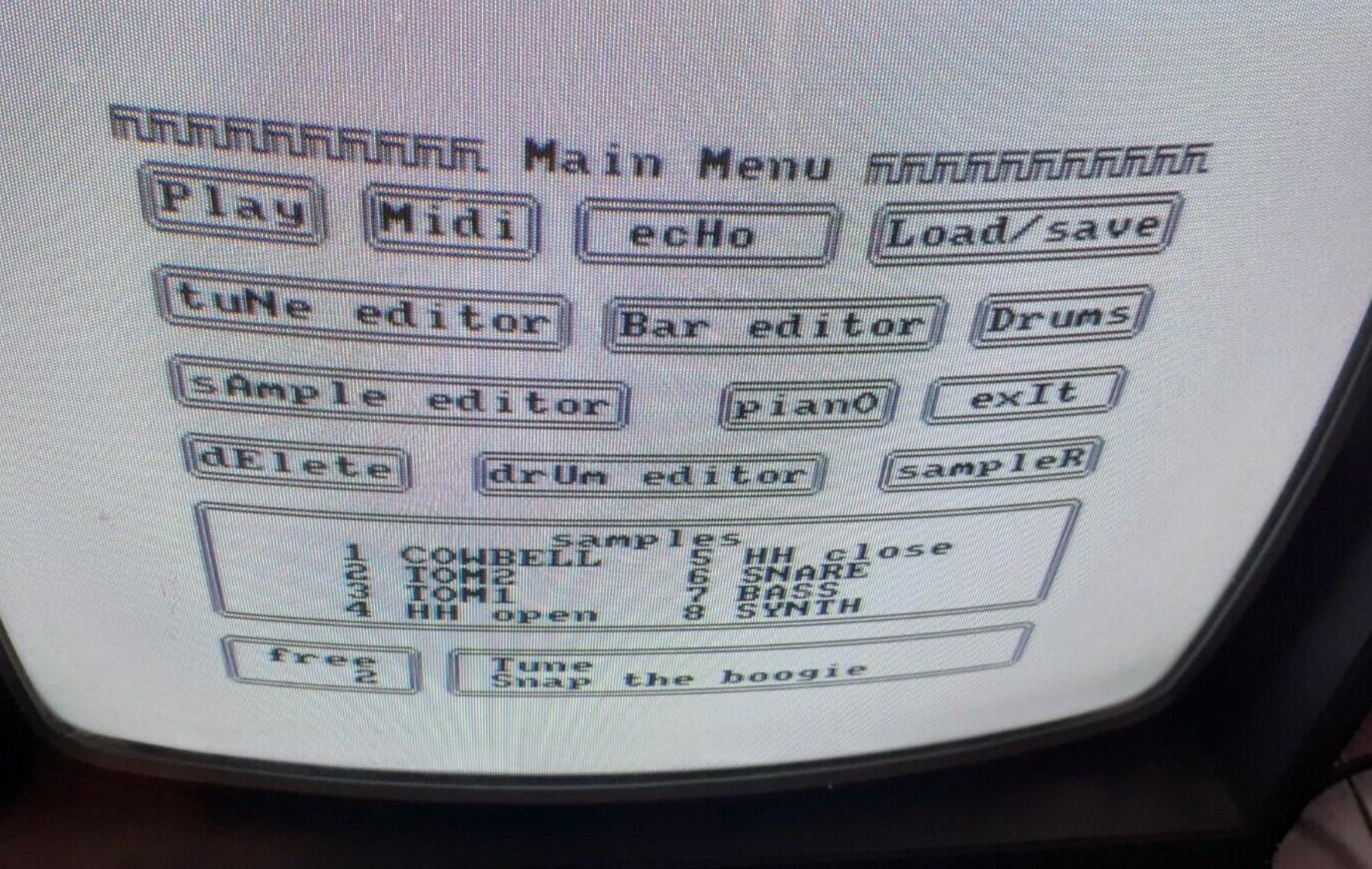

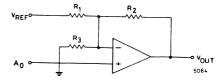

If you see The Music Machine title screen appear on your monitor, you will know that all is well. You should wait several minutes for the main program to load after which you will see the Main Menu screen shown in Figure 2.

(If you cannot get either the title screen or the Main Menu to load, do not despair. Just wind the tape back to the beginning, and try to load the program again. See your User Instructions for more help.)

Figure 2, First screen of Main program. Main Menu

# Disk loading

Insert the disk with side A uppermost, type RUN "MM" and press RETURN. The program will load and run automatically in about 20 seconds.

# 3. GETTING STARTED QUICKLY

Now that you've got everything plugged together, you probably want to start making sounds, playing songs, and playing the drums straight away.

That's what this Chapter is for. When you've tried all the things described here, you can spend a bit of time later on reading the detailed descriptions of what The Machine can do in Chapter 4.

So you are all plugged in and the software has loaded and looks like Figure 2? Good.

## 3.1 Playing the sounds, rhythms, and songs supplied

The way in which you make selections from the menu screens is to press the key on the Amstrad keyboard associated with the capital letter shown in the panel you want to choose.

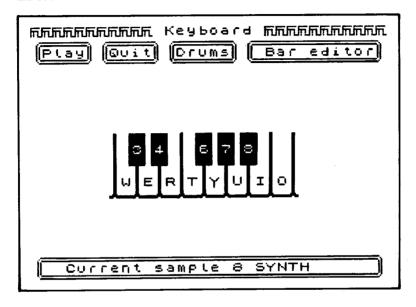

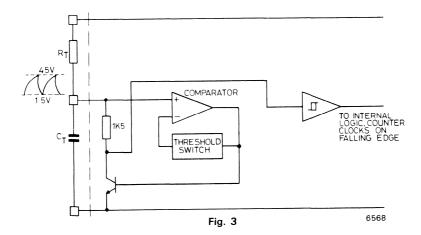

Example: If you want to play the piano, simply press 'O'. Try that now. The screen will look like that shown in Figure 3.

To get back to the Main Menu straight away, simply press 'Q' for Quit. Try that now.

#### Playing the tune:

Select 'Play' (by pressing 'P') and you will hear the tune whose name is shown in the panel at the bottom of the screen.

(What, no sound? Perhaps you have forgotten to turn up the volume on your amplifier, or maybe you haven't connected the leads properly?)

You can play the tune supplied with the software through your computer's internal programmable sound generator (psg). To do this, select 'M' from the Main Menu, key '9', then 'P' for Play. Adjust the computer's volume control to the level you want. You

can also play the drum rhythm through the psg, by keying '8' then 'P' for Play. The sounds produced by the psg are pre-selected and cannot be altered. They sound very different to the voices produced by the Music Machine. To interrupt a tune or rhythm, press ESCAPE.

Figure 3, The Piano Keyboard

#### Playing the piano:

Select 'pianO' and the screen will change to the one you've already seen in Figure 3. The numbers and letters shown on the screen correspond to the notes that you can play from the Amstrad's keyboard.

Press some of the 'musical' keys. Doesn't sound much like a piano, does it? That's because you are actually playing one of the sample voices which makes the sound called 'Synth' every time you press a key. We'll tell you how to make your own musical-instrument sounds later on.

## Changing the sound:

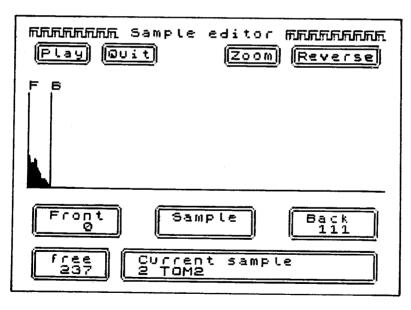

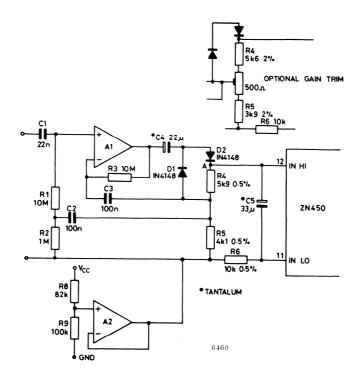

Before we record some new sound effects, let's change the sound that the 'piano' plays. Select 'Quit', and from the Main Menu select 'sAmple editor'.

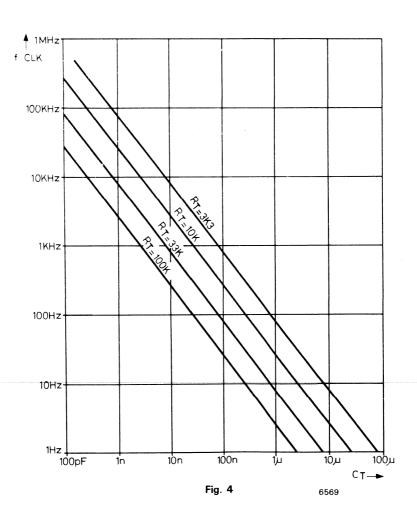

What you are now looking at is the waveform of the sound that plays 'Synth'. This is shown in Figure 4. Don't worry about this screen too much because we'll tell you more about it in Chapter 4. Whilst you're here, you might as well press 'Play' again just to see that you can hear the sound from more than one screen.

Select 'Current sample' and you will see that the title in the bottom panel clears and a red flashing cursor appears to prompt you for an input.

Figure 4, The Sample Editor

Type '7' and press ENTER. The bottom panel will now read '7 Bass'. Note that this is one of the sample sounds listed in the big panel on the Main Menu screen. Press 'Play' again and listen. See how easy it is to change instruments!

Return to the Main Menu by selecting 'Quit', and then go to the 'pianO' screen. Press a few of the 'keyboard' keys on your Amstrad and listen to the difference. 'Quit' back to the Main Menu and select 'Play' before you go on to the next exciting instalment.

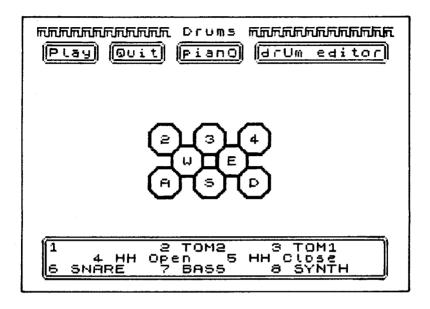

### Playing the drums:

From the Main Menu, select 'Drums'. The screen will look like that shown in Figure 5. If you want to hear the rhythm that we have supplied, you must ensure that the drum channel, rather than the music channel, is selected on the Midi screen. To do this, 'Quit' to the Main Menu, select 'Midi', and then key '4' to redirect the output to the earphone and phono sockets. 'Quit' back to the Main Menu and just select 'Play'. If you want to tap out your own rhythm, select 'Drums' then press the keys on the Amstrad's keyboard that are shown on the screen. (To stop the rhythm playing, press ESCAPE.)

Want to change the drum sound? Well you can either play all the eight sounds that correspond to the keys shown in Figure 5, or you can make a new sound. Because this is a bit more complicated, we'll describe how to do it in a moment.

#### Echo and reverberation:

The echo effect is created by a delay that's adjustable from one thousandth of a second to around one whole second. How much you can delay the sound depends on how many different samples you've already got stored in your computer.

If this is the first time you have loaded the software, you will have automatically loaded a full set of sounds and you will have to make a bit of room for the echo. This is done by deleting one or more samples. (Don't worry – they're still on the tape or disk, so you

won't lose them forever.) Select 'Quit' then 'dElete'. Press 1, to delete one sample, and when asked "Which sample?", type in '6' and press ENTER. You have now made room for your echo.

Figure 5, The Drum Machine

'Quit' back to the Main Menu and select 'ecHo'. Press'Play' and as you speak into the microphone, what comes out of the amplifier is exactly the same, but delayed! You will get even more extreme effects if the volume control of your amplifier is turned up, because the sound from the amplifier is then mixed in and delayed too. You can make some quite startling sounds using this technique, but don't turn the volume up too loud or you'll get feedback howls.

# 3.2 Some quick experiments for making your own sounds

You plugged the microphone in some time ago and have so far used it to delay your voice; let's use it creatively now.

We mentioned earlier that you can capture your own sounds and play them back in a sort of musical way through The Music Machine. Any sound that can be picked up strongly enough by the microphone (as long as that sound is not too long) can form the basis of your works of art.

We will give you some simple examples of how this is done now, but read Chapter 4 if you want some more detailed information.

# Capturing a sample

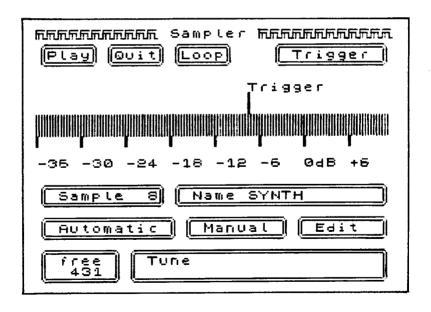

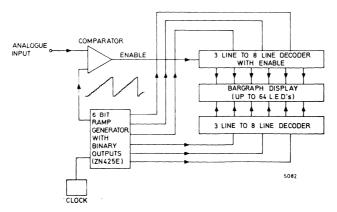

From the Main Menu, select 'sampleR'. You will see the screen shown in Figure 6. It might look complicated, but it is really very simple. Notice how the coloured bar resembles the recording-level display on most modern hi-fi cassette decks. Well, that's exactly what it is - a level meter.

Figure 6, The Sampler

When you are using the microphone with The Machine to capture noises (just like a recording), the level meter of the sampler will respond to the loudness of the noise.

Try this. With the 'Manual' panel on the Sampler screen highlighted, say a few words into the microphone and see how the level meter moves from left to right. The louder you speak, the further right the meter moves.

If you have to shout in order to get the meter to read higher than the point marked 'Trigger', you should adjust the slider on top of The Music Machine's case (see Figure 1 to see where this slider is positioned). You have found the ideal position for the slider when, as you speak into the microphone, the screen level meter just goes into the red bar (marked 0dB and above).

OK, when you've set the level of the slider so that the meter just goes into the red bar when you speak, we can capture your voice. This can be done manually or automatically, but we'll do a quick example automatically now and explain more in Chapter 4.

So that you can experiment with several sounds, you should delete all those that are currently stored in your computer. So select 'Quit', then 'dElete', and then '2'. (Remember that you can always reload the original sounds from the tape or disk.) 'Quit' back to the Main Menu, and select 'sampleR' again.

Choose 'Automatic', and repeat "This is me" into the microphone.

As soon as the volume of your voice gets loud enough to cause the level meter to go over half-way into the yellow bar, press 'Trigger' and what you say will be captured automatically. What is happening is that the volume of your voice, when sufficiently loud, will trigger The Machine.

Until you get used to the level meter, you might have to try capturing your voice two or three times before you get it right. Don't worry though, you'll quickly get the hang of it.

So that you know which sample is your voice, select 'Name', and when you see the red flashing cursor, type in "My voice" and press ENTER.

Select 'Play' in order to hear what you sound like inside a computer!

Now that you have a new sample you can 'Quit' back to the main menu, and play the Amstrad 'piano' keyboard to produce your new sounds.

Note that you can alter the position of the Trigger point with respect to the bar meter by moving it left and right with the cursor keys. This lets you control the level at which the automatic trigger occurs.

What other handy short sounds can you capture conveniently? How about a snippet from the radio, or a raspberry?

OK, that's the easy stuff done with. Now we are really going to show you how to make the best use of The Music Machine. The next chapter explains how to capture and edit your own sounds, and then build them into your own songs, tunes and rhythms.

We will show you everything that The Machine and the software can do but, because it is so powerful, we might use words or phrases that are new to you. Wherever possible, we will describe what we mean so that you'll understand. Even if you've never composed any music or rhythms before, we'll be very surprised if you still haven't after reading the next chapter and experimenting with The Music Machine.

#### 4. DETAILED DESCRIPTIONS OF WHAT DOES WHAT

In this chapter, we have assumed that you have already read chapters 2 and 3, and that you are familiar with the simpler things that The Music Machine and its software can do. If you haven't read these parts of the manual, we recommend that you do so now. Thank you.

#### 4.1 Playing using the Amstrad keyboard

'pianO'

On selecting 'pianO' from the Main Menu, the system behaves as a simple monophonic (single voice) synthesiser. Pressing any of the appropriate keys from the keyboard screen will play the currently selected sample (indicated in the panel at the foot of the screen).

If you want to change the voice that is played by the 'piano', then simply select 'Current sample' and, when prompted by the red flashing cursor, enter the number of the voice you want to use and press ENTER. Press one of the "musical" keys to hear the sound. (Note that the music channel must have been selected from the Midi screen in order to listen to the audio output from The Machine: see the next paragraph.)

A directory of the available voices is shown on the Main Menu screen.

'Play'

Once you have composed a song, you can play it from more than one screen. You will probably play the song most often from either the Main Menu or the Tune Editor screens, it doesn't matter which. (Note that you can only play the displayed bars from the Tune editor.)

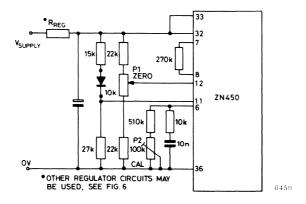

You must direct the music or drum output to the 'Ear' channel from the Midi screen if you want to listen to compositions through either the earphone socket or an amplifier connected to the phono output. This is simply done by selecting 'Midi', and keying either '4' or '7' according to whether you want to hear drums or music. You can also play the drums or music through the Amstrad's programmable sound generator (psg) by selecting '8' or '9' respectively. Note that the sounds from the psg will sound nothing like those generated by the Music Machine.

#### 4.1.1 The Bar Editor

In the context of The Music Machine, the difference between a bar and a tune is as follows:-

Bar: this is a sub-set of a tune. In other words, a tune comprises one or more bars. Obviously enough, you use the Bar Editor to compose a short piece of music.

Tune: this is a compilation of separate bars. Once you have composed a number of bars, you can string them together in any order you want, using the Tune Editor, to form your song.

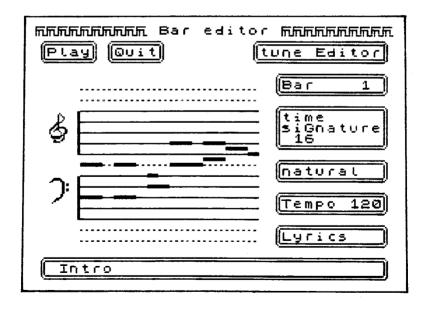

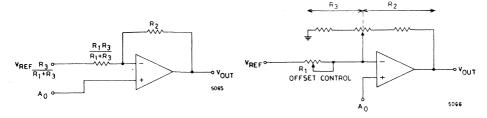

Figure 7, The Bar Editor

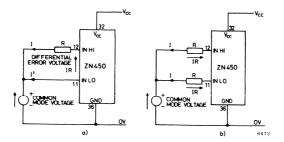

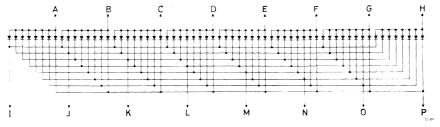

Select the 'Bar editor' from the Main Menu and you will see the screen shown in Figure 7. The major part of the screen is set aside for your music composition and consists of a conventional pair of staves for treble and bass clefs. (Each stave is set of horizontal parallel lines; the upper is called the treble clef, and the lower is called the bass clef.)

## 'Time Signature' and 'Tempo'

You may change the Time Signature and the Tempo of the music at any time, but note that any bar already displayed on the screen will be lost if you change the time signature after the music is composed. The time signature dictates the number of beats to the bar and may have a value of 16 or less whilst the Tempo indicates the rate at which the bar is played. The figure associated with the tempo is the number of beats per minute and may be any value in the range of 60 to 240.

If you want to plant sixteen notes on a stave, then you should select a time signature of sixteen; you will then have one complete bar for every sixteen notes. Or, if the signature is eight, you will be able to play eight notes to the bar.

### Entering music

The way in which you enter music is illustrated in the following example. Because the software with which we supply you already has bars and tunes built into it, we shall edit the supplied tune which is called "Snap the Boogie".

# Sharps and flats

'Quit', then select the 'Bar editor'. You will see the first bar of the song displayed. The black rectangles on the staves each represent a note. The notes may be natural (white notes on a piano), or sharps and flats (the black notes). If a note is sharp, then a '#' is displayed at the top or bottom of the stave nearest to that note. Notes entered as sharps are denoted by a '#' sign whereas flats are shown either as naturals or sharps. An example of this is B-flat which is actually displayed as A-sharp; see below.

Try this. Make the second note sharp by firstly keying 's' (to alter the box showing 'natural'), moving the cursor to the note, and pressing the space bar, backspacing and then pressing the space bar again. Change the third note to a flat by repeating the above process except for pressing 'f' for flat instead of 's' for sharp. You will notice that if you call for a sharp or a flat note that doesn't actually exist in musical terms (for example, there is no such thing as 'C flat'), the Music Machine software will select the appropriate natural note or semitone.

Whenever you press the space bar, you either plant a note at the cursor position or you remove one. Because the Amstrad Music Machine is a one-voice synthesiser, you can only play one note at a time. However, it can act as a two-voice device when driving MIDI. Thus, you can have two notes aligned vertically on the staves. If you attempt to enter a third note, the one nearest to it will disappear automatically. You can nevertheless, play two notes simultaneously on the internal Amstrad sound chip.

#### Changing bars

Experiment with the bar editor by moving notes around the staves; select 'Play' from time-to-time to see what your composition sounds like. When you have completely ruined the first bar, select 'Bar' and, when prompted, key in the number of another bar and press ENTER.

## Changing the lyrics

Select 'Lyrics' and when prompted by the red flashing cursor, enter a name for the bar. When you come to compile your song, the bar number and the first part of the lyric name will be displayed in a screen panel. If you use lyrics that remind you of the music in that particular bar, you will find it easier to assemble your song; this will be illustrated with an example in a moment.

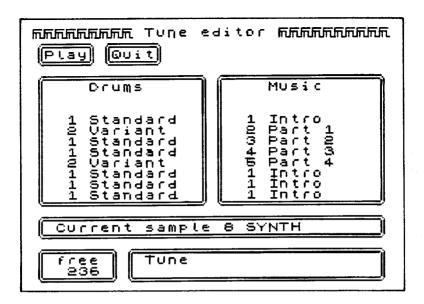

#### 4.1.2 The Tune Editor

Select 'tuNe editor' from the Main Menu and you will see the screen

shown in Figure 8. This editor is not nearly as complicated as the Bar Editor. All you need do with this screen is construct a list of numbers.

Each number and name represents a bar that you have already composed. To make a song, you simply string together bars in the order that you want.

As an example, we can compose a variation of the song "Snap the Boogie" that is supplied with the software, just by re-ordering the bars and adding the new bar that we ruined - sorry, composed - in section 4.1.1.

Drum rhythm bars are assembled in the left-hand panel, and music bars in the right-hand one. Move the cursor right, to the music tune editor, and then scroll through the music using the up and down cursor keys. Overtype at the cursor position to replace a few bar numbers and watch how a handful of letters of the lyric are displayed to remind you of what the bars are. If you want to insert new bar numbers, just press ENTER (bar number 1 will then be inserted by default) and add the number you want.

To change the voice, select 'Current sample' and enter the new voice number. To edit the tune name, select 'Tune' and enter the new name.

If you select 'Play' from the Drum editor screen, you can only play the displayed bar and not the whole rhythm sequence (composed from lots of bars); the whole is playable from the Tune editor. Whether music or drums play when you select 'P' depends on which side of the screen the cursor is displayed. Move between music and drums using the cursor left and right keys.

The number in the 'free' panel indicates the amount of space you have available for composing your tunes.

If you want to interrupt a song whilst it is playing, press ESCAPE.

Figure 8, The Tune Editor

## 4.2 The Drum Machine

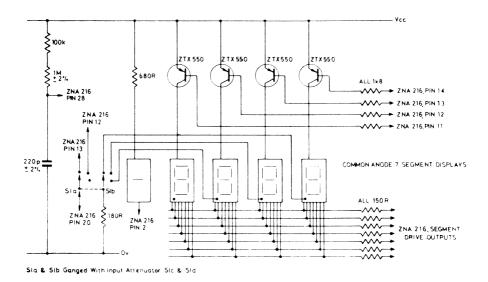

On selecting 'Drums' from the Main Menu, you will see the screen shown in Figure 5. Pressing the appropriate keys on the Amstrad keyboard will result in the sounds listed in the bottom panel of the screen being played.

The relationship between the keys and the number of the sound is a function of their physical positions:

| Amstrad Key | Sound Number |

|-------------|--------------|

| 2           | 1            |

| 4           | 3            |

| E           | 5            |

| S           | 7            |

| Amstrad Key  | Sound Number |

|--------------|--------------|

| 3            | 2            |

| $\mathbf{W}$ | 4            |

| A            | 6            |

| D            | 8            |

Note that from the Drums screen, you can only play one drum sound at a time (but you still have eight sounds to choose from). However, it is possible to play any three sounds from these eight at the same time when using the drum editor to build a rhythm.

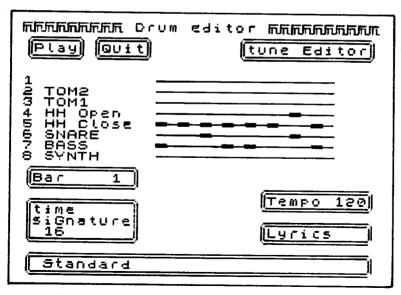

# 4.2.1 The Drum Rhythm Editor

When you select 'drUm editor' from the Main Menu, you are confronted with the screen shown in Figure 9. The column of numbers from 1 to 8 lists the memory-resident sound samples. If you load the software from the original cassette or disk, you will see listed the drum sounds supplied.

Figure 9, The Drum Editor

Writing your own rhythms is straightforward; wherever there is a beat planted on a horizontal line, then the sample associated with that line will sound when the rhythm is played. There are several similarities with the tune editor described in section 4.1.2 of this manual, and these are as follows:

The tempo may be changed to any value between 60 and 240 beats per minute. The lyrics editor enables you to describe each bar with a meaningful name. The time signature may have a value of 16 or less and denotes the number of beats per bar. The bar number panel is used both to create new bars and edit existing ones.

As an example of how to create a drum rhythm, first select a time signature of 16 and a slow tempo of 120 beats per minute. Insert a bass drum line of one drum beat every fourth space, starting with the first space, along the line. Add a sound like a hi-hat every second and third space. Add a tom-tom every fourth space starting with the third. Now add sounds that take your fancy elsewhere in the bar (but don't forget that you can only play three samples simultaneously). Now you can change the tempo to suit your mood.

Once you have composed several bars of different rhythms, you can use the tune editor to string them together and play them. If you have forgotten how to use the tune editor, read section 4.1.2 above.

### 4.3 Recording real-life sounds

Before you try the examples in this section of the manual, delete all of the resident samples. ('Quit', 'dElete', select '2'.)

The microphone supplied with the Music Machine can be used for capturing sounds from virtually any source. Both quiet and loud sounds can be captured; you will need to adjust the level control and maybe the distance of the microphone from the source to get the effect that you want.

Select 'sampleR' to bring up the screen shown in Figure 6. The level meter on this screen behaves in the same way as do bar meters on

modern cassette decks. The louder the sound source, the higher is the reading on the level meter.

You will find by experiment which combination of slider position (on the top of the Music Machine's case) and volume level of the source give the best results. Start by setting the slider to a position that corresponds to a screen reading averaging -6 dB; speaking into the microphone is probably the easiest way to experiment.

When you have found a suitable level, select 'Automatic', get ready to speak, press 'Trigger' and say "Testing testing". Press 'Play' to see what it sounds like.

(If the level is too low, you will not capture a sample because you will not have set off the automatic trigger. When a sample is being taken, the "Trigger" panel is high-lighted. The bar meter must reach approximately -6 dB before the Music Machine is triggered although this can be adjusted using the left/right cursor keys. On the other hand if, when you play the sample, it is very distorted then the slider control is set too high.)

The Manual control option on this screen enables you to capture a sample right from the moment that you press 'Trigger' and is useful if you want to record at a particular instant in time.

The 'Loop' option on this screen enables you to play a particular sample continuously. Once Loop is selected, anything you play from the 'piano' or MIDI screen will continue to sound until a key is released or note-off data is sent.

### 4.3.1 Editing captured sounds

When you capture a sound, that sample will fill all of the allocated free memory space. Assuming that you currently have no samples resident and, say, you want to capture a sound lasting 1000 milliseconds, then most of the free space will be taken. This is why the sample editor is provided.

Capture a sound (some speech, for example). Select 'Edit' and you will see the screen shown in Figure 4. The peaks in the displayed signal represent the captured sound. The horizontal sections of the display are most probably dead space. Edit out this dead space by moving the front cursor (F) with the cursor keys to the start of the rise. Play the sound to see what effect this has on the sample. Select 'B' and move the back cursor to the end of the fall, and you will now have sandwiched the useful part of the signal. Play it to ensure that you have eliminated the dead space.

Some signals, if truncated at a high signal level will sound "spitty" when played. This may be overcome by starting and stopping the sample at points where the spectrum is at or near the base-line. Because rapid variations in the signal level are difficult to spot when the spectrum is displayed normally, you can 'Zoom' into the part of the graph nearest the selected cursor (that is, either front or back) and examine it in close-up. You will then find it very much easier to truncate the signal at a minumum and thus avoid "spit".

You may play your sample backwards by invoking 'Reverse'.

The positions of the front and back cursors are expressed in terms of elapsed time in units of milliseconds (thousandths of a second). The "free" figure is also in milliseconds and gives you a measure of how much space you have left for other samples. You have in total about one and a quarter seconds at your disposal. This might not seem like very long, but bear in mind that realistic drum sounds can be made with samples less than one-tenth of a second long.

### 4.4 Playing using an external keyboard

To connect a MIDI (Musical Instrument Digital Interface) keyboard to the Music Machine, you should plug appropriate DIN cables into the MIDI-IN and MIDI-OUT ports of both devices. As you would expect, IN on one device should be connected to OUT on the other, and vice versa.

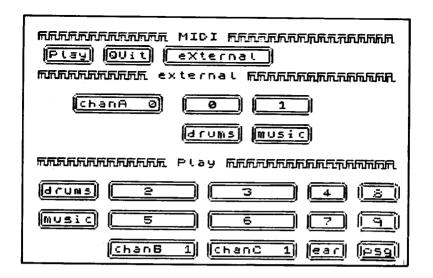

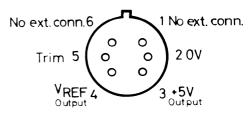

Figure 10, The Midi Screen

You are now free to do several things.

- (a) You may play any captured sample held in the Amstrad's memory from the MIDI keyboard over its full musical range.

- (b) You may send composed tunes to the MIDI synthesiser and play either the captured samples or any of the voices that your MIDI device might already hold, or both simultaneously.

- (c) Using the microphone, you may capture any of the MIDI keyboard's voices and edit them using the sample editor.

- (d) You may switch between voices on your MIDI keyboard to simulate different instruments.

- (e) Using a MIDI synthesiser, you may play two Music Machine notes simultaneously (whereas this can't be done directly from the computer's keyboard).

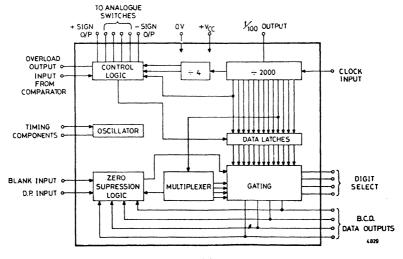

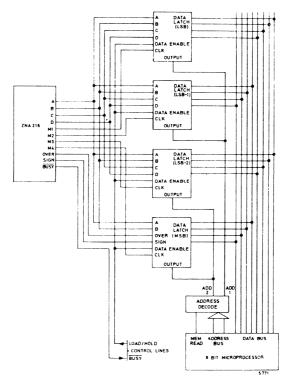

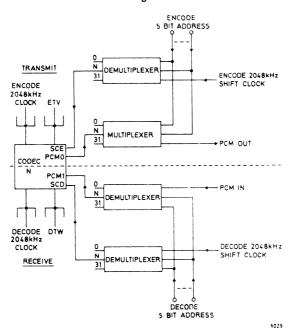

Figure 10 shows the MIDI screen. The important thing to note about this screen is that it is actually two screens in one; the top half is for external playing. In particular, the bottom half is relevant to what happens when data is sent to a particular output (whether this be drums or music sent to the ear/phono or MIDI sockets, or the Amstrad's internal psg).

Note that you can define which of the 16 MIDI channels both receive and transmit data. You have complete freedom over where you send the Music Machine's drum and musical signals. Channels A, B and C correspond to external drums or music, internal drums, and internal music respectively; each may be assigned to any MIDI channel.

Note that the software will not allow you to map both drums and music onto the earphone (or phono) outputs of The Music Machine. You can only play drums OR music through these outputs, and not both simultaneously. The same limitation applies to the Amstrad's internal psg. Please see section 4.4.2.

To allow a MIDI synthesiser to play a Music Machine voice, select the MIDI channel you want to use (channel zero is the 'omni' mode that can receive from all channels), and select 'eXternal'. If music is mapped onto the MIDI channel in the lower half of the MIDI screen (key 5 or 6), your synthesiser will play a resident sample. If drums are mapped onto the MIDI channel (key 2 or 3), the complete sample set will map onto consecutive sets of keys.

You might wish to play some pretty advanced musical compositions (using the MIDI keyboard), store them, edit them, and play them back later. At the moment, the software we supply takes up a great deal of the available RAM and we just have not had the space to provide you with these latter facilities. Please write and let us know what you want to do with your Music Machine and we will try to take account of your needs with future developments.

### 4.4.1 MIDI in, out and through

The MIDI-IN and MIDI-OUT sockets on The Music Machine conform to the MIDI standard. The MIDI-THROUGH socket is used for daisy-chaining devices that conform to the MIDI standard. The instructions supplied with whatever it is that you wish to connect should give you more information about assigning masters and slaves.

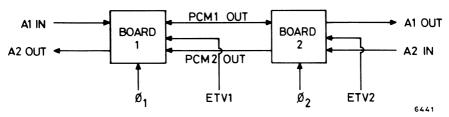

As The Music Machine conforms to the MIDI standard, you can of course connect up to 16 Amstrads together and orchestrate them!

If you are fortunate enough to own a MIDI sequencer, you can use this as the master device for controlling, say, an external keyboard, an external drum synth, AND your Music Machine. The world of MIDI is large and fairly complicated; without knowing what devices you are going to plug together, it is very difficult for us to provide you with detailed instructions. Suffice to say, whatever you are plugging in should come with its own instruction manual to help you.

### 4.4.2 Combining tunes and drums

You have just read that it is not possible to direct drum and music outputs to the headphone or phono sockets simultaneously. However, you can use your MIDI keyboard to play the music whilst The Music Machine plays the drum rhythm in synchronisation.

Channel selection is straightforward from the MIDI screen menu, and you can assign any of the sixteen channels to any stream you want.

### 4.5 The effects box; echo and reverberation

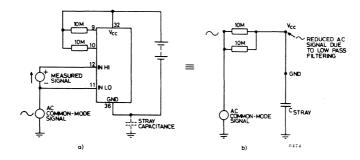

Echo and reverberation effects are generated via a simple variable delay line. You will hear markedly different effects by listening either through your headphones or an amplifier.

The length of the delay that you can use is dependent on the amount of free RAM; if you have stored a number of samples, there will be less

space to alot to the delay effect. To maximise the delay, you should delete all resident samples. The delay time is displayed in a screen panel in millliseconds.

Using headphones, you can faze yourself by trying to speak coherently into the microphone. Alternatively, with an amplifier and speakers connected, you will find that you can generate some pretty startling effects as the delayed signal is regenerated via the speakers and microphone. Be warned that at high sound levels, you can generate feedback howls.

By experimenting with the length of the delay, the microphone level slider, and the amplifier output volume, you should be able to produce a wide range of strange noises.

### 4.6 Recording and replaying your compositions

Loading and saving is an extremely simple affair. The options available to you on selecting 'Load/save' are self-explanatory.

You can save the data parts of the program either with the program or separately. The advantages of this are that you can load and save individual samples, sub-libraries of samples, individual tunes and sub-libraries of tunes to suit your particular needs. If you would rather, you can save all your samples and tunes together with the program so that when you next load the software, it is ready to run.

The program is smart enough to recognise whether what it is loading is samples or tunes, so you need not necessarily specify which. You may use the usual Amstrad "CHAIN" command if you cannot remember the name of what you want to load (tape only), or you can look for specific named files. If you are using disk, you can get a directory from the filing menu.

### 4.6.1. Cassette and Disk storage

If you have software on cassette you can transfer it to disk using the

Load/save option from within the program. To do this simply select Floppy from the menu and then option 4, enter a name as requested and then hit RETURN.

If you have not got a disk fitted you may choose to reduce the cassette loading time by saving the program without the loading screen. To do this follow the procedure above but do not select the Floppy option.

### 5. TECHNICAL SPECIFICATION OF THE MUSIC MACHINE

If you have some technical knowledge and machine code programming experience, you may well be interested in the contents of this chapter. (On the other hand, you might not want to know anything at all about the technicalities of The Music Machine - in which case you won't miss much by not reading this.)

### 5.1 Technical Spec.

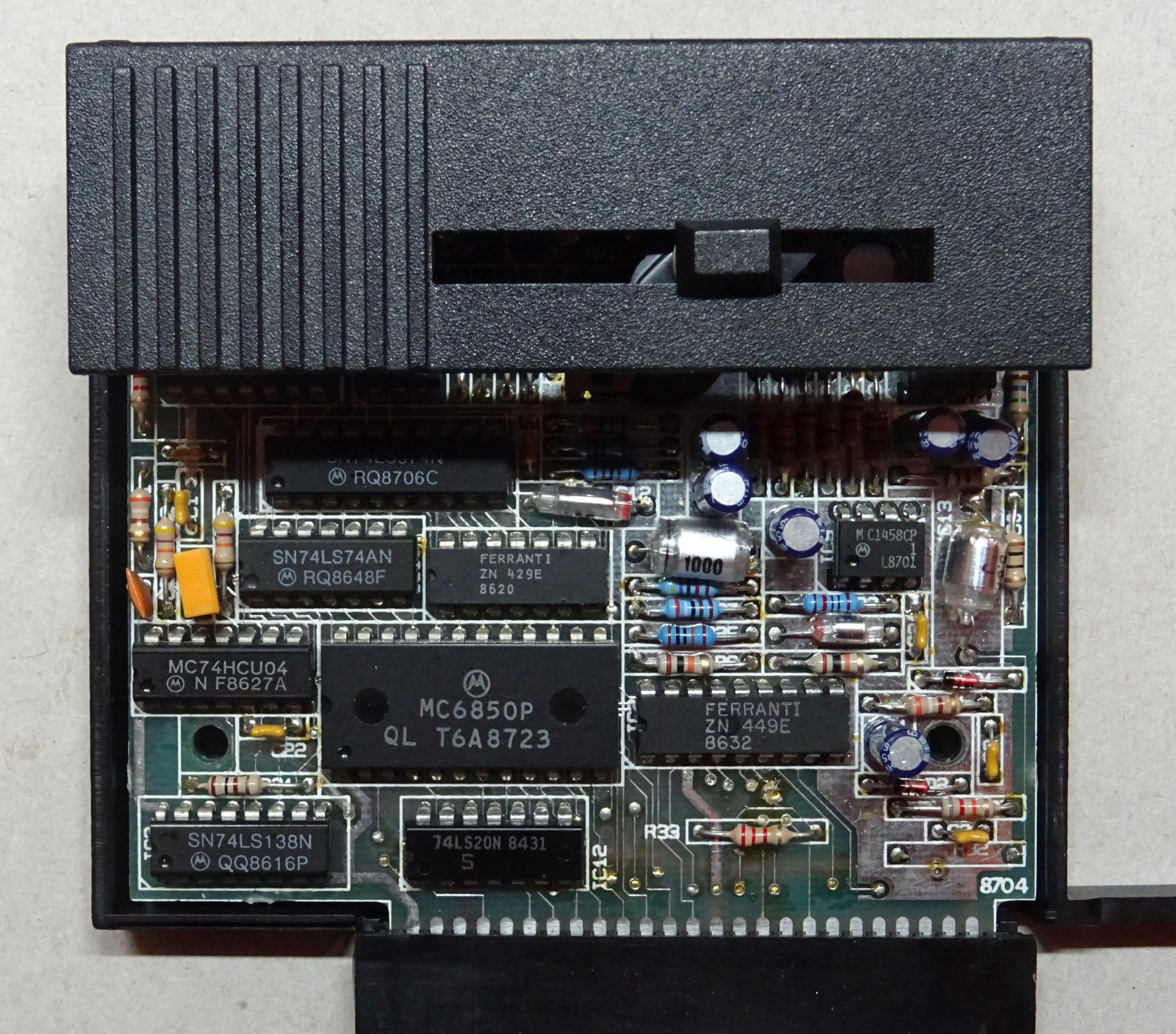

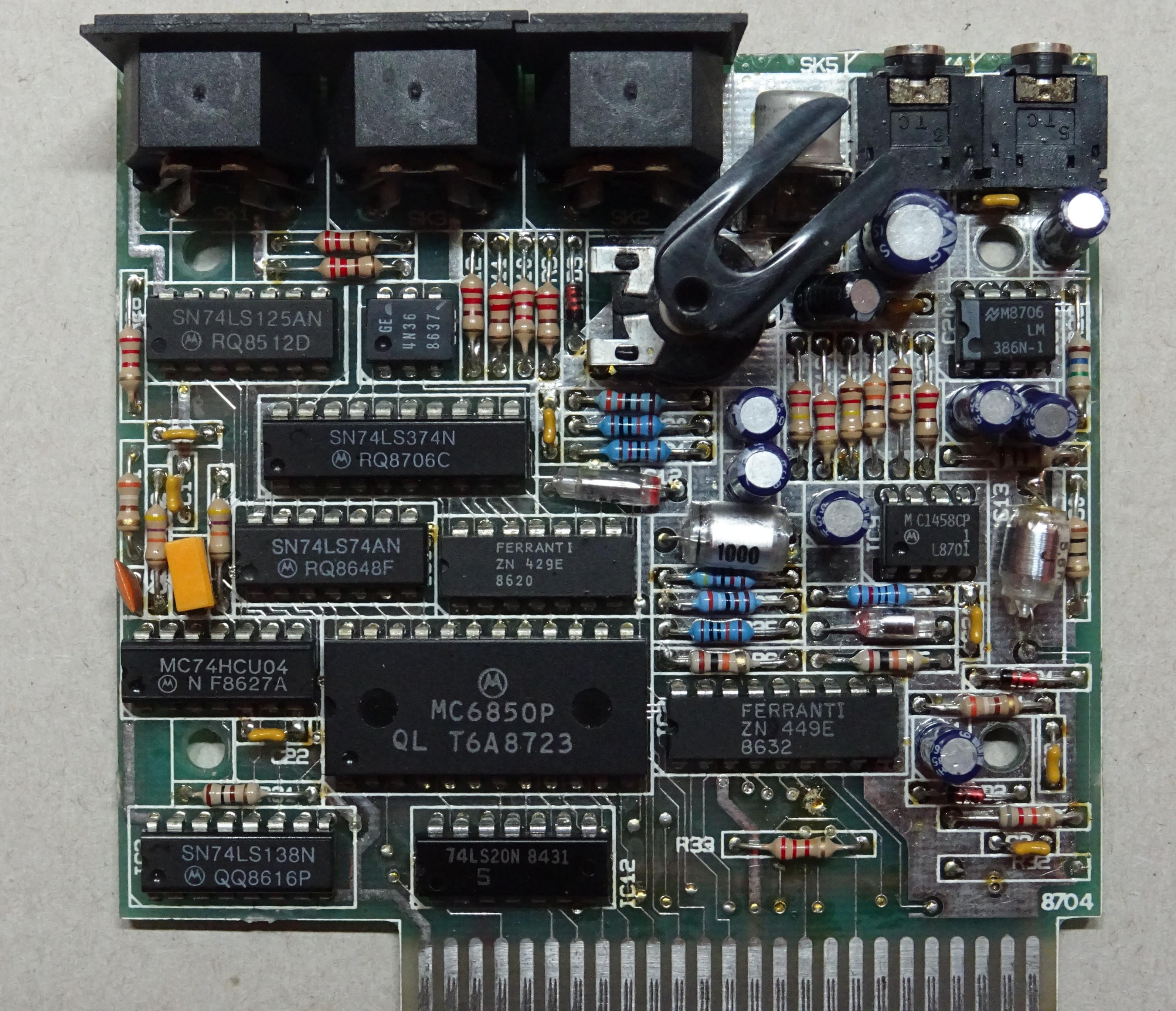

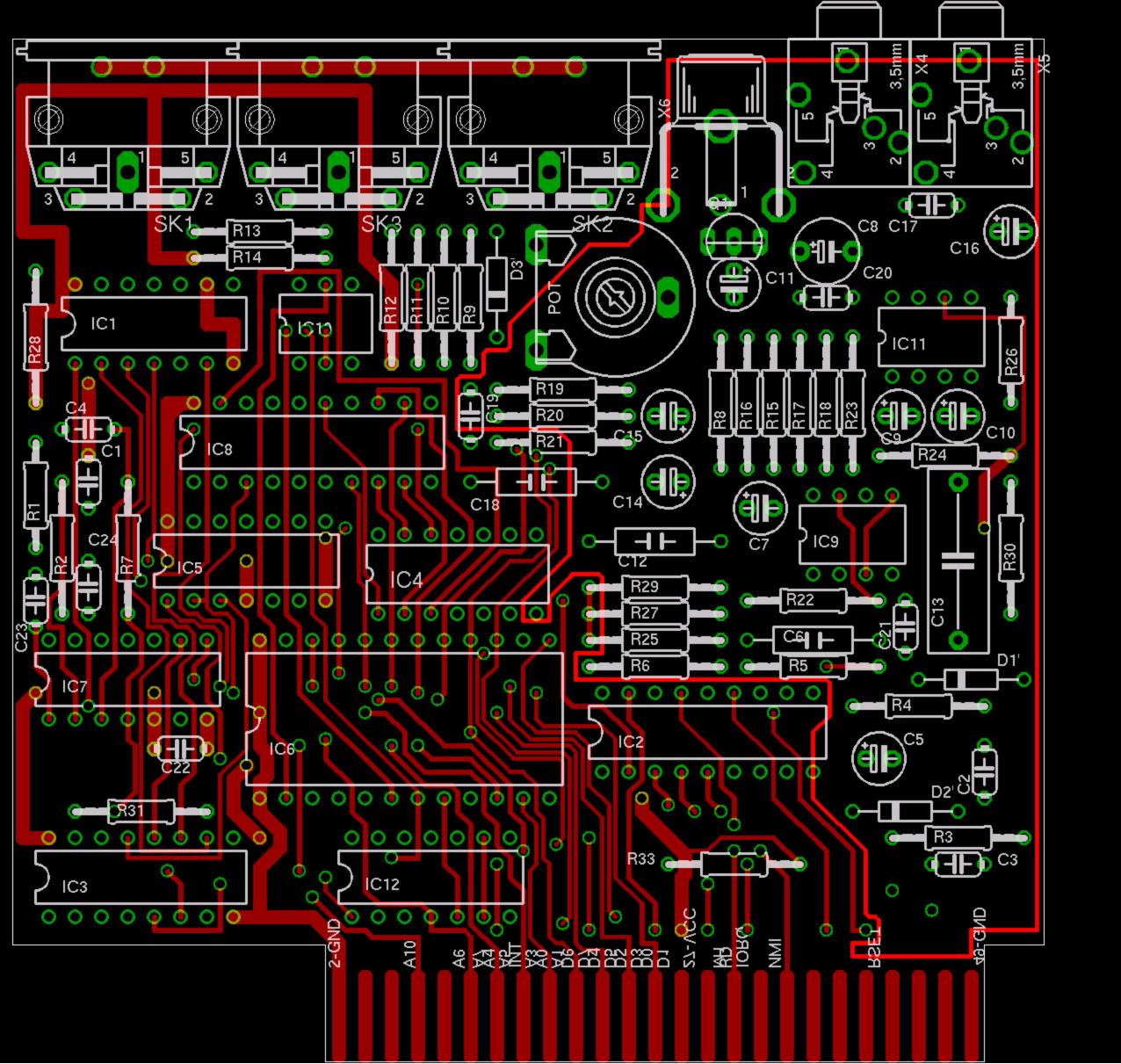

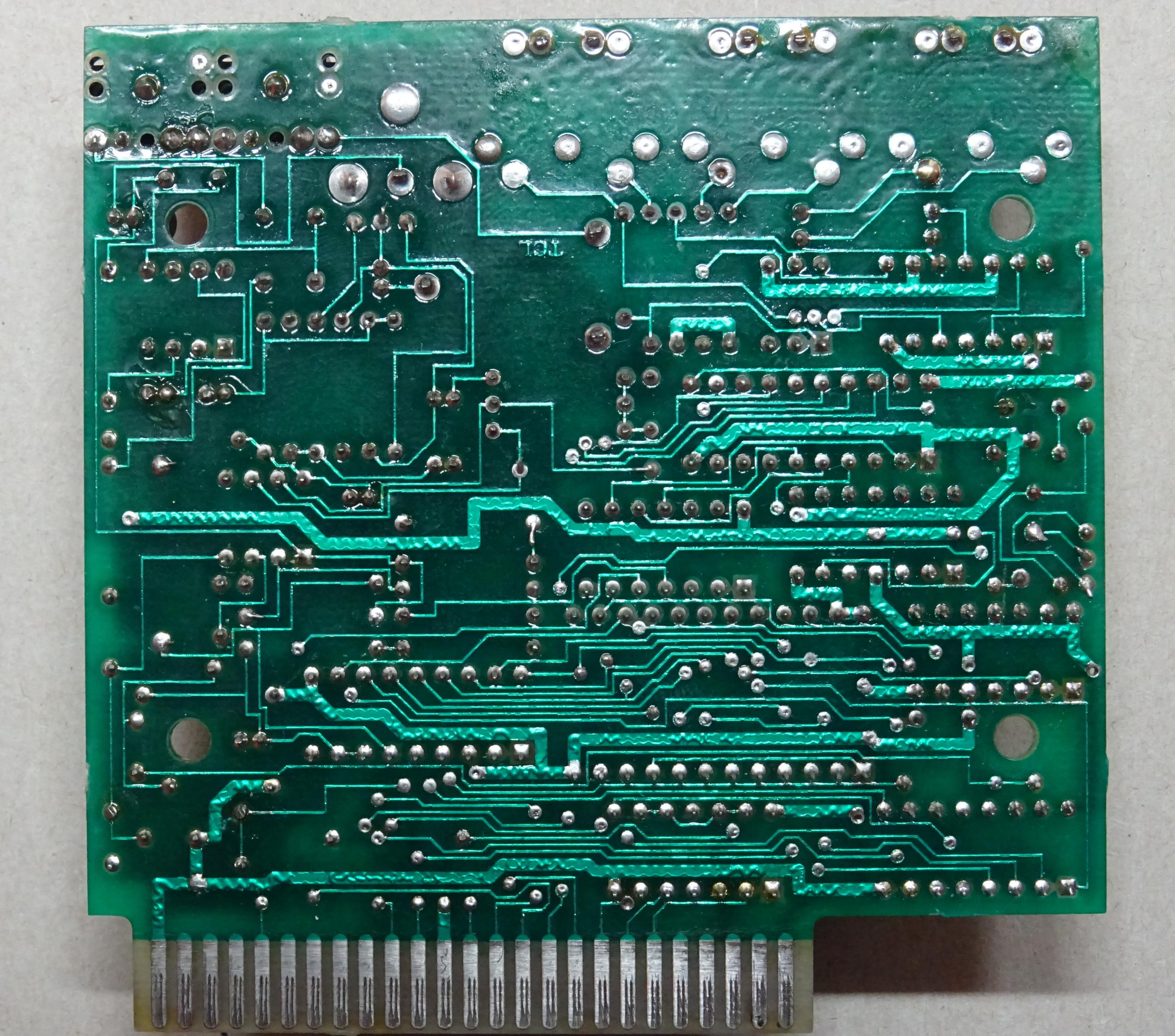

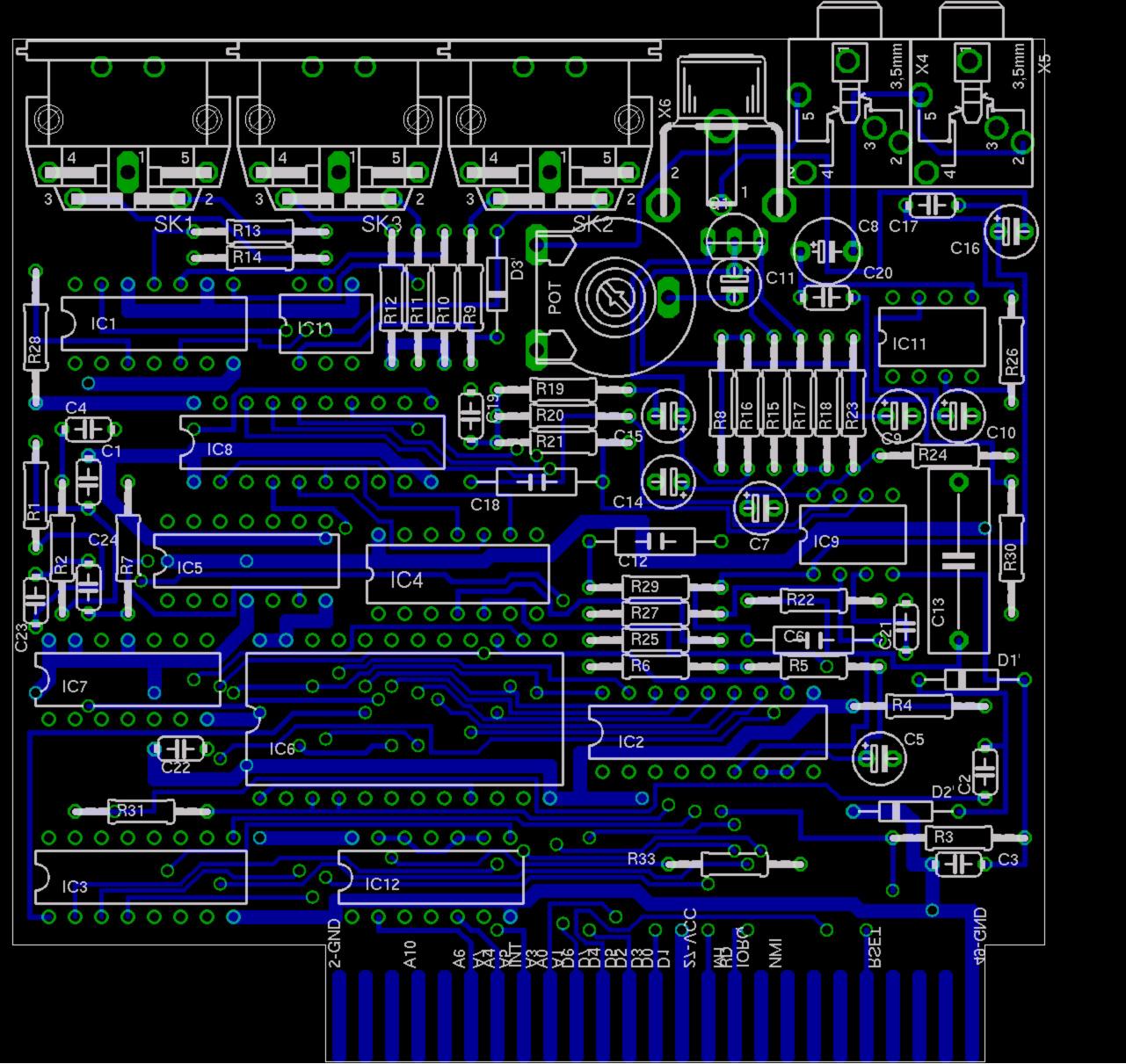

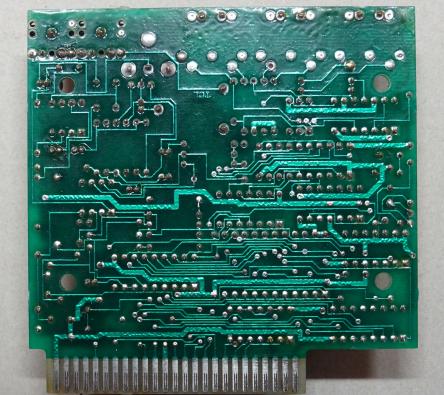

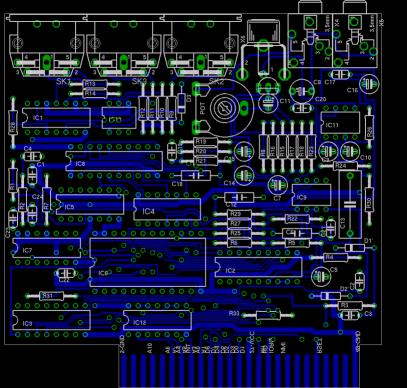

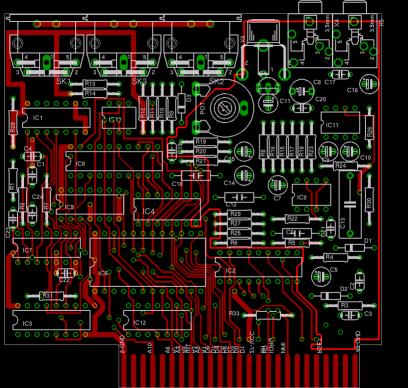

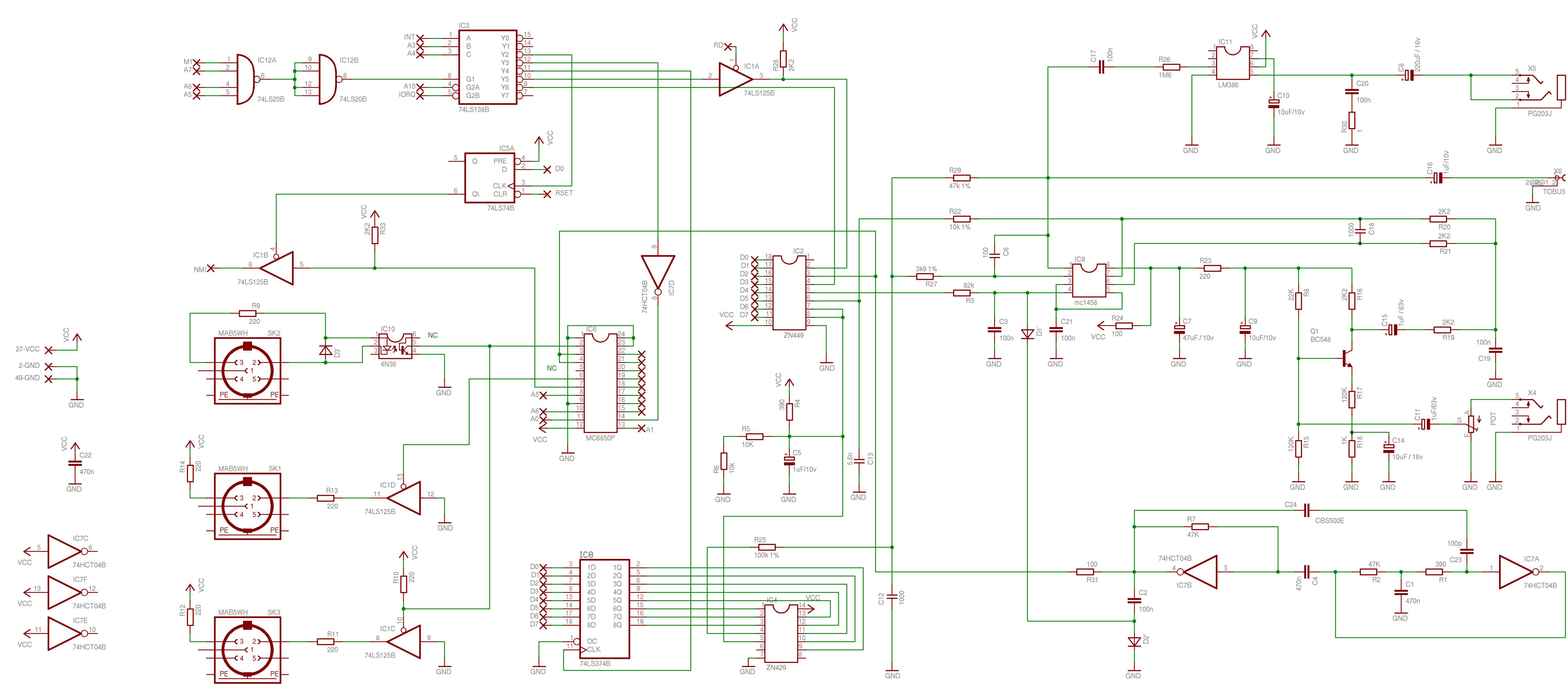

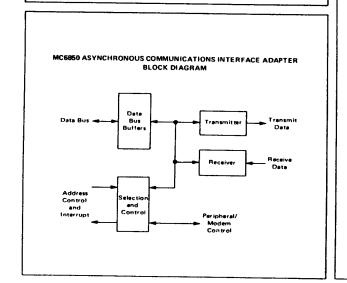

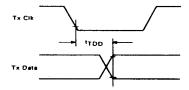

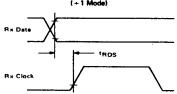

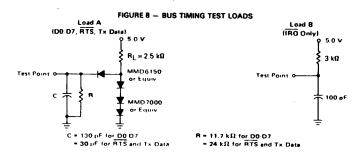

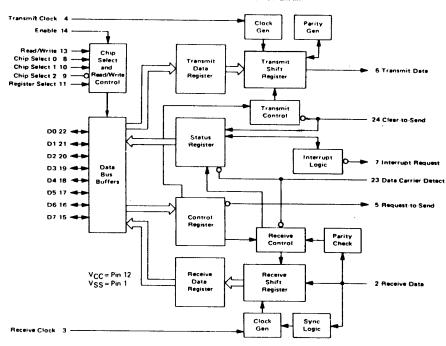

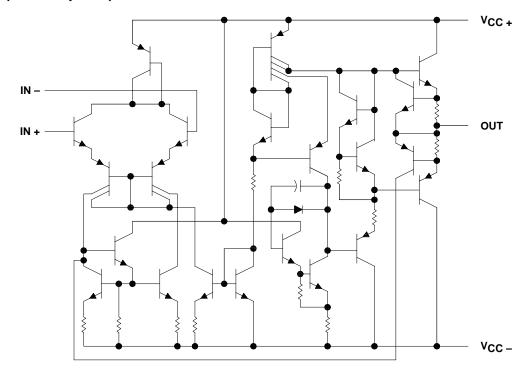

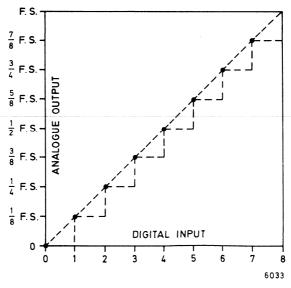

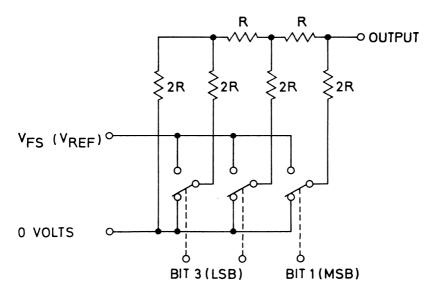

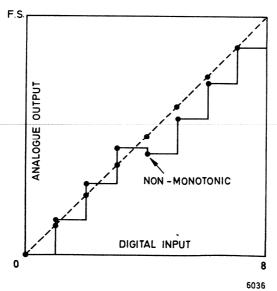

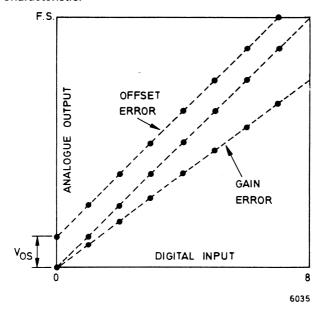

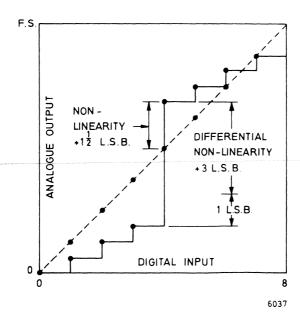

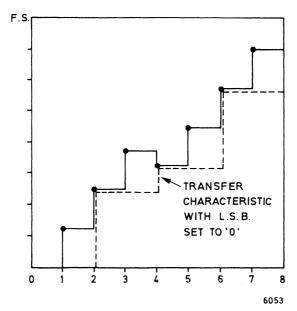

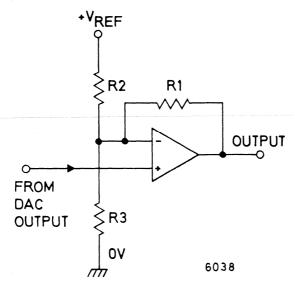

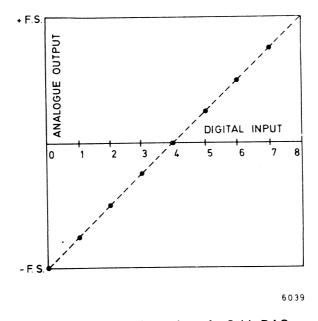

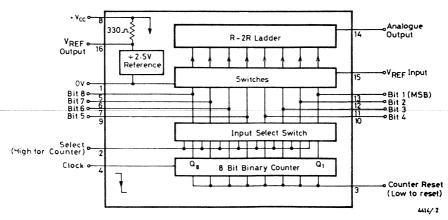

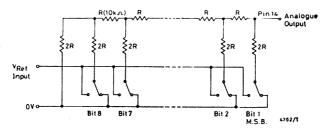

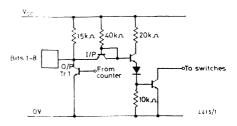

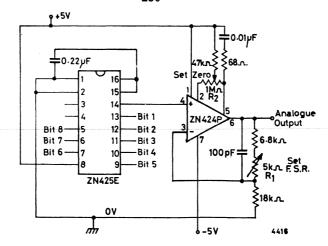

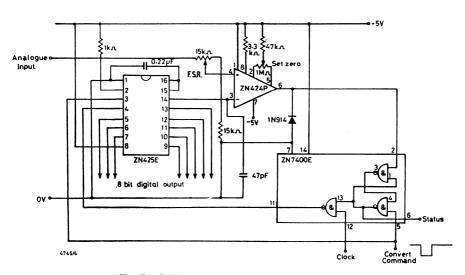

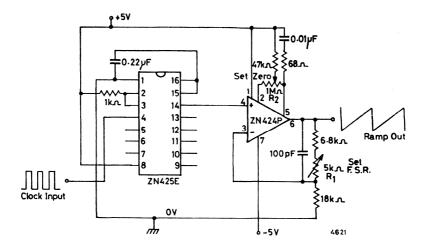

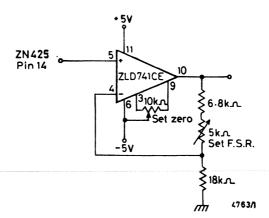

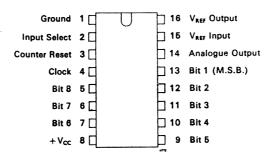

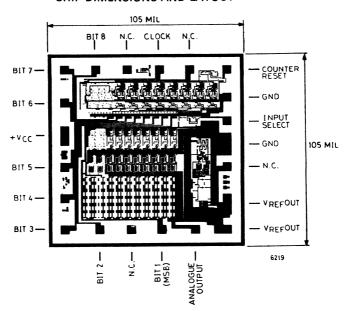

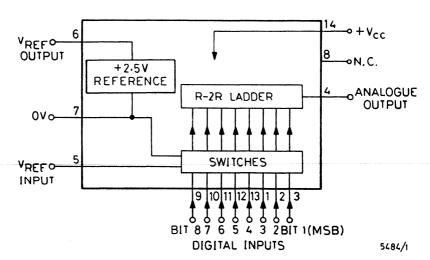

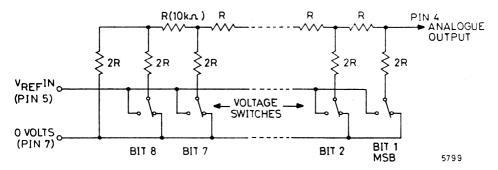

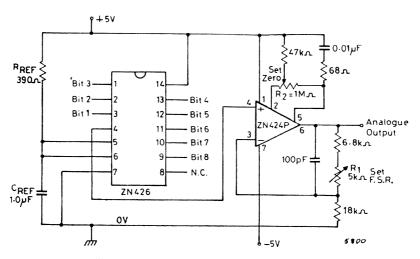

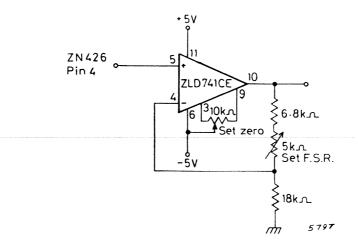

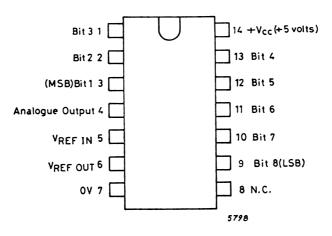

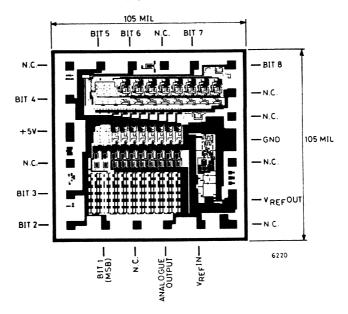

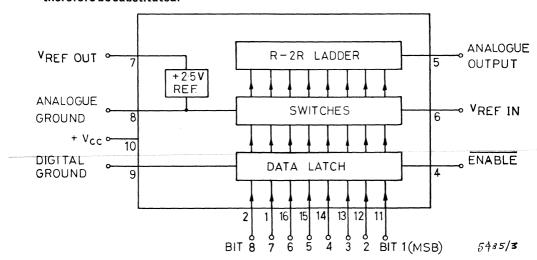

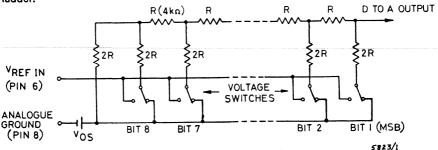

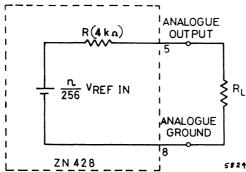

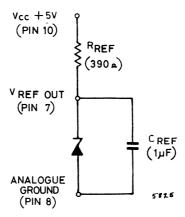

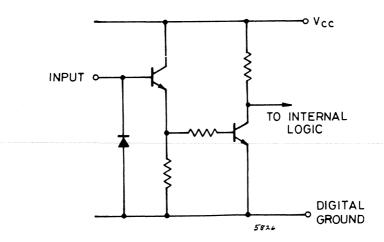

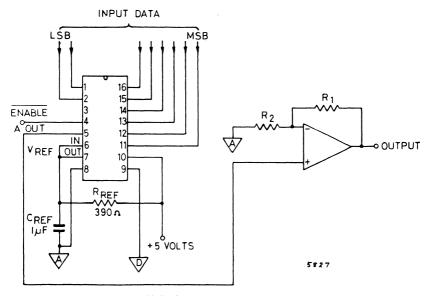

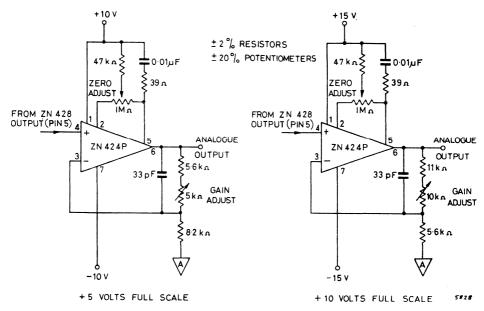

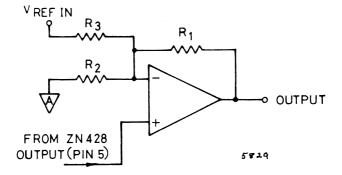

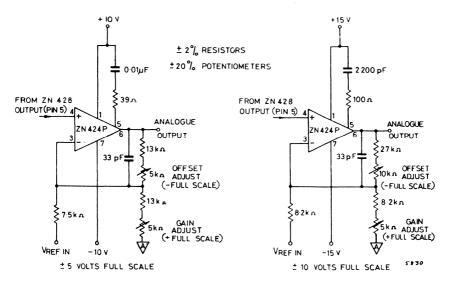

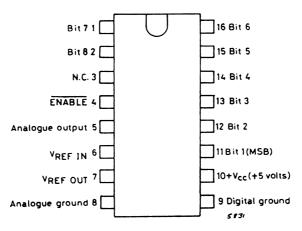

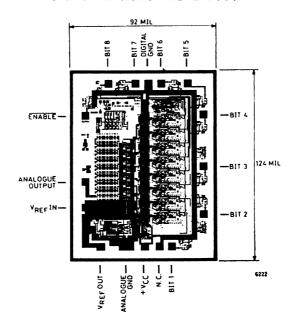

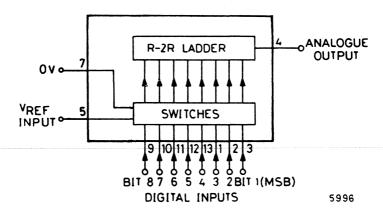

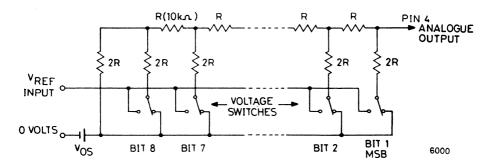

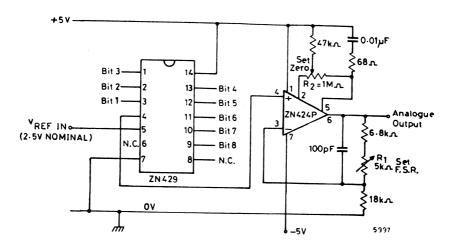

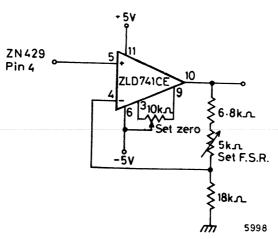

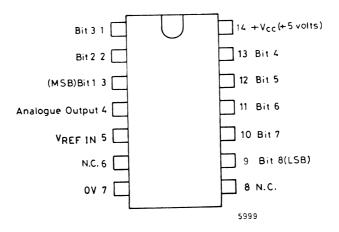

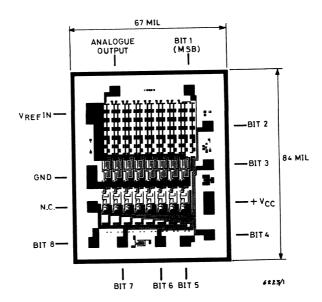

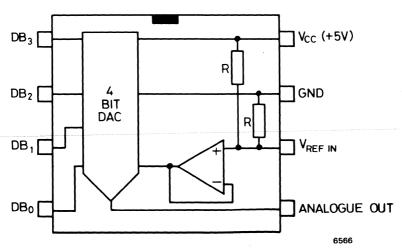

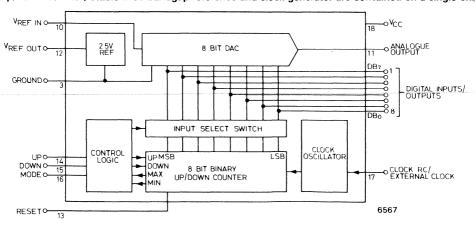

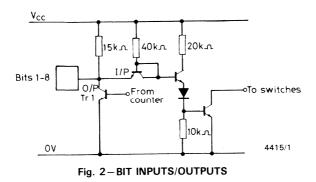

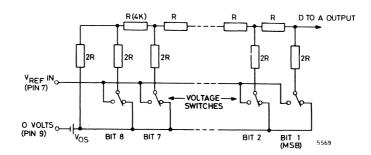

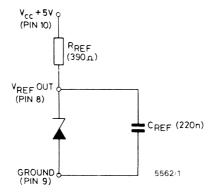

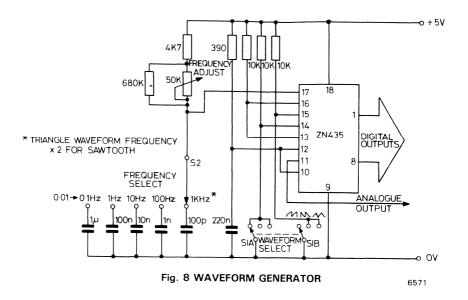

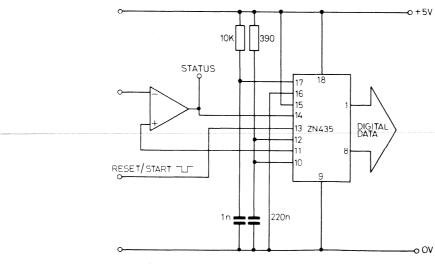

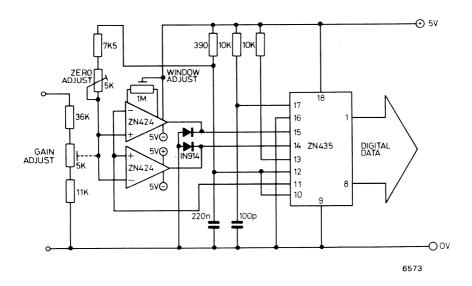

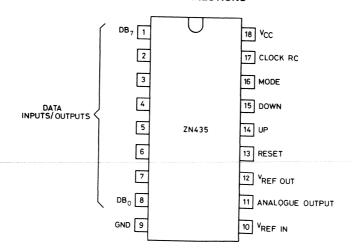

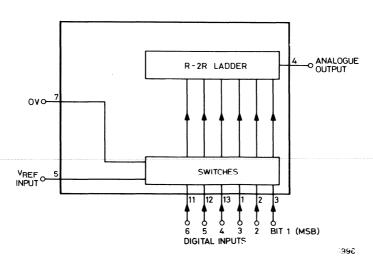

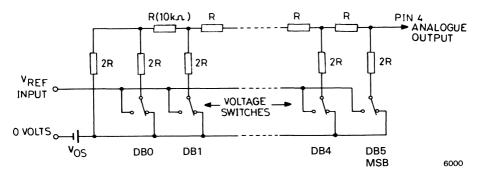

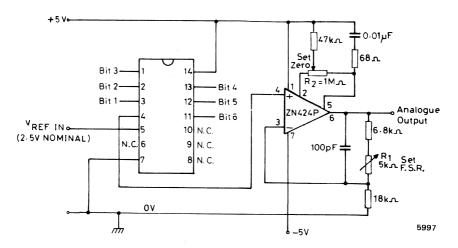

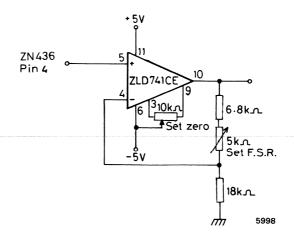

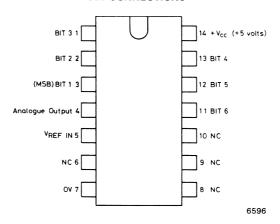

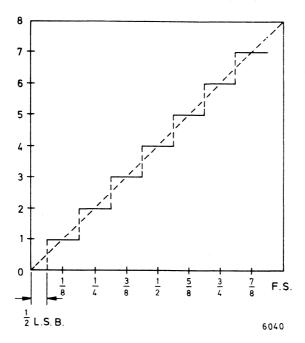

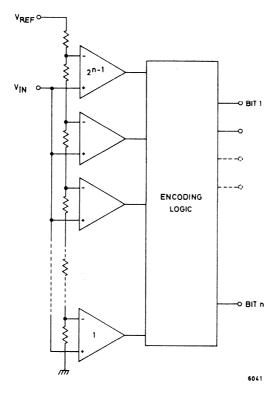

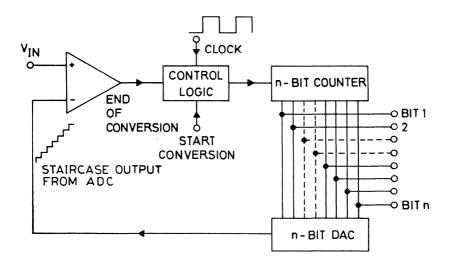

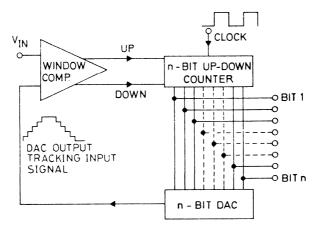

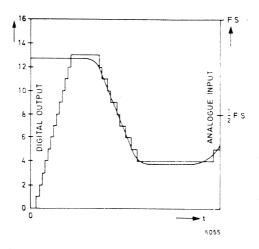

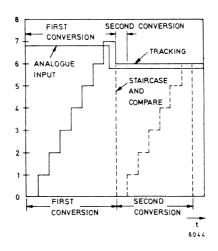

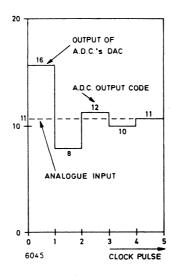

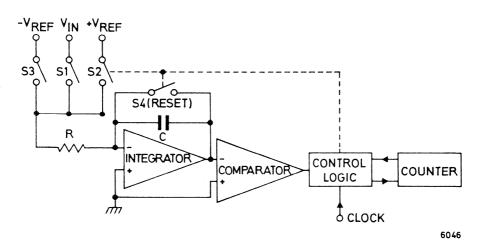

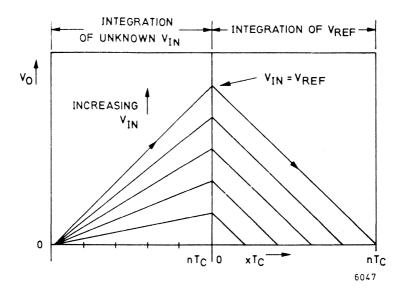

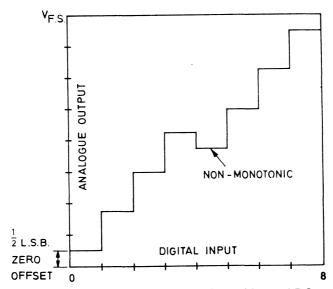

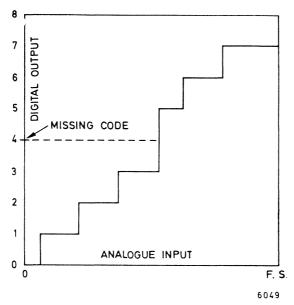

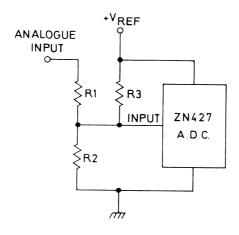

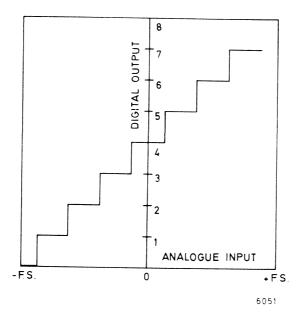

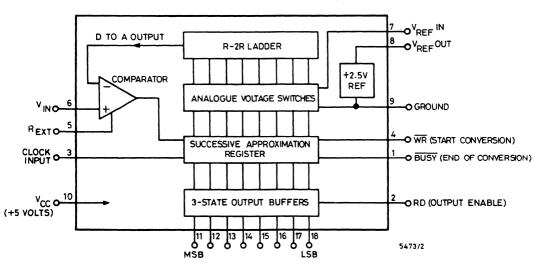

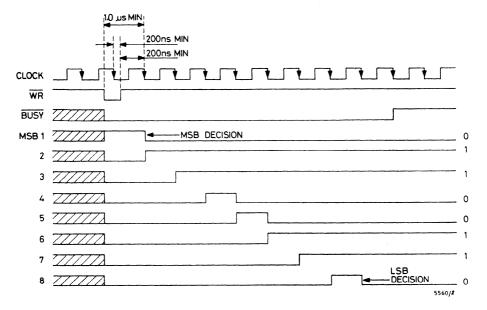

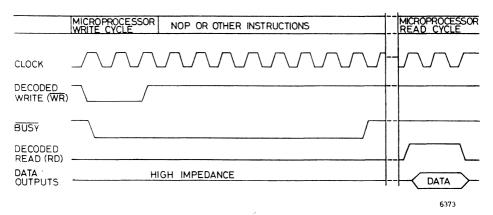

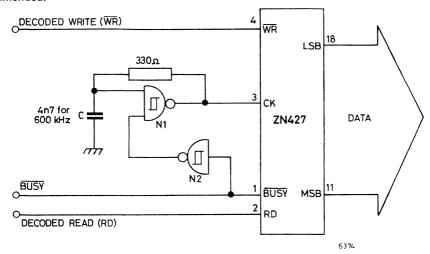

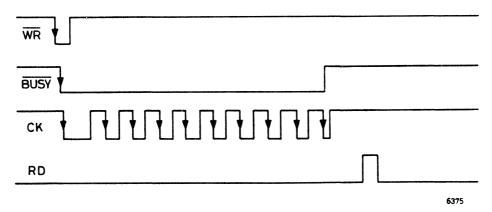

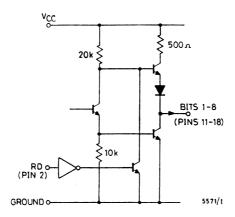

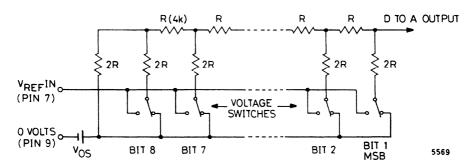

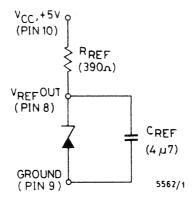

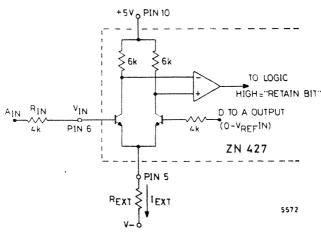

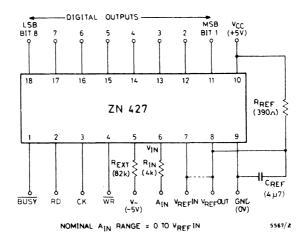

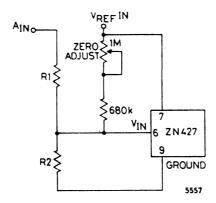

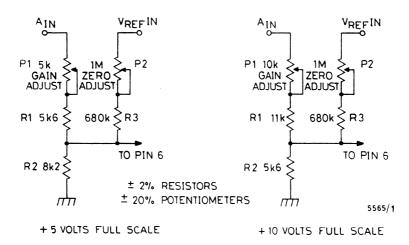

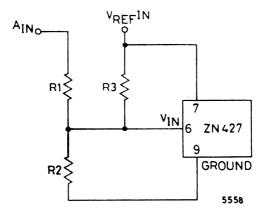

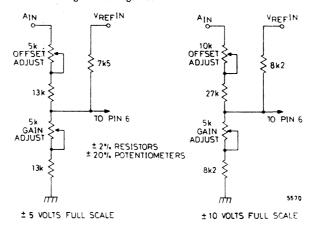

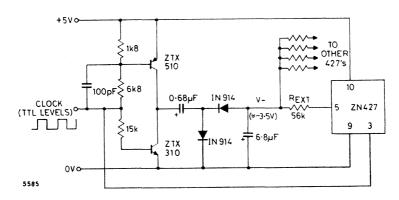

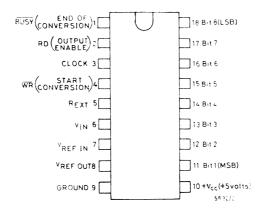

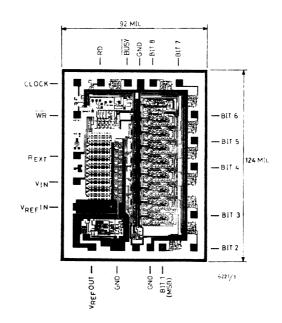

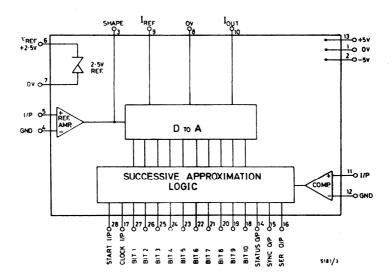

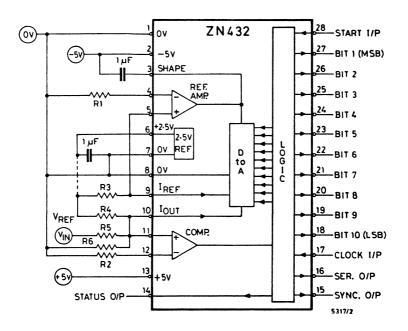

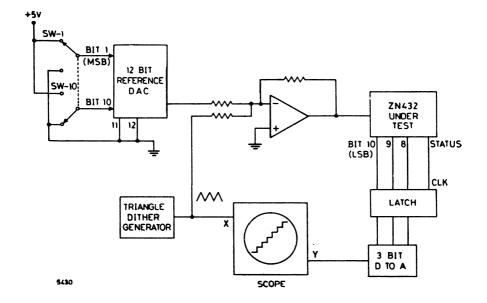

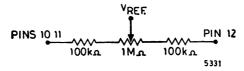

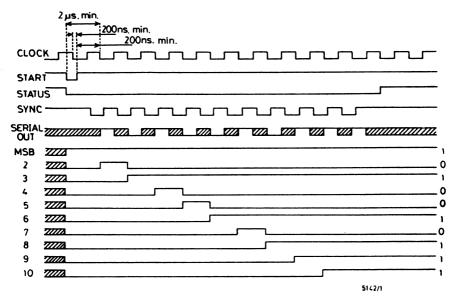

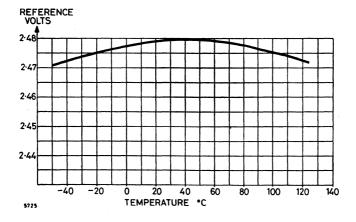

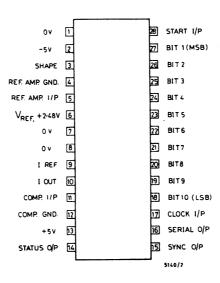

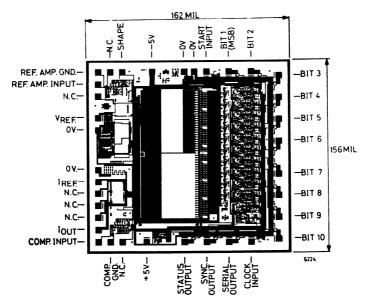

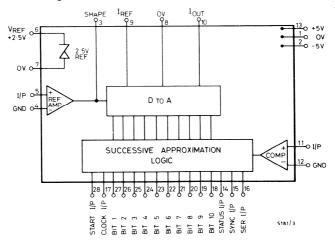

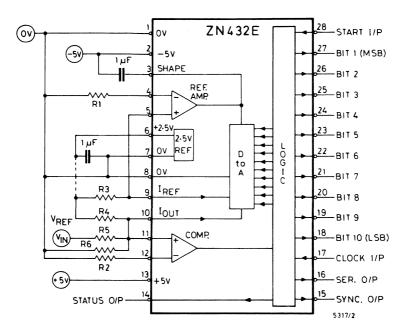

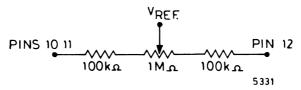

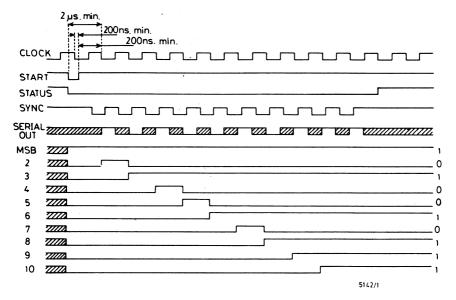

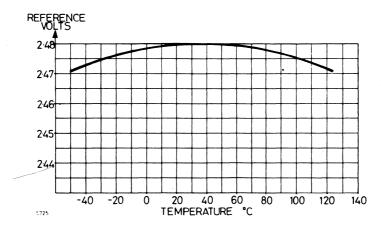

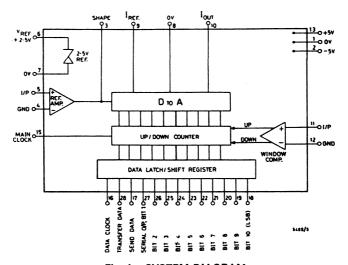

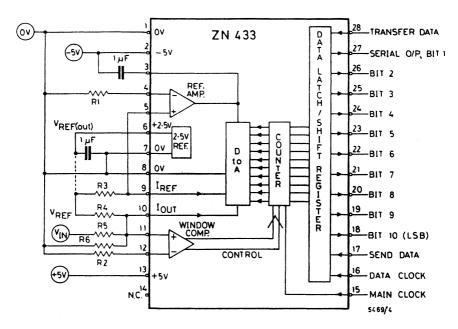

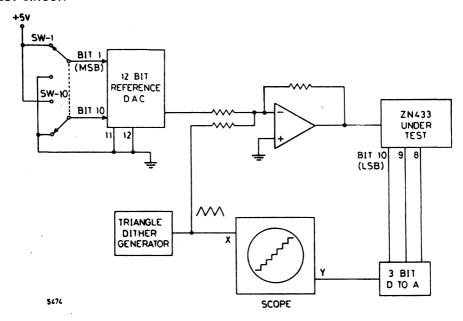

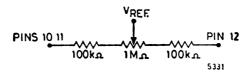

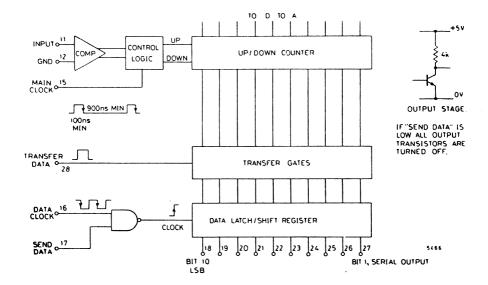

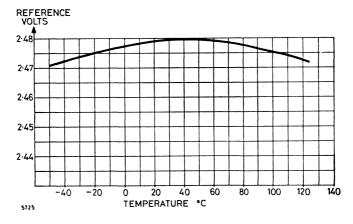

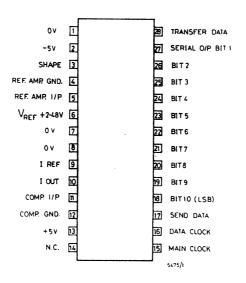

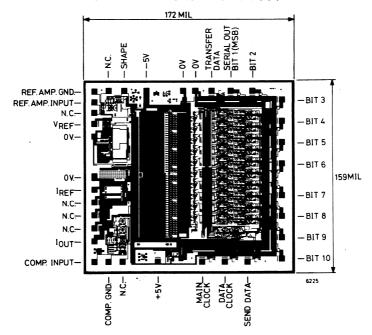

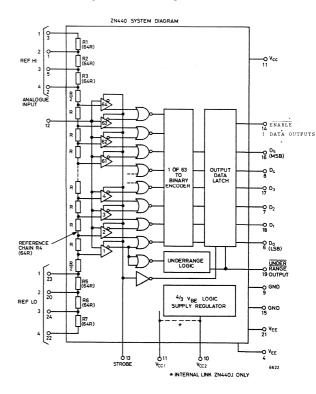

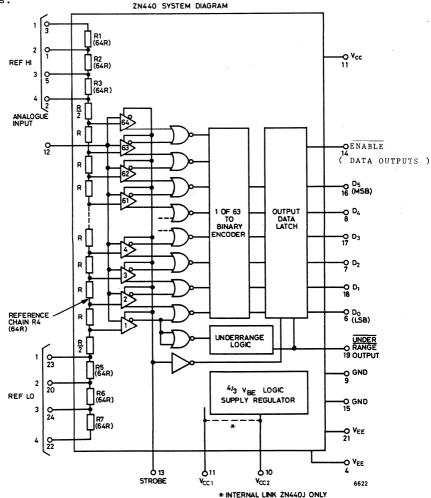

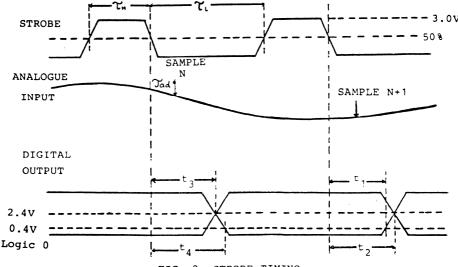

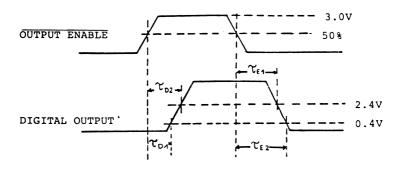

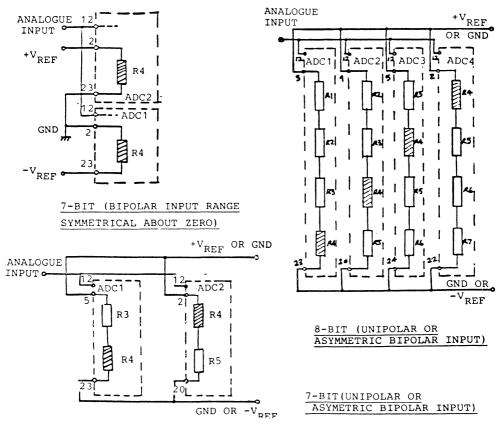

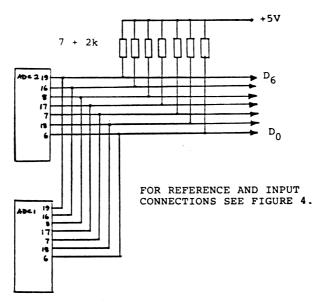

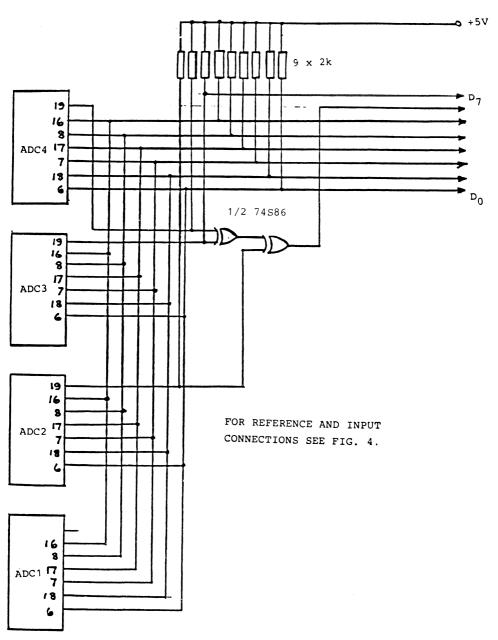

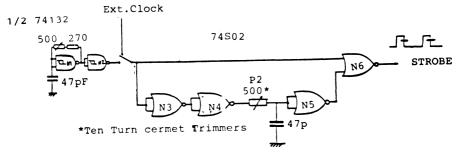

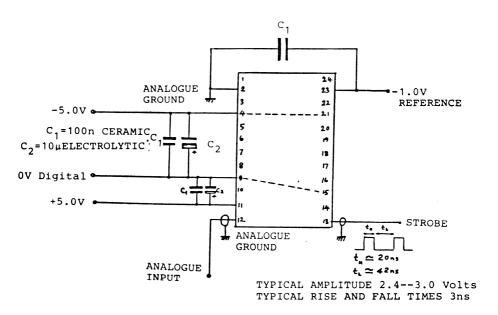

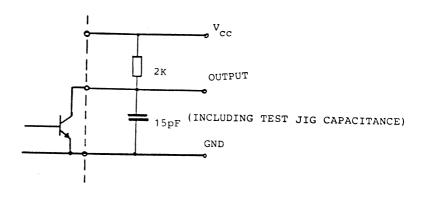

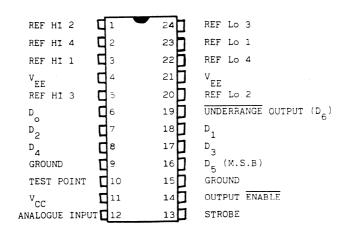

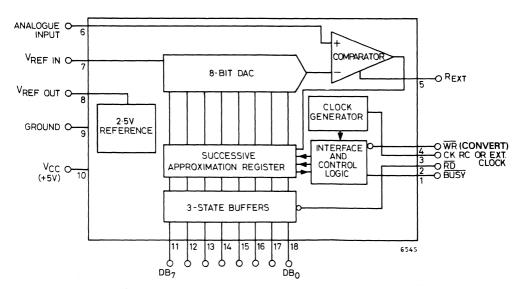

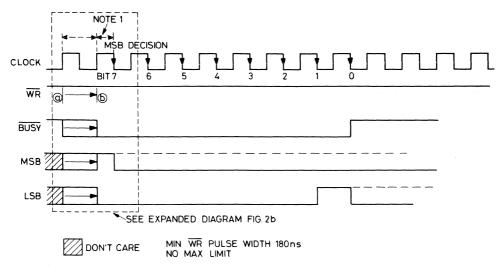

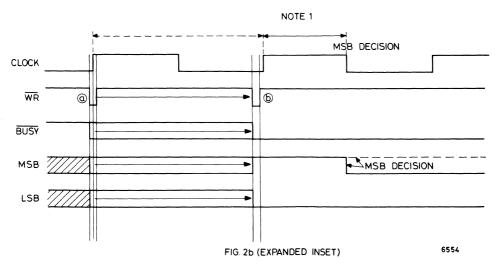

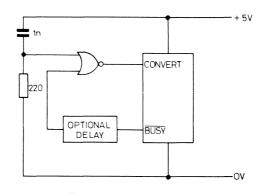

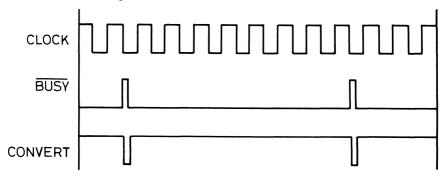

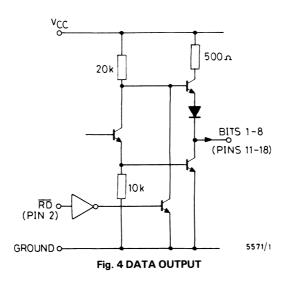

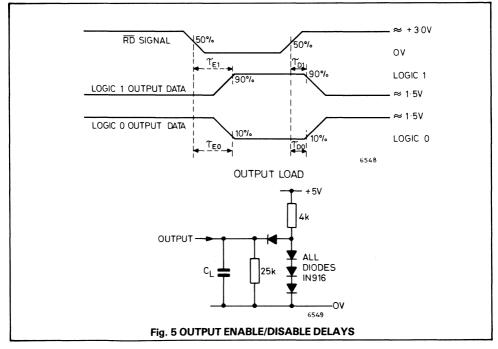

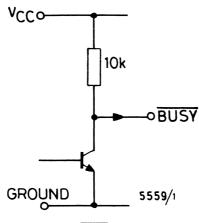

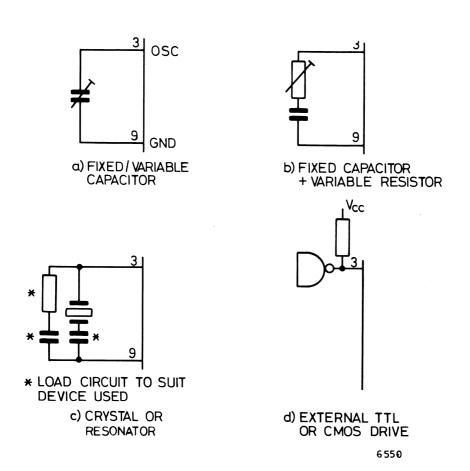

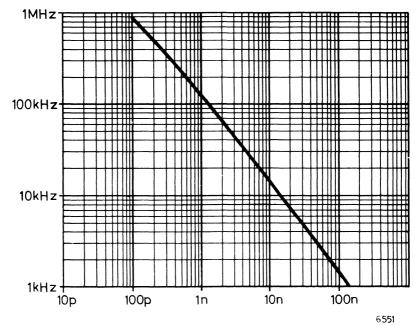

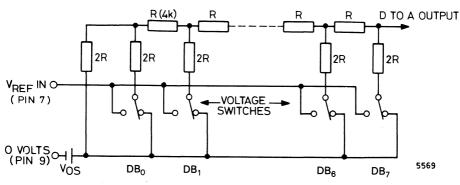

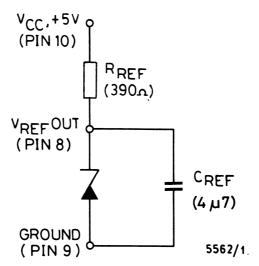

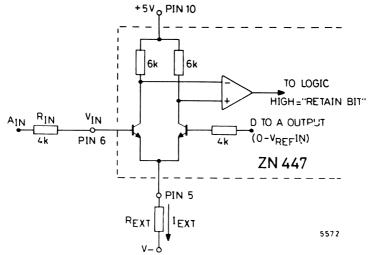

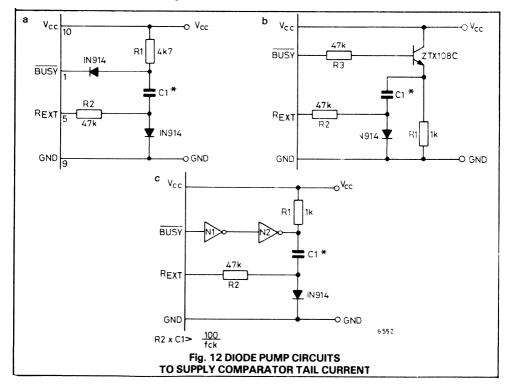

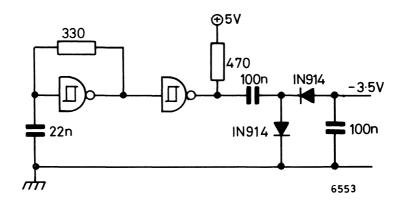

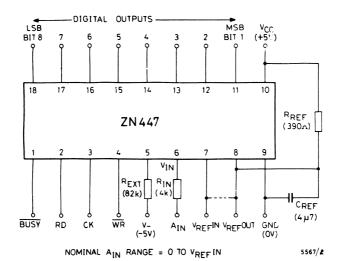

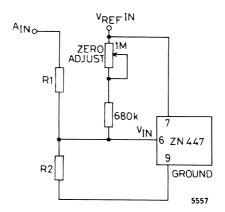

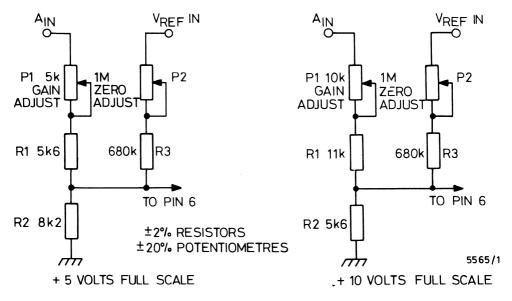

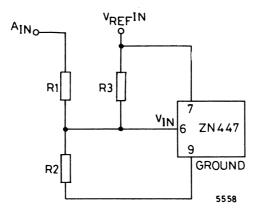

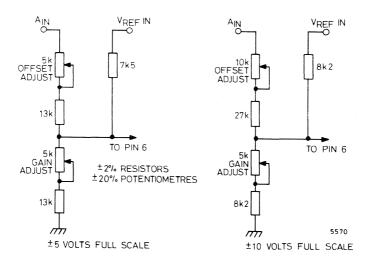

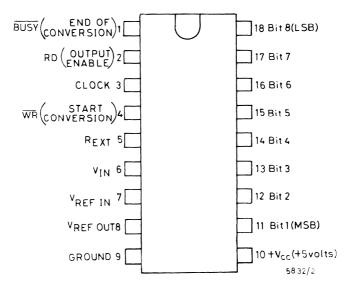

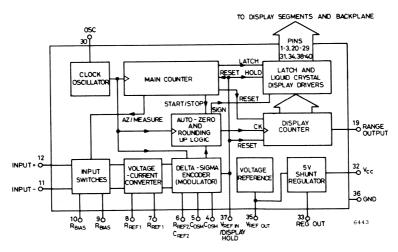

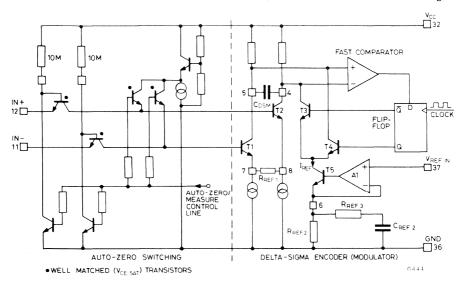

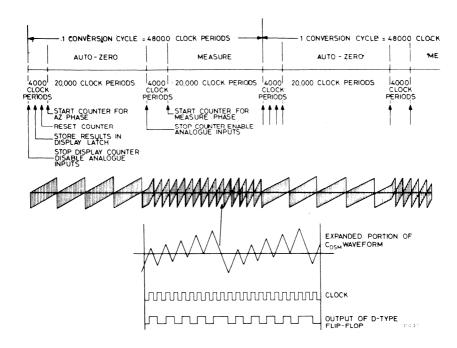

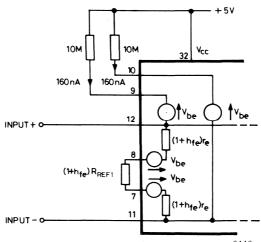

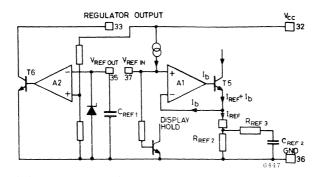

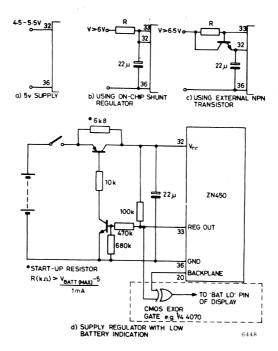

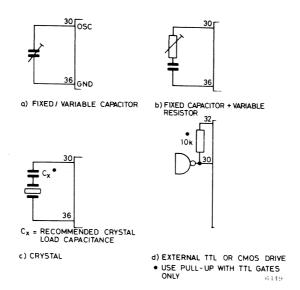

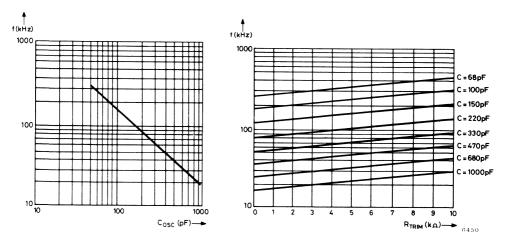

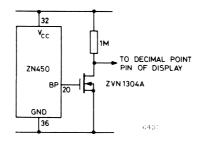

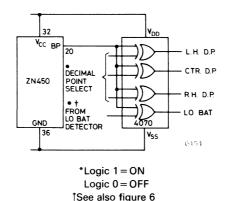

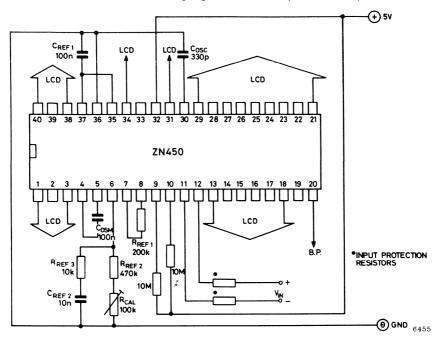

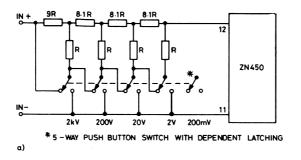

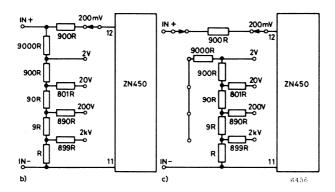

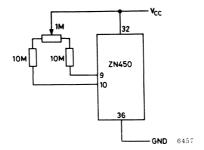

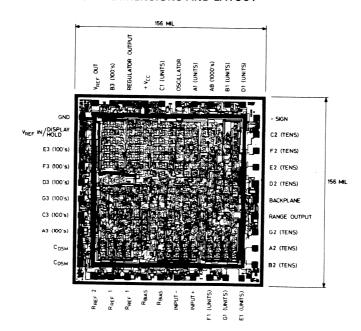

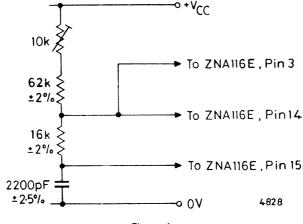

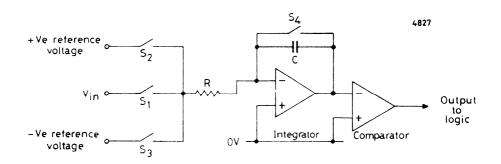

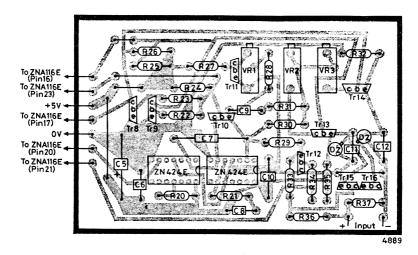

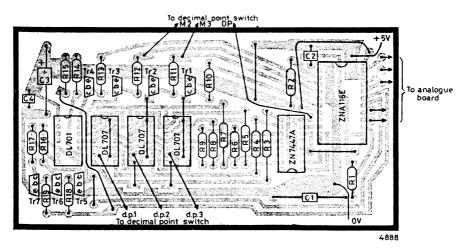

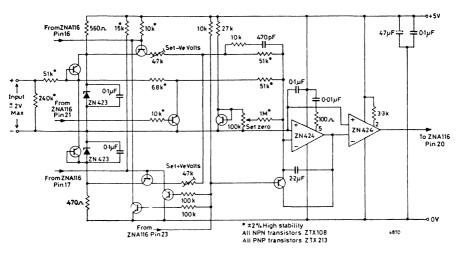

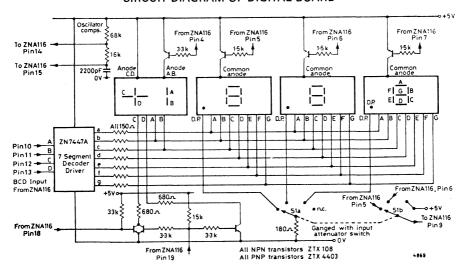

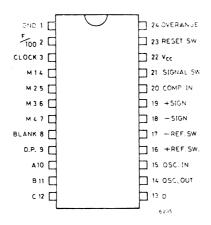

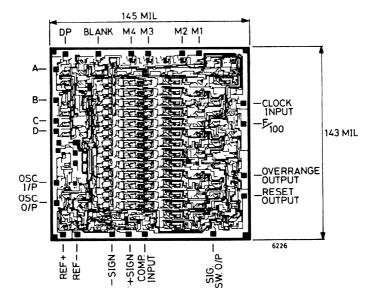

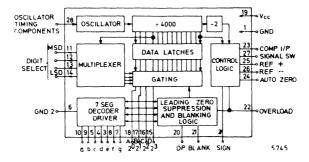

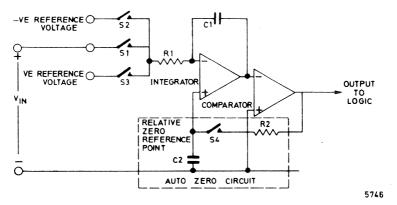

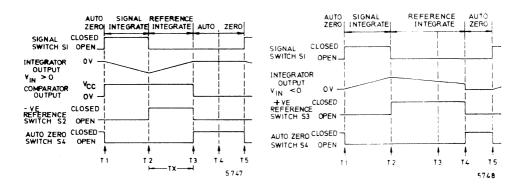

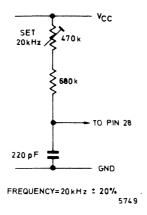

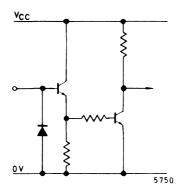

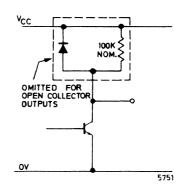

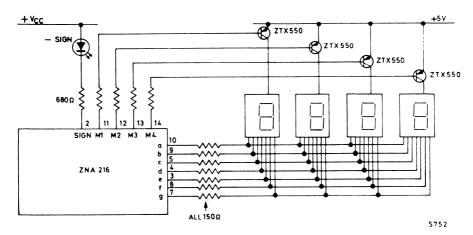

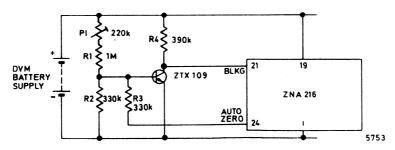

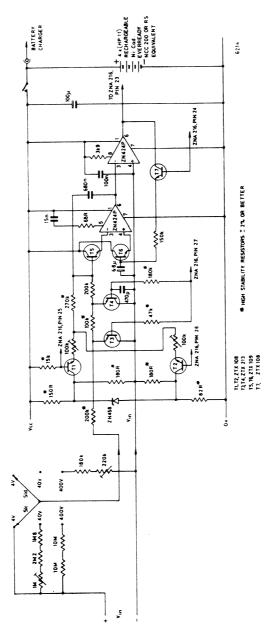

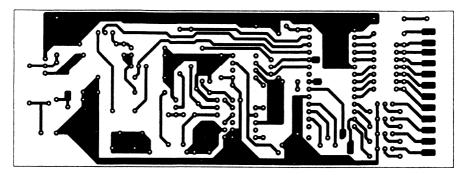

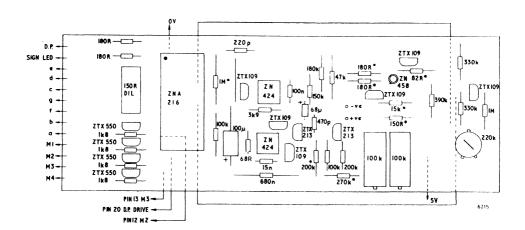

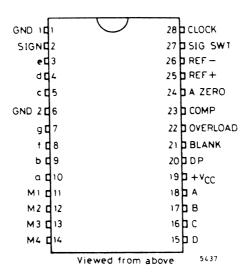

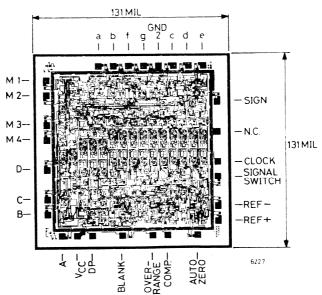

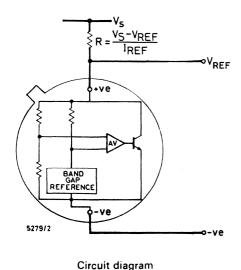

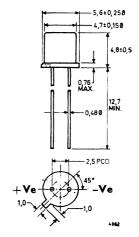

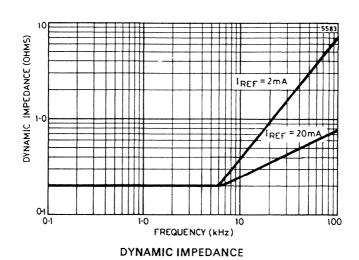

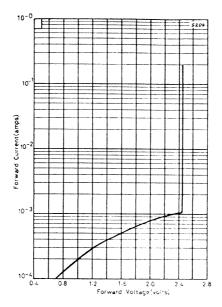

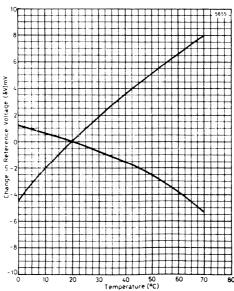

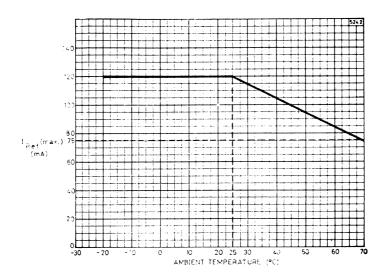

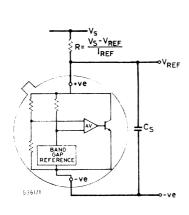

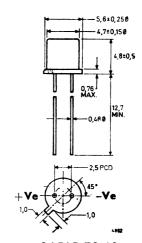

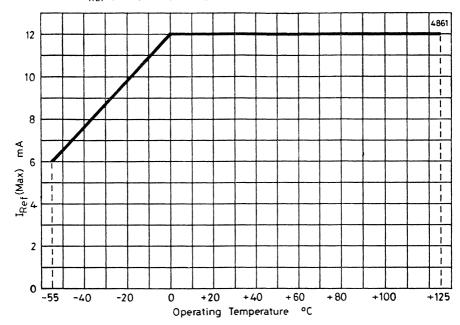

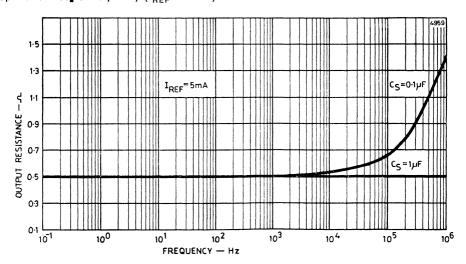

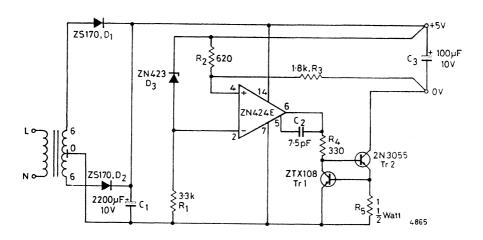

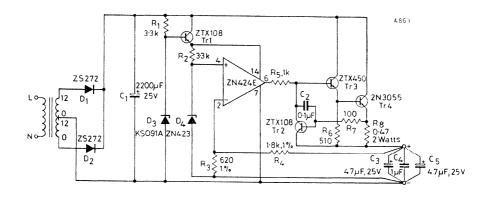

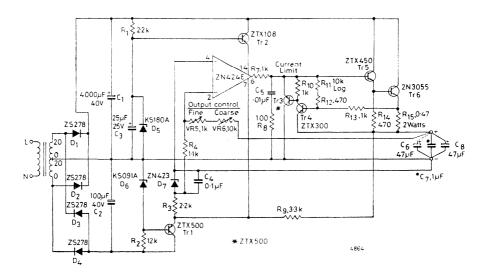

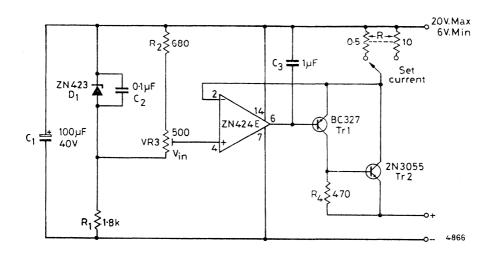

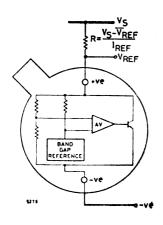

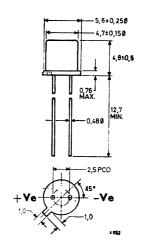

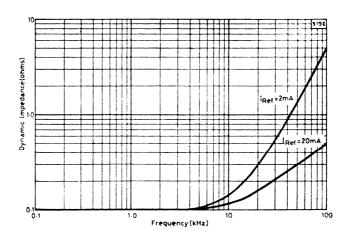

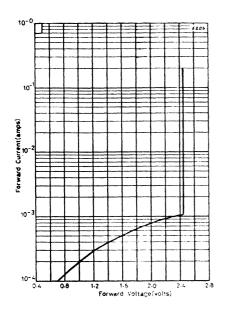

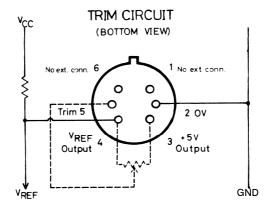

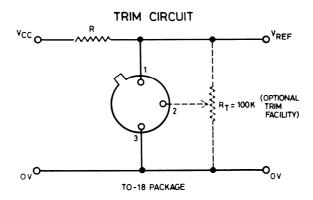

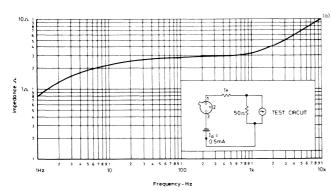

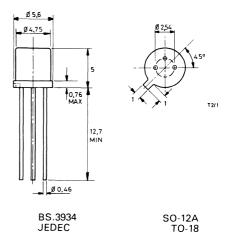

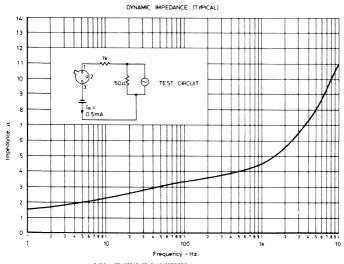

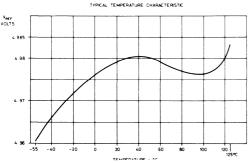

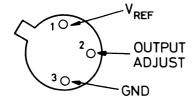

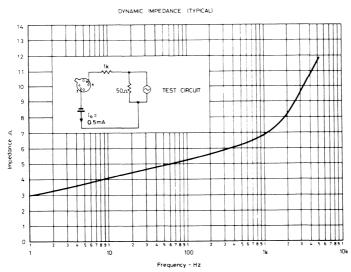

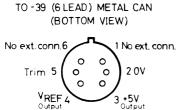

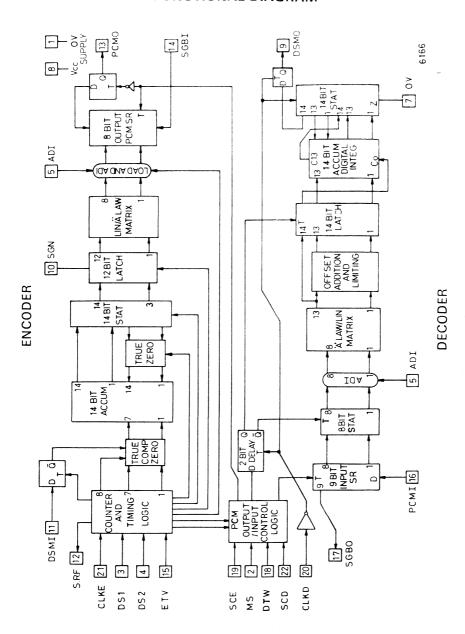

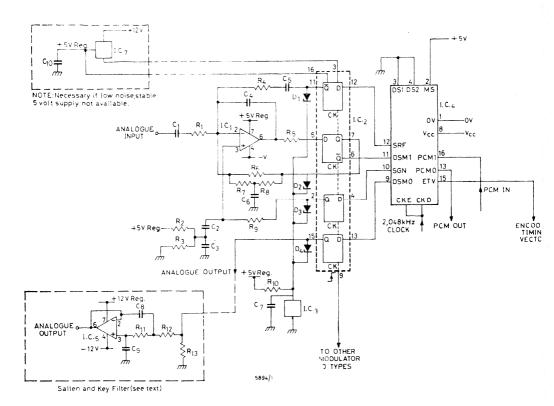

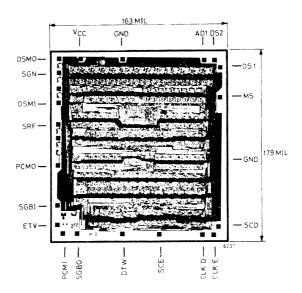

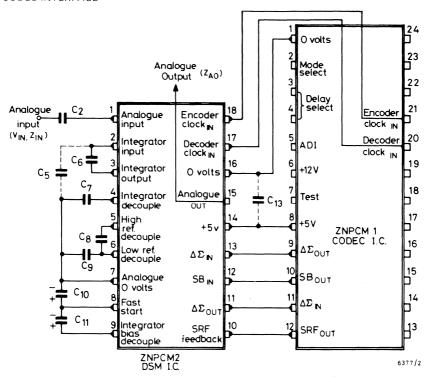

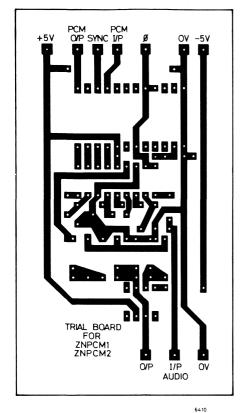

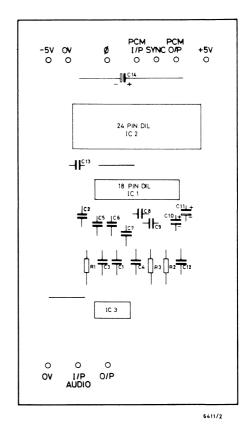

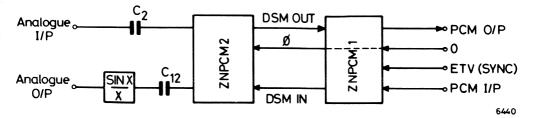

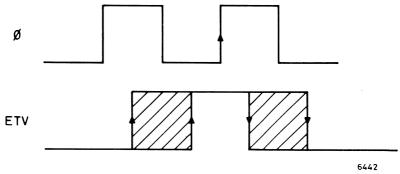

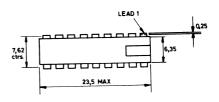

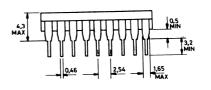

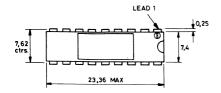

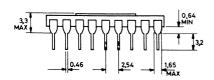

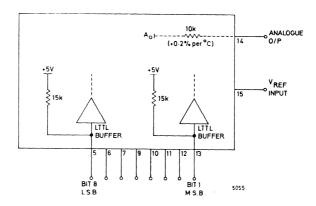

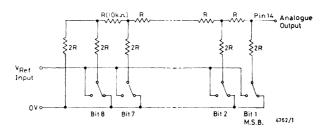

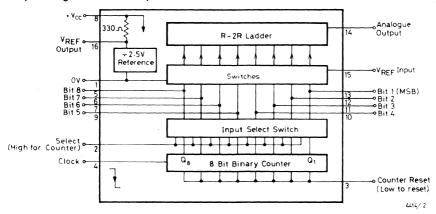

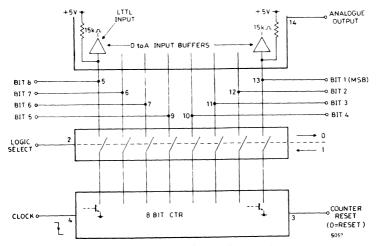

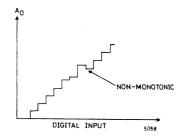

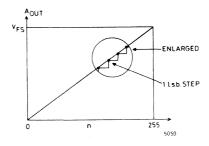

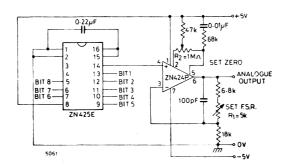

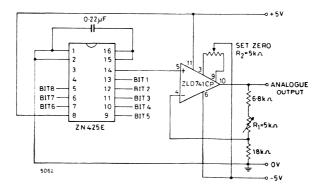

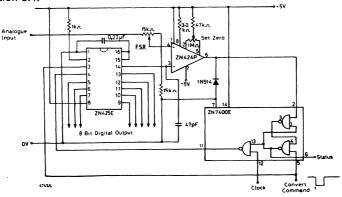

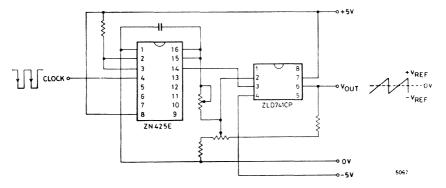

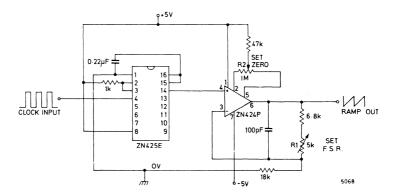

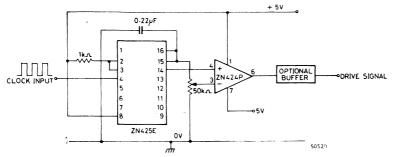

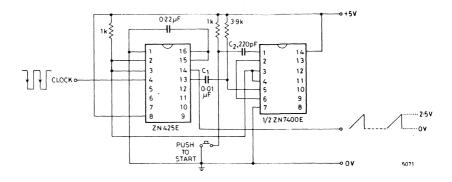

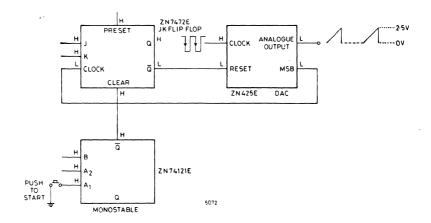

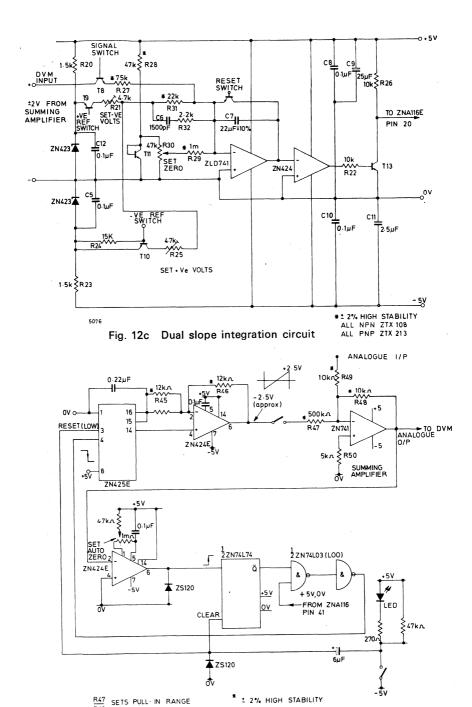

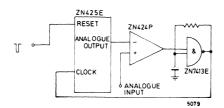

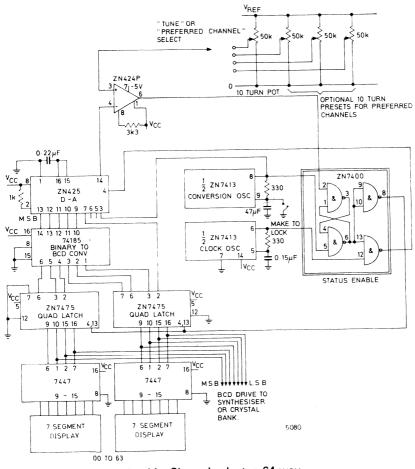

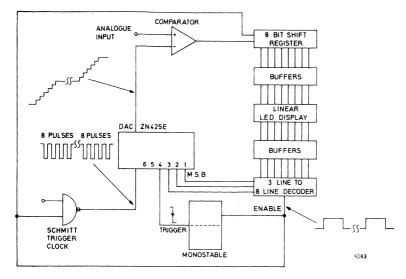

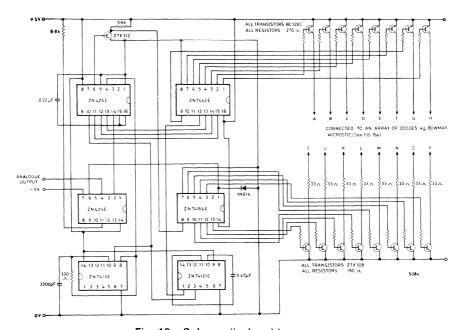

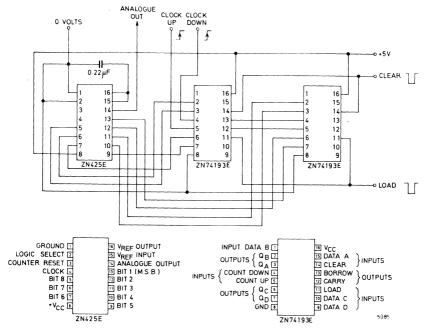

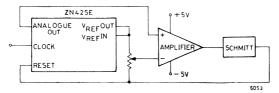

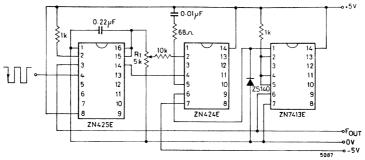

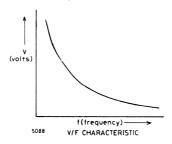

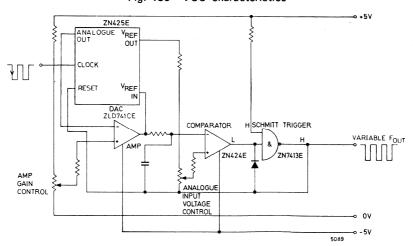

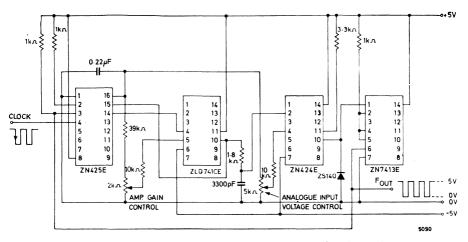

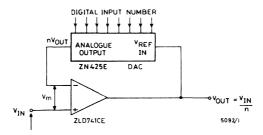

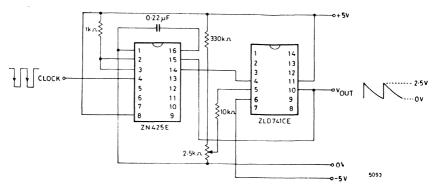

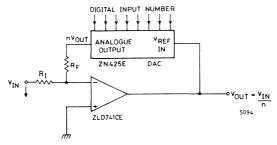

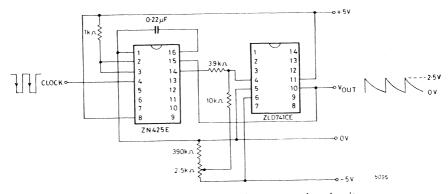

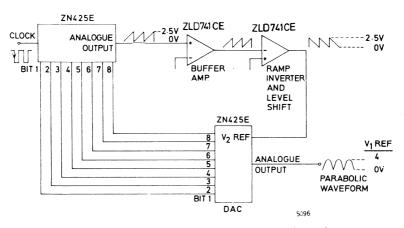

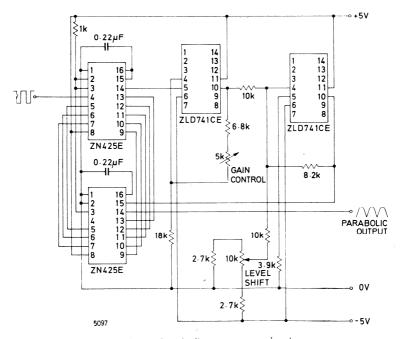

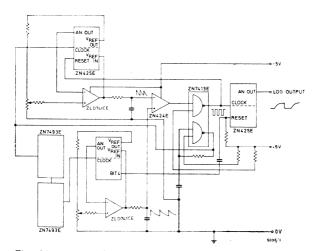

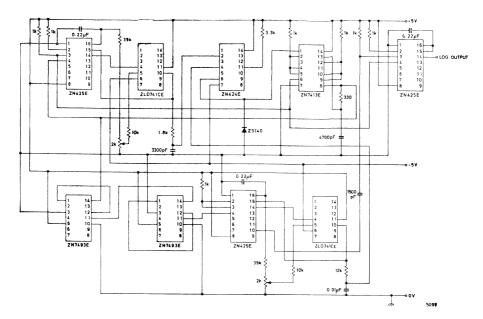

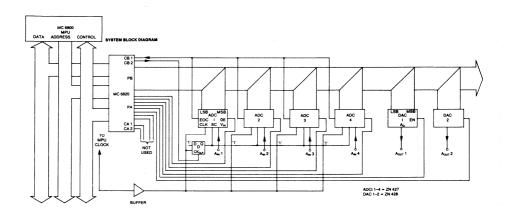

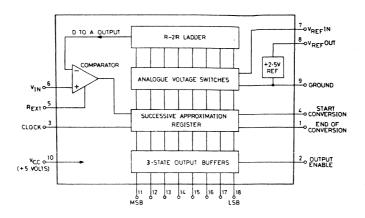

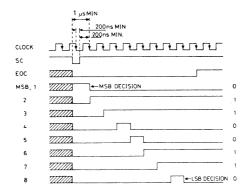

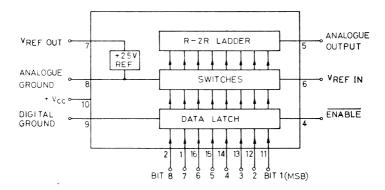

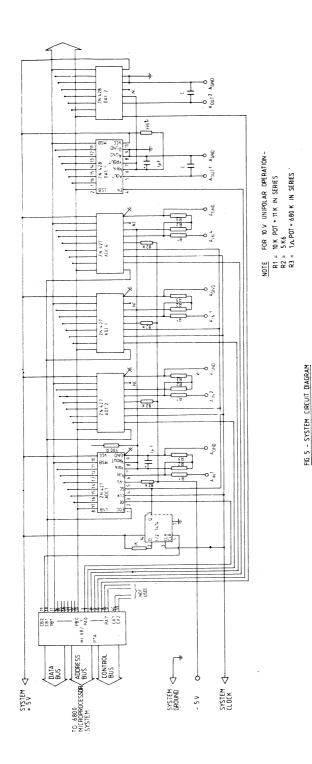

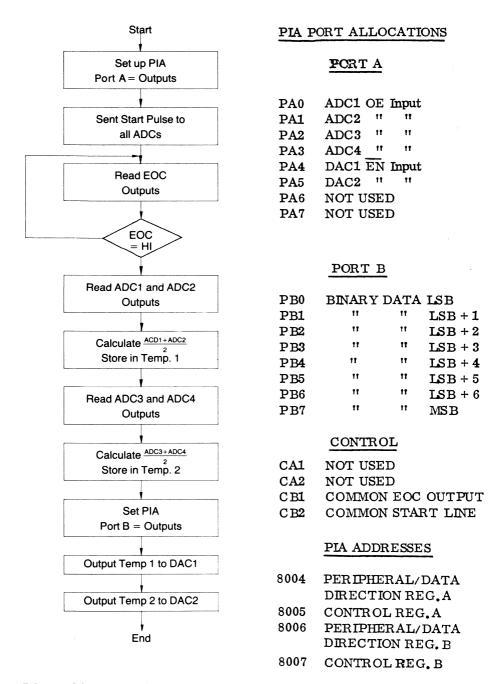

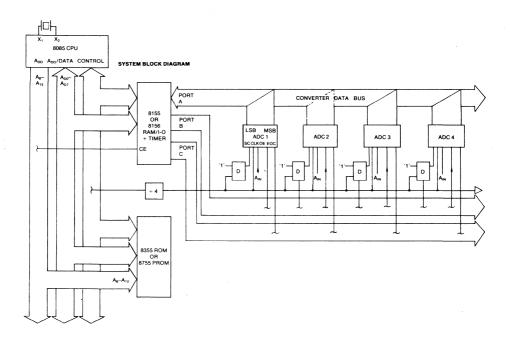

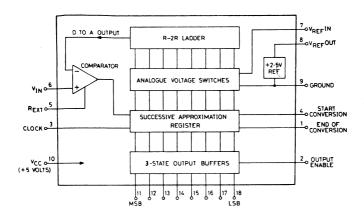

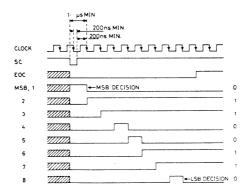

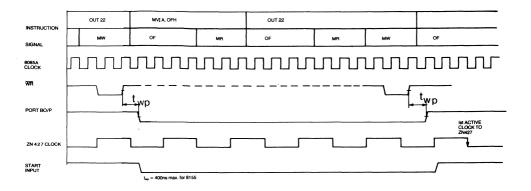

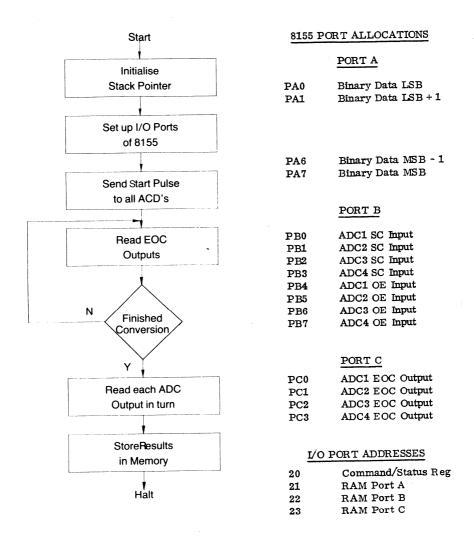

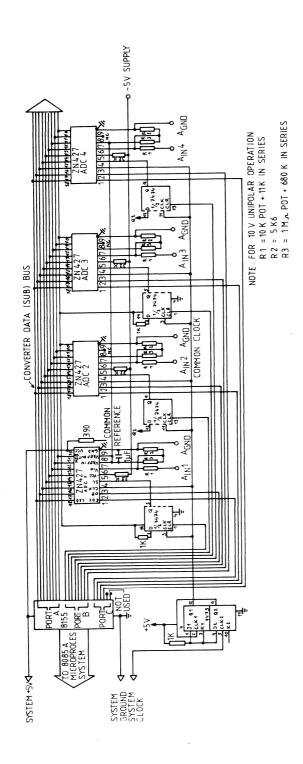

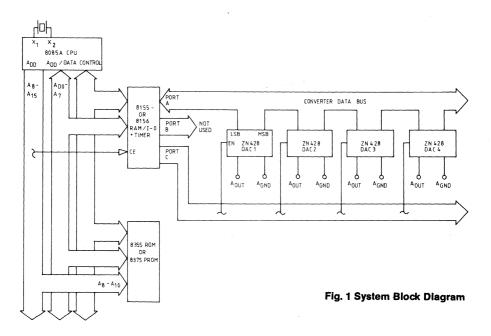

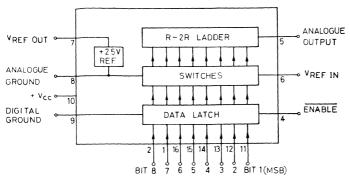

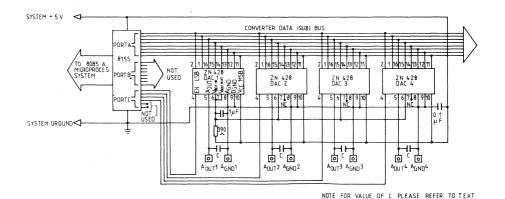

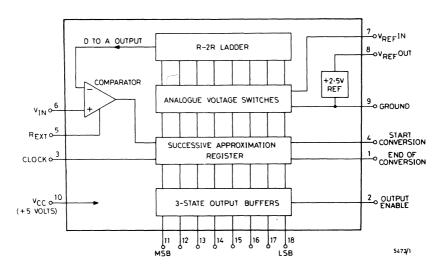

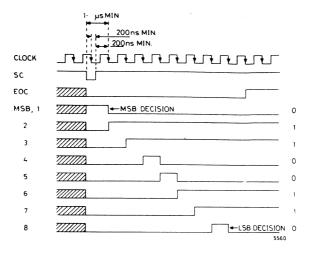

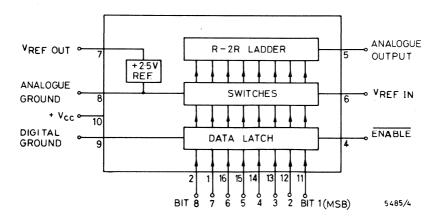

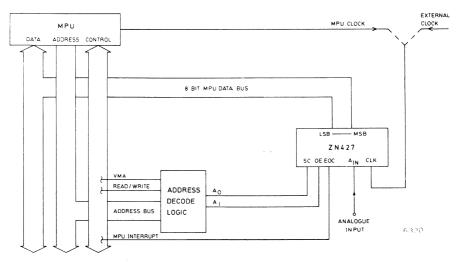

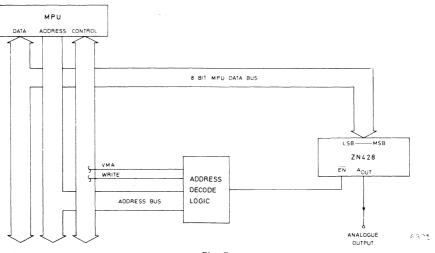

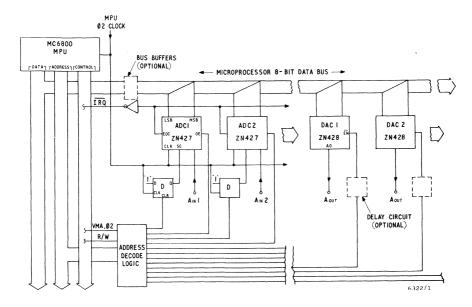

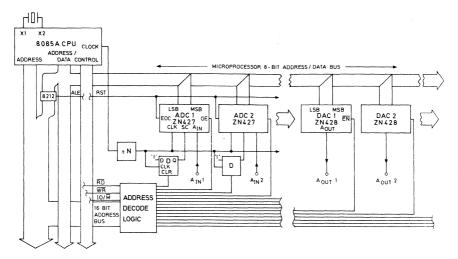

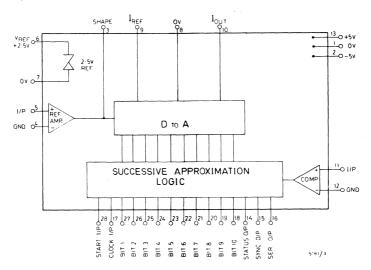

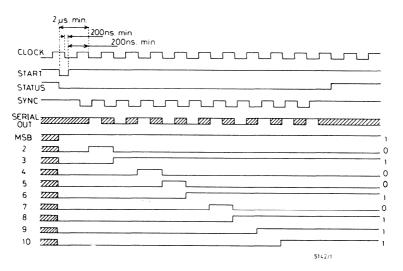

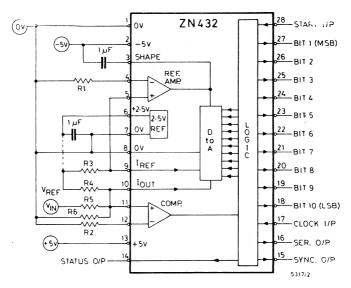

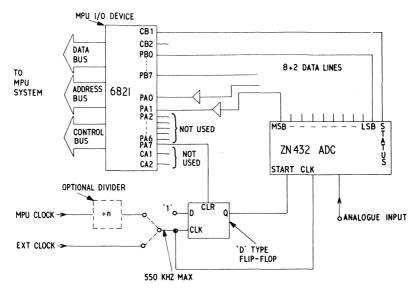

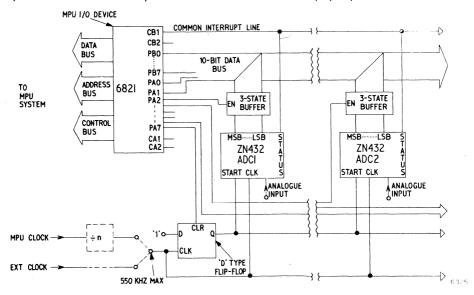

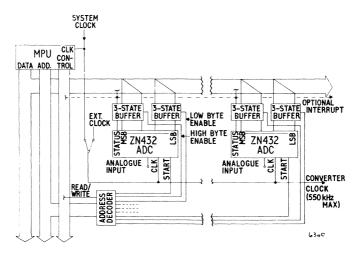

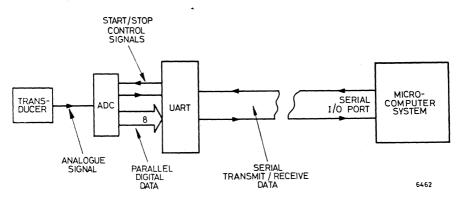

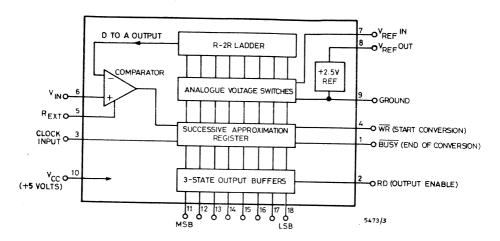

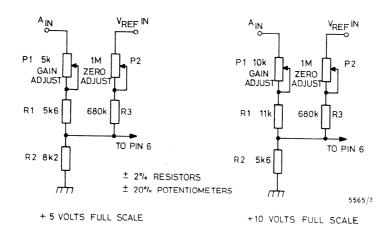

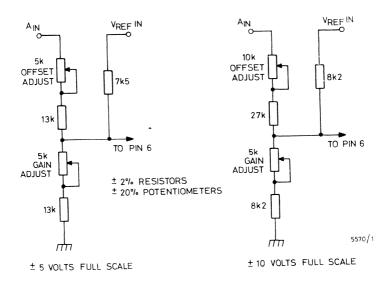

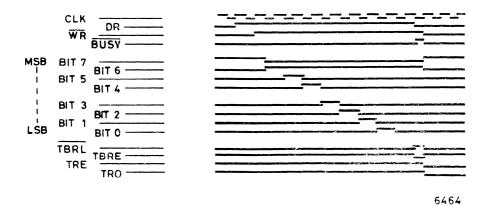

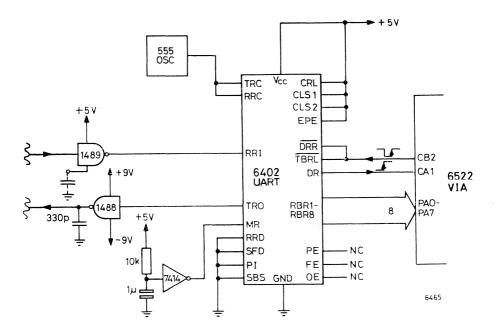

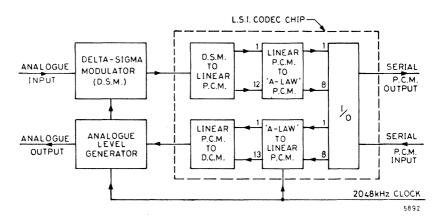

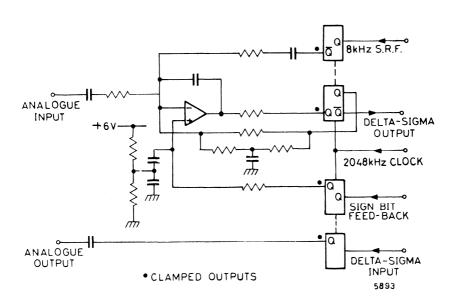

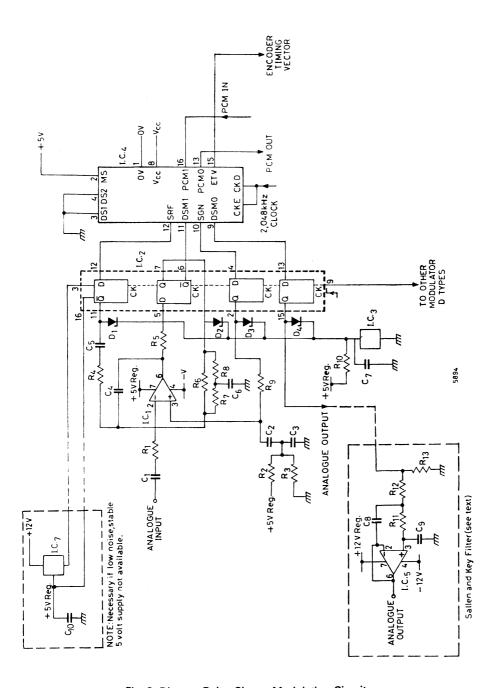

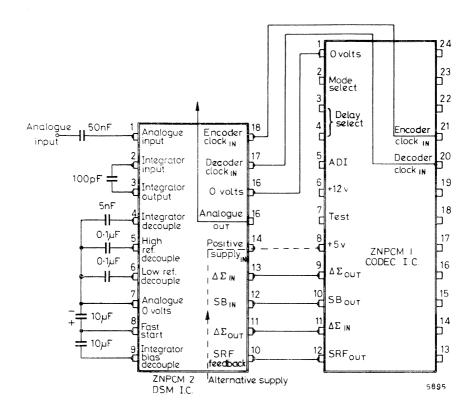

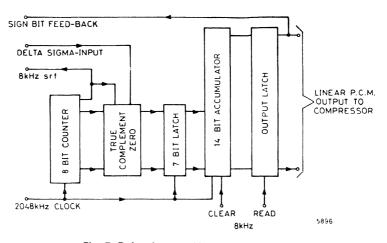

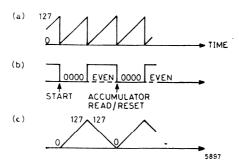

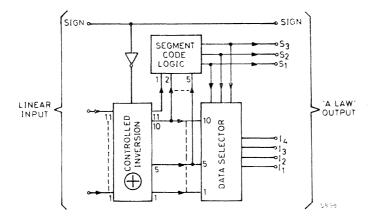

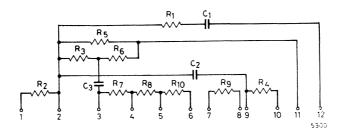

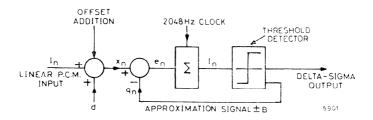

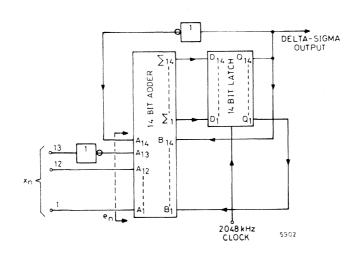

The Music Machine incorporates two Ferranti devices for digital-to-analogue (DAC) and analogue-to-digital (A to D) conversion. The part numbers are ZN429E8 and ZN449 respectively. The circuit also includes a Motorola 6850 ACIA (Asynchronous Communications Interface Adapter) for handling the MIDI channel, two anti-alias filters (one for input and one for output), a discrete microphone amplifier and a headphone amplifier. The clock signal for the ACIA and the ZN449 is provided by a ceramic oscillator.

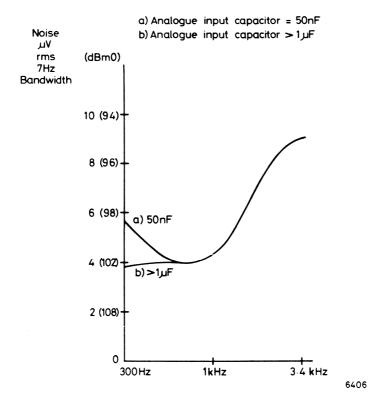

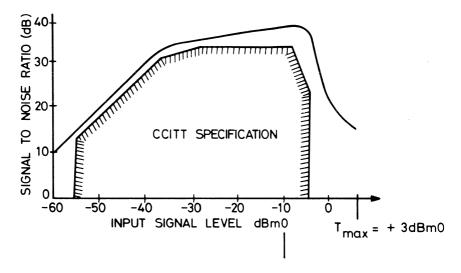

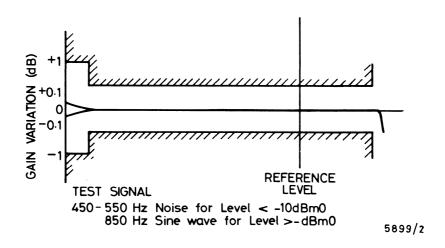

The incoming signal from the microphone amplifier is sampled to an 8-bit resolution at a rate of 19.444 thousand samples per second. This yields an analogue bandwidth of approximately 9.5 KHz which is in fact the cutoff frequency of the filters.

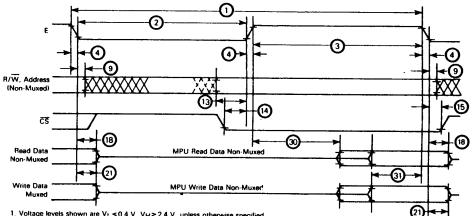

All of the devices on The Music Machine data bus are accessible to the Amstrad within its IO space. ACIA transactions must use 16-bit IO instructions; the converters are accessible via 8-bit IO instructions.

IO Map

ADC START OF8F8 hex

Reading (or writing) to this port will start analogue to-digital conversion.

ADC READ OF8F4 hex (read only)

The contents of the A-to-D can be read via this port. Note that the A-to-D must have been 'started' at least 20 uS before this port is read.

**DAC WRITE** OF8FO hex (write only) Date can be written to the DAC via this port.

OF8E8 hex (write only) Writing 01 to this port INTER'PT SEL disables internal Amstrad interrupts and replaces the IRQ signal from the ACIA. Writing 0 restores normality.

Sheet

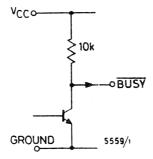

**ACIA** status OF8EE hex (read only)

See ACIA data read OF8EF hex (read only) Motorola Data

OF8ED hex (write only)

OF8EC hex (write only)

ACIA control

ACIA data write

Sampled-data capacity 1223ms

Clock frequency 500 kHz

A-to-D conversion time 20 uS

Sampling frequency 19,444 samples per second

Sampling bandwidth 20 Hz to 9.5 KHz

Input sensitivity 2mV RMS into 50 kOhms

Headphone output 15mW RMS into 15 Ohms

Amplifier (phono) output 450 mV RMS

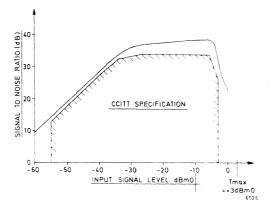

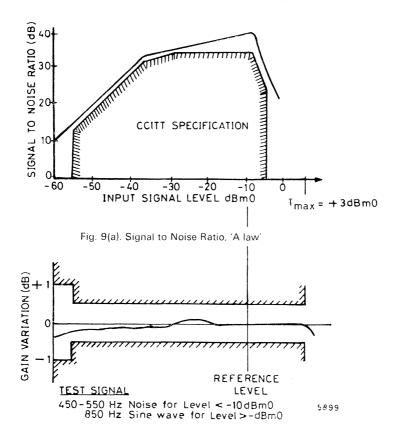

Signal-to-noise ratio 42 dB

### **MIDI**

The only MIDI facilities provided as standard with The Music Machine are the ability to control internal or external note-on or note-off events. In most cases the action of turning a note on or off requires the transmission of three bytes.

Note-on event:

1001nnnn NOTE-ON control byte. nnnn is a four-bit

number corresponding to the MIDI channel number. 0000 is Channel 1, 0001 is Channel 2, and 1111 is Channel 16, for

example.

Oppppppp Pitch value. 0010 0000 is middle C.

Ovvvvvvv Velocity value. The Music Machine can

only recognise velocity 0 which is, in effect, NOTE OFF or another value for note on. There are no facilities for volume control and so, quite reasonably, it is ignored.

Note-off event:

1000nnnn NOTE-OFF control byte

Oppppppp Pitch value of the note to be turned off.

Ovvvvvv After-touch velocity, ignored.

### Drum Pitch

In common with other drum machines, each drum has a notenumber; unfortunately, different machines use different numbers. The Music Machine uses the following note numbers:

Middle C = 1, C# = 2, D = 3, and so on.

### 5.2 Music capacity

RAM is consumed at the rate of one byte per sample. With a sample rate of 19.444 kHz and about 23K of data space, approximately 1.22 seconds of continuous digitised data can be stored. The amount of free RAM is indicated on most screens, and is given in units of milliseconds.

Up to eight digitised samples can be stored in RAM simultaneously. At full capacity, the average duration of each sample is about 0.15 seconds. In practice, the digitised drum sounds consume around one tenth of a second each, leaving half a second or so for user-sounds. You do of course have the option of deleting the resident samples in order to make use of the full data space. The total duration available of around 1.2 seconds is, we believe you will find, a surprisingly long time for most musical sounds.

A song or rhythm can comprise a sequence of up to 255 different bars. Because most music repeats a range of bars, the final song or drum sequence can last very many minutes.

### 5.3 Additional notes

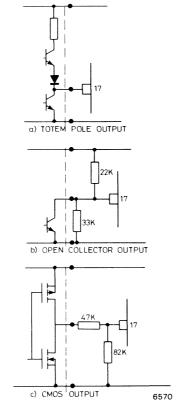

You must use headphones whose lead is terminated with a 3.5 mm stereo jack plug as a mono plug may short the output and you will hear nothing. Aim to use headphones with an impedance between 8 and 64 Ohms.

By all means experiment with microphones other than the one we supply; in general, the better the quality of the microphone, the better the results.

CPC 464, CPC 664, and CPC 6128 are trademarks of Amstrad Consumer Electronics plc.

Music Machine transforms the Amstrad into a powerful music computer.

features you'd normally buy separately. Sampling, editing, step sequencing, composition, MIDI, digital echo effect and much more. Or as

digital echo effect and much more. Or as Amstrad Action put it, "virtually everything you require for music composition." Sound sampling, the latest buzzword, lets you record natural sounds with the microphone

supplied, then edit them and play them back at different pitches.

Or you can choose from eight internal 'voices' including drums and synthesiser, edit them, create new ones and play them from the

Available at WHSMI

### An Amstrad like you've never heard it before.

Amstrad or a MIDI keyboard. The sampled drum sounds "have to be heard to be believed" (Amstrad Action) and come with a Rhythm Editor.

For budding composers there's note, bar and tune editing. And for enthusiasts, a full MIDI specification that includes In/Out/Thru ports

to connect with MIDI instruments.

Yet despite its power, the menu driven

graphics and excellent manual allow sounds to

be created and songs composed in minutes.

The price of all this magic? Just £49.95\*

complete with manual, microphone and demon-

stration recording

As Amstrad User's reviewer summed it up, "a worthwhile hunk of technology for the price of four or five good games...Fun fun fun!"

or pop into your nearest store and see it for yourself!

Ram Electronics (Fleet) Ltd, Unit 16, Redfields Industrial Park, Redfield Lane, Church Crookham, Aldershot, Hants GU15 ORE. Telephone: (0252) 850085.

When used with a CPC464 and disk drive, an adaptor is required. Music Machine is a trademark of Bam Electronics (Fleet) Ltd.

| ore | ler   |      | har | ge 1 | ny i | Acce | ss/ | /isa |   |   |                     | • | 1 |

|-----|-------|------|-----|------|------|------|-----|------|---|---|---------------------|---|---|

|     | Г     |      |     |      |      |      | Ι   | I    | I | Ι |                     |   |   |

| _   | DRE   | SS   |     |      |      |      |     |      | _ |   |                     |   |   |

|     |       |      |     |      |      |      | POS | rcon | E |   |                     |   |   |

| TE  | LEPS  | HONE | ò   |      |      |      |     |      |   |   |                     |   |   |

|     | sie A |      |     |      |      |      |     |      |   |   | 7 days              |   |   |

|     |       |      |     |      |      |      |     |      |   |   | ields In<br>shire ( |   |   |

|     |       |      |     |      |      |      |     |      |   |   |                     |   |   |

John Menzies and all good computer stores.

### MUSIC MACHINE

The complete home computer mutic system

AMSTRAD

USER GUIDE

MUSICE SYSTEM MACHINE COMPUTER MUSIC SYSTEM

AMSTRAD USER GUIDE

# MUSIC MACHINE

THE COMPLETE HOME COMPUTER MUSIC SYSTEM

AMSTRAD

USER GUIDE

MUSIC MACHINE

SOFTWARE

FOR THE AMSTRAD 6128

AMSTRAD 6128

## MUSIC MACHINE

The complete home computer music system

FULL ARTEE

- Easy to use with fast menu-driven screens

- High quality drum machine with real prerecorded drum sounds

- Any external sound can be recorded, altered and played through the keyboard

- Write your own music quickly and easily using the onscreen facilities

- MIDI interface to other musical instruments

- Pack includes easy-to-understand user guide, microphone and demonstration tape

- Plug in your headphones or listen through your hi-fi

Music Machine is a trademark of Ram Electronics (Fleet) Ltd. Designed in the UK by Flare Technology Ltd. and manufactured in the UK by Ram Electronics (Fleet) Ltd. We reserve the right to amend specifications without notice. © Ram Electronics (Fleet) Ltd. 1986. © Flare Technology 1986.

Ram Electronics (Fleet) Ltd., Unit 16, Redfields Ind. Park, Redfield Lane, Church Crookham, Aldershot, Hants. GU13 ORE.

waisks pienm laindmop amon alaidmop and

LECTEU

NUMER

Play Midi echo Load/save

tuNe editor Bar editor Drums

sample editor piano exit

delete drum editor sampler

1 combell samples Hh close

2 Tom 2 Share

3 ToM1 7 BASS

4 HH open 8 SYNTH

free Tune Snap the hoogie

AMSTRAD VERSION

### MUSIC MACHINE

The complete home computer music system

LECTEUR DE DISQUETT

HUMÉROS DES TOUCHES

PALETTE DES COL

to Manager 12" In Proceeding 12" I Proceeding 12" In Additional In 18"

SIDE A

ISSUE 1

© RAM

ELECTRONICS

464: Hold down CTRL key and the small enter key. 664/6128: Type I (shifted@) tape (ENTER) then type RUN"

# AUDIO DEMO "SNAP THE BOOGIE"

SIDE B

© FLARE

© RAM ELECTRONICS

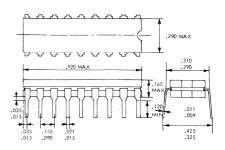

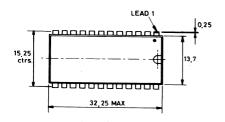

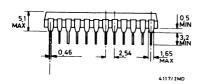

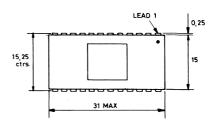

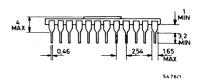

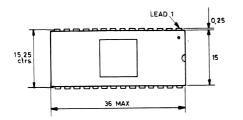

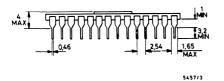

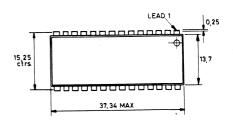

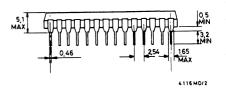

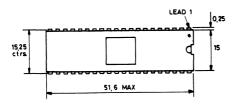

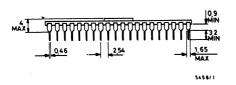

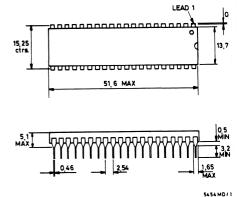

### MC6850 (1.0 MHz) MC68A50 (1.5 MHz) MC68B50

### ASYNCHRONOUS COMMUNICATIONS INTERFACE ADAPTER (ACIA)

The MC6850 Asynchronous Communications Interface Adapter provides the data formatting and control to interface serial asynchronous data communications information to bus organized systems such as the MC6800 Microprocessing Unit.

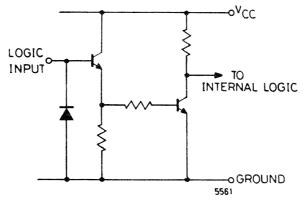

The bus interface of the MC6850 includes select, enable, read/write, interrupt and bus interface logic to allow data transfer over an 8-bit bidirectional data bus. The parallel data of the bus system is serially transmitted and received by the asynchronous data interface, with proper formatting and error checking. The functional configuration of the ACIA is programmed via the data bus during system initialization. A programmable Control Register provides variable word lengths, clock division ratios, transmit control, receive control, and interrupt control for peripheral or modern operation, three control lines are provided. These lines allow the ACIA to interface directly with the MC6860L 0-600 bps digital modern.

- 8- and 9-Bit Transmission

- Optional Even and Odd Parity

- Parity, Overrun and Framing Error Checking

- Programmable Control Register

- Optional + 1, + 16, and + 64 Clock Modes

- Up to 1.0 Mbps Transmission

- False Start Bit Deletion

- Peripheral/Modem Control Functions

- Double Buffered

- One- or Two-Stop Bit Operation

### MOS

(N-CHANNEL, SILICON-GATE)

ASYNCHRONOUS

COMMUNICATIONS INTERFACE

ADAPTER

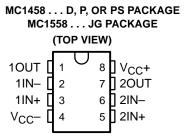

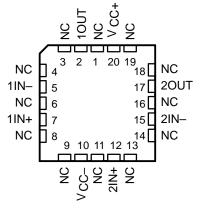

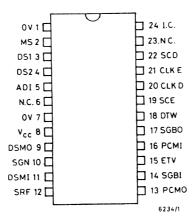

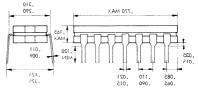

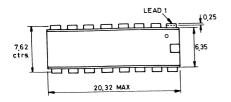

### PIN ASSIGNMENT Vss**⊈**ı ● 24 D CTS Rx Data [ 23 D DCD Rx CLK 13 22 00 Tx CLK 21 01 RTS 20 D D2 Tx Date 6 19 7 03 IRO d 7 18 J D4 csode 17 1 05 CS2 d 9 16 1 06 CS1 10 15 07 RS DI 14 J E VCC 12 13 R/W

### **MAXIMUM RATINGS**

| Characteristics                                                                        | Symbol          | Value                                                     | Unit |  |

|----------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------|------|--|

| Supply Voltage                                                                         | Vcc             | -0.3 to +7.0                                              | V    |  |

| Input Voltage                                                                          | V <sub>in</sub> | -0.3 to $+7.0$                                            | V    |  |

| Operating Temperature Range<br>MC6850, MC68A50, MC68B50<br>MC6850C, MC68A50C, MC68B50C | <sup>†</sup> A  | T <sub>L</sub> to T <sub>H</sub><br>0 to 70<br>-40 to +85 | °C   |  |

| Storage Temperature Range                                                              | Tstq            | -55 to +150                                               | °C   |  |

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields: however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are field to an appropriate logic voltage level (e.g., either VSS or VCC).

### THERMAL CHARACTERISTICS

| Characteristic     | Symbol | Value | Unit |

|--------------------|--------|-------|------|

| Thermal Resistance |        |       | +    |

| Plastic            |        | 120   | - 1  |

| Ceramic            | θJA    | 60    | °C/W |

| Cerdip             |        | 65    | İ    |

### POWER CONSIDERATIONS

The average chip-junction temperature, T<sub>J</sub>, in °C can be obtained from:

T<sub>J</sub> = T<sub>A</sub> + (P<sub>D</sub>•θ<sub>JA</sub>)

Where:

(1)

TA = Ambient Temperature, °C

$\theta_{JA}$  = Package Thermal Resistance, Junction-to-Ambient, °C/W

PD=PINT+PPORT

PINT=ICC × VCC, Watts - Chip Internal Power

PPORT = Port Power Dissipation, Watts - User Determined

For most applications PpORT

PINT and can be neglected. PpORT may become significant if the device is configured to drive Darlington bases or sink LED loads.

An approximate relationship between PD and TJ (if PPORT is neglected) is:

$P_D = K + (T_J + 273^{\circ}C)$

Solving equations 1 and 2 for K gives:  $K = P_D \cdot (T_A + 273 \cdot C) + \theta_{JA} \cdot P_D^2$  (2)

Where K is a constant pertaining to the particular part. K can be determined from equation 3 by measuring PD (at equilibrium) for a known TA. Using this value of K the values of PD and TJ can be obtained by solving equations (1) and (2) iteratively for any value of TA.

### DC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5.0 Vdc ±5%, V<sub>SS</sub> = 0, T<sub>A</sub> = T<sub>L</sub> to T<sub>H</sub> unless otherwise noted )

| Characteristic                                                                                                                                               | Symbol | Min                | Typ          | Max         | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------|--------------|-------------|------|

| Input High Voltage                                                                                                                                           | VIH    | VSS + 2.0          | <del>-</del> | Vcc         | T V  |

| Input Low Voltage                                                                                                                                            | VIL    | VSS-0.3            | _            | VSS+08      | Ιċ   |

| Input Leskage Current         R/W, CSO, CS1, CS2, Enable           (Vin = 0 to 5.25 V)         RS, Rx D, Rx C, CTS, DCD                                      | lin    | -                  | 1.0          | 2.5         | μА   |

| Three-State (Off State) Input Current D0-D7 (Vin = 0.4 to 2.4 V)                                                                                             | ITSI   | -                  | 2.0          | 10          | μА   |

| Output High Voltage $D0-D7$ $(I_{Load} = -205 \mu A, Enable Pulse Width < 25 \mu s)$ $(I_{Load} = -100 \mu A, Enable Pulse Width < 25 \mu s)$ $Tx Data, RTS$ | Vон    | VSS+2.4<br>VSS+2.4 | -            | -           | v    |

| Output Low Voltage (I <sub>Load</sub> = 1.6 mA, Enable Pulse Width < 25 µs)                                                                                  | VOL    |                    |              | Vss+0.4     | l ∨  |

| Output Leakage Current (Off State) (VOH = 2.4 V) IRO                                                                                                         | ILOH   |                    | 1.0          | 10          | #A   |

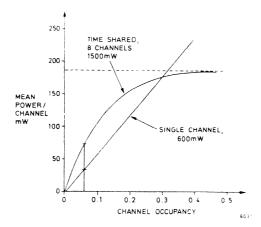

| Internal Power Dissipation (Measured at TA = TL)                                                                                                             | PINT   |                    | 300          | 525         | mW   |

| Internal Input Capacitance (V <sub>in</sub> = 0, T <sub>A</sub> = 25°C, f = 1.0 MHz)  E, Tx CLK, Rx CLK, R/W, RS, Rx Data, CS0, CS1, CS2, CT5, DCD           | Cin    | -                  | 10           | 12.5<br>7.5 | pF   |

| Output Capacitance RTS, Tx Data $(V_{in}=0,T_A=25^{\circ}C,f=1.0\text{MHz})$ IRQ                                                                             | Cout   | -                  | -            | 10<br>5.0   | pF   |

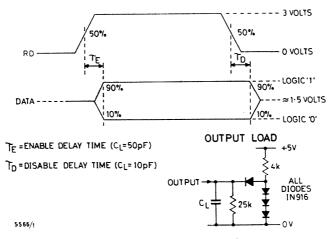

SERIAL DATA TIMING CHARACTERISTICS

| Characteristic                                                   |                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | MC8950       |                    | BA50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MC68B50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                 |