ARGUS BOOKS

ASSEMBLY LANGUAGE PROGRAMMING FOR THE

## AMSTRAD CPC 464,664 & 6128

A.P. & D.J. STEPHENSON

## Assembly Language Programming for the AMSTRAD CPC 464/664/6128

# Assembly Language Programming for the AMSTRAD CPC 464/664/6128

A.P. & D.J. STEPHENSON

Argus Books Ltd 1 Golden Square London W1R 3AB

© Argus Books Limited 1986

ISBN 0 85242 861 8

All rights reserved. No part of this publication may be reproduced in any form, by print, photography, microfilm or any other means without written permission from the publisher

## **Preface**

We hope that this book will persuade readers that machine code, entered with the help of an assembler, is worth learning. The reader should have some experience of BASIC, together with an understanding of simple computer terms. Anyone entirely new to computing and who may have just bought an Amstrad should study the User Instructions first, before tackling this book.

Machine code programs execute in a flash and take up far less memory than an equivalent program written in BASIC. This is why most commercial software, including arcade games, are written in machine code.

Although written for the Amstrad, the book should also be helpful to those who own other machines that incorporate the Z80 microprocessor – the Spectrum for example. Experience of machine code, using 8-bit micros, is never wasted because most of the techniques involved will still apply to the new breed of 16 or 32 bit micros.

Some readers may be a little surprised by the scarcity of 'remarks' in the program listings. For experienced programmers, there can be no denying their importance. For those trying to learn machine code from scratch, the sparse language and cryptic abbreviations used in the typical 'remark' column can be more confusing than helpful. Instead, we have included a line-by-line description in the accompanying text.

We have stressed, quite early in the book, that an assembler is a powerful weapon in the battle against machine code. We realise, however, that some readers may be content to struggle along without one so a simple hex loading program is featured which should reduce the boredom associated with POKEing program bytes into memory.

The complete Z80 instruction set is presented as an Appendix and is laid out in a special format which, we hope, will provide an easy-to-read reference source. Detailed descriptions of the most commonly used Z80 instructions are given in Chapter 6.

Where applicable, descriptions are supported by example program listings. Some of these listings will be found to have

immediate practical value while others may serve as useful guidelines for the development of other programs. Special attention has been given in the early chapters to the design of loops and conditional branching because these are areas which provide a rich breeding ground for bugs. Several full length subroutine listings appear in the later chapters, each supported by detailed explanations which should help those wishing to introduce modifications.

Resident System Extensions, known as RSXs, provide a means of adding extra commands to the operating system repertoire. We have devoted considerable space to the techniques involved, including practical machine code listings which can be called as an RSX from BASIC.

Attention has been drawn to the advantages of writing 'relocatable' machine code so we have shown, with practical examples, how to convert normal code to a relocatable form.

The final chapter explains how the movement of 'shapes' on the screen can be made free from flicker and without the jerkiness which is so irritating in animated sequences.

AP and DJ Stephenson

### **Contents**

#### 1 Why machine code?

1

Good points of BASIC. Defects of BASIC. Translating high-level languages. Compilers and interpreters. Assemblers. Binary machine code. Hexadecimal machine code. Mixing BASIC with machine code.

#### 2 Machine hardware

10

Hardware. Logic chips. The Z80 microprocessor. The address bus. The data bus. The control bus. The clock. RAM chips. ROM chips. Overlay. Addressing problems. Start-up conditions. The ULA chips. The CRT controller. The memory map. Disc workspace.

#### 3 Binary and hexadecimal

21

Digital versus analogue computers. Representing numbers by switches. Bits and bytes. Ways of arranging bits. Nybbles. Naming individual bits. Binary addition. Double byte numbers. Signed numbers. Two's complement numbers. Circle of signed numbers. Unsigned binary. Decimal and binary conversion. Hexadecimal. Converting hex to decimal. Adding hex numbers. Binary coded decimal. Adding in BCD format. Use of BCD. Logical operations. AND, OR and XOR.

#### 4 Entering and running programs

38

Using an assembler. The HiSoft DEVPAC assembler. Listing source code. Assembler options. Pass 1 and 2 errors. Assembler directives. Object code. Using the BASIC loader. Saving and retrieving code. Saving source code. Loading source code. Saving object code. Renumbering source code. Executing object code. Assembler manuals.

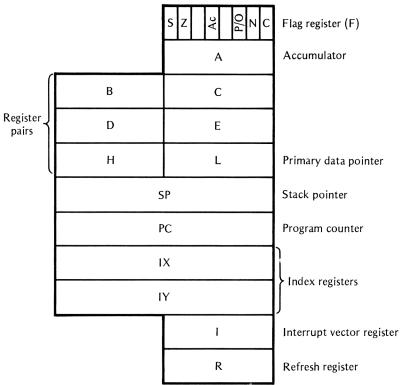

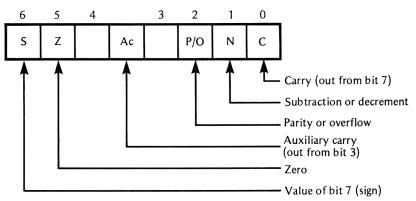

Registers. Source and destination rules. The single length registers. Register pairs. The index registers. The stack pointer. Use of the stack. The program counter. The flag register.

#### 6 Commonly used instructions

63

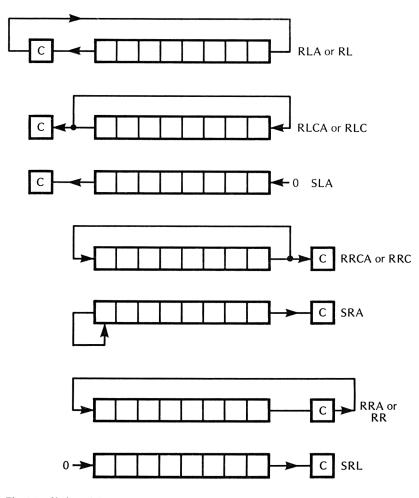

Instruction mnemonics and operands. Addressing modes. Implied addressing. Direct addressing. Immediate addressing. Indexed addressing. Register indirect addressing. Indexed addressing. Operation codes. Clock cycles. Bytes taken. Flags update. Load instructions. Arithmetic instructions. Logical instructions. Incrementing and decrementing. Stack operations. Conditional jumps. Unconditional jumps. Subroutine calls. Comparisons. Bit tests. Shift and rotate instructions. Operation code details. Relative jump bytes.

#### 7 Using resident firmware

86

Free software. Jump blocks. Commonly used resident subroutines.

#### 8 Addition and subtraction

92

Numerical range limitations. 8 bit addition and subtraction. 16 bit addition and subtraction. 32 bit addition and subtraction.

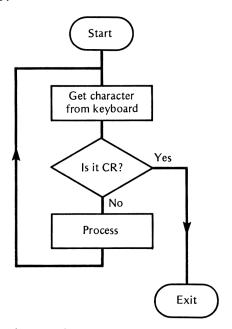

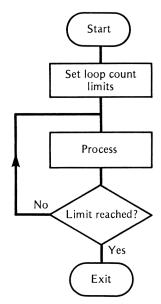

#### 9 Decision making and loop structures

101

Testing for zero, non zero, less than zero and greater than zero. Simple loop structures. Double byte up-counting and down-counting. Preserving register contents. Branching according to sign. Using the BIT test.

#### 10 Multiplication and division

118

8 bit unsigned multiplication. 16 bit unsigned multiplication. 16 bit signed multiplication. 8 bit unsigned division. 16 bit unsigned division. 16 bit signed division.

#### 11 Input and output

139

String input. String output. Text output. Decimal input. Hexadecimal input. Decimal output. Hexadecimal output.

161

| 12 | Parameter passing and introduction to resident system |  |

|----|-------------------------------------------------------|--|

|    | extensions                                            |  |

Parameter blocks. Fixed locations. Using the stack. Executing machine code from BASIC. Sorting of BASIC string arrays. Logging on an RSX. External command tables. Name tables.

### 13 Self relocation of subroutines and resident system extensions

185

Dynamic allocation of memory. Self relocation of object code. Location independent object code. Converting existing code to a self relocatable RSX. Programming the user restart (RST 6). Converting absolute addresses to relative. Look-up tables. String arrays Quicksort RSX. Loading and testing the RSX. Parameter passing from BASIC to an RSX. Executing an RSX from BASIC. RSX for sorting rectangular arrays. Using rectangular arrays efficiently. How BASIC organises a rectangular array. The RSX loader test program. Producing a binary file of an RSX.

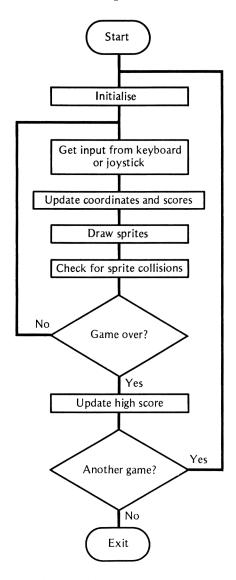

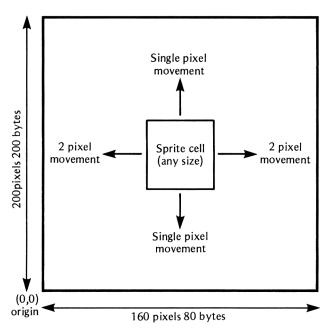

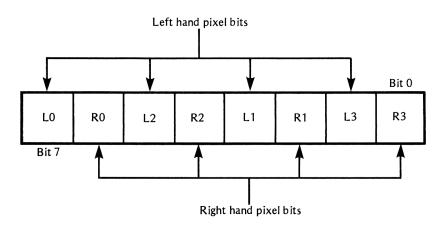

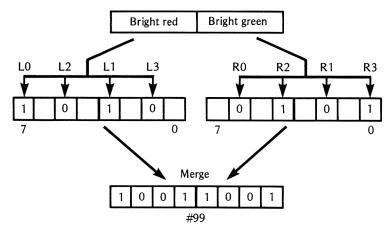

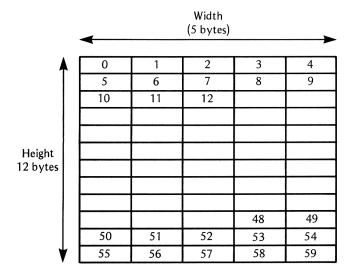

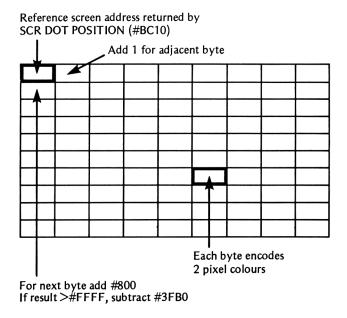

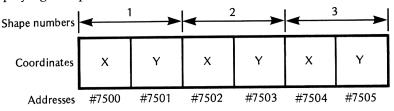

#### 14 Graphics and direct screen addressing

213

Using resident firmware routines. Typical action games. Organisation of screen memory. Mode zero. Shape tables for Mode zero. Placing a shape at screen coordinates X,Y. Addressing screen memory directly. Frame flyback. Moving a multicoloured shape. Moving multicoloured shapes independently. Co-ordinate blocks. Shape tables.

#### **Appendices**

Index 244

## Why machine code?

It takes an extra effort to learn machine code, and to persuade you that it's worthwhile, this chapter discusses the properties of high-level languages such as BASIC, the various methods of entering programs and explains the differences between compilers, interpreters and assemblers.

#### Good points of BASIC

BASIC is the most popular computing language in present day use and, in spite of periodic abuse from the establishment, will probably remain so for some time. The reasons are not hard to find. With few exceptions, home microcomputers are designed with only one builtin computer language, BASIC, so it is understandable that the majority of home enthusiasts stick with it because they feel it to be the 'natural' language of the computer. There are other reasons, not least of which is the undeniable fact that newcomers to the computer revolution find BASIC not too difficult to pick up. The original designers of BASIC, John Kemeny and Thomas Kurtz of Dartmouth College USA, way back in 1964, purposely designed the language to suit those who wanted to use a computer in their work but were not prepared to study the rather difficult languages currently used by professionals at that time. Another advantage of BASIC is the relative ease with which program lines can be deleted or modified. In all fairness, we should point out that this advantage stems from the method of translation, rather than from the language itself.

#### Defects of BASIC

The above treatment has dwelt on the plus points of BASIC but there are some rather disagreeable features which continue to provide ammunition for the critics. One criticism is concerned with the speed of *execution*. Depending on type, complexity and programming skill, some BASIC programs can take quite a while to display the 'answers' on the screen. A few seconds' (or minutes') wait is easily tolerated during the first weeks of ownership because the natural fascination with a new toy clouds the critical faculties. However, after the settling in period has ended, even a few seconds can become irritating so the relatively slow execution speed of BASIC must be accepted as a justifiable criticism. (Why BASIC is slow will be explained later in this chapter.)

Another criticism concerns the amount of memory taken up by a program written in BASIC. As each BASIC line is entered, the bytes squandered tend to mount up at an uncomfortable rate. Home micros, even Amstrad machines, are far from lavish in the amount of RAM left over for user's programs. A sizeable chunk is always purloined by the resident software for purposes which come under the euphemistic heading of 'work space'. The situation is made even worse by the fact that the full BASIC program (the *source code*) must reside in RAM, in addition to the variable list, while the program is being run. The strict definition of source code will be tackled later but, in the meantime, it can be thought of as the program in the form that it was originally written and entered. This is the form which squanders RAM. Most other languages only require the machine code translation (called the *object code*) to remain in memory during run time.

Although execution speed and memory demands are often quoted by attackers of BASIC, by far the most savage criticism is its lack of *structure*. To exponents of the art, structure, a normally harmless little word, is a kind of religion. It would be out of place in this book to enter into lengthy discussions on what constitutes good structure in a program because the concept is not quite so important in machine code work. It is sufficient here to describe it as a set of rules and guidelines for writing programs which are easy to follow and easy to amend. It is not easy to write good structured programs in BASIC because the language was designed without regard for structure. Many other computer languages such as Algol and Pascal were designed specifically for the writing of structured programs. Fortunately, BASIC has gradually changed since its conception in 1964. Dialects of BASIC, now appearing in some modern microcomputers are far removed from the original crude Dartmouth version. Both the BBC and the Amstrad machines offer quite an advanced BASIC, allowing better structured programs to be written. At least it is possible in either of these machines to write a program without too many GOTO commands polluting the pages. (The GOTO command is responsible for the cursed 'spaghetti' programming.)

In spite of all these criticisms, the authors do not despise BASIC. There is no reason why you should give up BASIC to learn machine code. In fact, the two can live quite happily together. One can complement the other in many ways. The abuse, now hurled at BASIC, cannot be accepted without suspicion as to the motives of

those who practise it – in the words of the Bard, they 'protesteth too much'.

#### Translating high-level languages

Languages such as BASIC, Algol, Pascal and many others (there are over 1000 in all if various specialised languages are included in the total) are said to be *high-level*. A high-level language:

- (a) requires the assistance of *translation software* before the computer can understand it and,

- (b) is one in which each statement, command or keyword in the language, when translated, usually gives rise to many individual machine instructions.

In BASIC, for example, an apparently simple statement like PRINT TOTAL will, after translation, generate a surprising number of machine code instructions. This is due to:

- (a) the primitive nature of a computer at machine level and

- (b) the necessity for the translating software to cover worst-case situations. For example, the variable TOTAL could be holding a small number like 47 in one program but a huge number like 358,467,789 in another so the translation software must always be prepared for the worst.

#### Compilers and interpreters

There are two quite distinct classes of high-level language translators and we need to distinguish them with care. Before describing the difference, we must first introduce the terms *source* code and *object* code.

Source code is the program as written in the original language. A program written in BASIC or Pascal is source code. Code in this form may be understood by you but not by the machine. Object code is the output from the translator. In other words, it is the set of machine code instructions which appear after the source code is translated. This time, the machine will understand it, but you may not.

#### Compilers

A compiler translates the entire source code into a *complete set* of machine code instructions. This is said to be the compiling stage and the source code is then said to be compiled. Once compiled into object code, the program can be executed (run). The original source code can then be released from occupying valuable RAM space. Pascal, Fortran, Cobol, Algol are examples of languages which are translated by a compiler. It takes a relatively long time for a machine to compile source code but it is only a one-off task. All subsequent

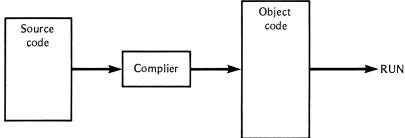

runs take place at machine code speed. From the beginner's point of view, a compiled language has one serious drawback. Once the program has been compiled, it is extremely difficult to debug or modify the object code. If it doesn't work first time, the source code must be re-entered before the fault can be corrected and the whole lot recompiled again which, as we have seen, is a lengthy business. Figure 1.1 shows the mechanism of compiler action.

Fig 1.1 Compiler action

#### **Interpreters**

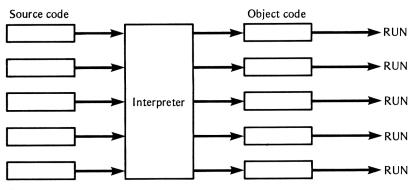

An interpreter does not translate all of the program in one go. Each line of the source code is translated and executed (run)) before the next line is translated. So the overall action is: translate a line, run it, translate the next line, run it, and so on. This means that the entire source code must remain in memory during run time. BASIC uses an interpreter. From the beginner's point of view, the advantage of an interpreter lies in the ease with which a program can be debugged or twisted around and re-run immediately. The disadvantages however, are serious. Since the source code must remain in memory during run time, valuable RAM space is occupied which limits the size of a program. Also the execution is dreadfully slow compared with compiler action because translation takes place every time the program is run. Figure 1.2 shows the mechanism of an interpreter.

Fig 1.2 Interpreter action

#### **Assemblers**

As far as this book is concerned, compilers and interpreters are not particularly important. They were introduced only as background material before introducing the assembler. Compilers and interpreters are concerned with the translation of high level languages. An assembler is a piece of software designed to aid the writing of direct machine code. Detailed treatment of an assembler is given in Chapter 4. It is sufficient at this stage to briefly describe assembler action. High-level interpreters generate many machine code instructions for each high-level statement. In contrast, an assembly language program is said to be low-level, meaning that, in general, one assembly code line generates only one machine code instruction. We could say there is a one-to-one relationship between an assembly code line and a machine code instruction. The primary objective of an assembler is to ease the task of constructing a machine code program. Instead of entering a long list of almost meaningless numbers, an assembler allows you to enter them in the form of code letters chosen, as far as practical, to be meaningful. They are called mnemonic codes because they aid your memory. A good assembler, in addition to allowing mnemonic code entries, will also provide sophisticated editing facilities, display of both source code and object code, means of storing either the source or object code on disc (or cassette tape) and various other little dodges which help to make life easier.

The terms source code and object code still apply to assemblers. The source code is the program written in assembly language and the object code is the translated version recognisable by the machine. The object code is said to be the assembled version. To 'assemble' means to translate to object code.

#### Is an assembler necessary?

An assembler is not provided free with the Amstrad machines. It is possible to enter a machine code program by a series of POKES from BASIC. Later, we shall be giving a complete listing of a BASIC program which will load any machine code program you like to write, providing the hex codes are entered in DATA statements. So, it would appear from this that the answer to the question 'Is an assembler necessary?', is no. This needs amplification. If you have patience above normal, if you are not easily frustrated, if you are willing to devote hours and hours to debugging and, above all, if you are blessed with a stable unemotional personality, then by all means save yourself some money and make do with POKEing. If, on the other hand you are a normal individual and intend to take up machine code seriously then you are strongly advised to go out and get hold of an assembler. Trying to write machine code without the assistance of an assembler is like trying to cut a lawn with nail scissors.

The current success of the Amstrad has stimulated software firms

to produce assemblers on tape, disc or in ROM. There is probably not much to choose between any of them, price for price, but the programs in this book have been developed using the official version, the HiSoft DEVPAC assembler. Its full title is as follows:

The HiSoft Assembler, disassembler, editor and monitor It can be obtained from AMSOFT or direct from HiSOFT. The price, at the time of writing is around £28. There are two versions, one for the CPC464 which is supplied in the form of a cassette tape and one supplied on disc for either the CPC464 with disc drive or the CPC664 and CPC6128 with built-in disc drives.

#### The advantages of using machine code

Before outlining the advantages, we should mention that 'machine code', is a rather loose term used to cover several different forms. There are in fact three different forms:

#### 1. Pure binary machine code

A program residing in RAM would appear as a series of pigeon holes, each containing a set of '1's and '0's. A program in this form is called pure binary machine code. The very early computers had their programs entered in this way by means of a series of panel switches. Mercifully, those days are ended but only because more humane ways have been thought up for entering code. Nevertheless, computers still only understand these '1's and '0's – the change has been in the method of entering, not the form in which they are finally held in memory. Here is an example of a short program segment to clear the contents of memory address 0025 hex, as it might appear written in binary machine code:

1001 0111 0011 0010 0020 0101 0000 0000

(It is pointless at this stage trying to work out how this, and the next two examples work.)

#### 2. Hexadecimal machine code

This is code entered in the form of a series of numbers which can be entered from a normal keyboard. A mixture of hardware and system software provides the necessary conversion to the equivalent binary '1's and '0's. Without an assembler, this is the form in which programs have to be entered. This is what happens when you POKE machine code or enter it by means of a loader. The numbers can be

in decimal or hexadecimal. Although decimal appears more natural for humans, hexadecimal will be found more natural for the machine and, with practice, easier for the human to communicate with it. Chapter 4 deals in detail with the hexadecimal system of numbers.

The program segment written in binary machine code shown above now follows as it would appear if written in hexadecimal machine code:

97

32

25

00

#### 3. Assembly code

Assembly code is best considered as the most elegant and the least error prone method of entering machine code. When we use assembly code we still speak of it as machine code so from now on, the term 'machine code' and assembly code mean the same thing. As a final example, here is how the same program would appear if written in standard Z80 assembler code:

SUB A LD (#25), A

#### Why learn machine code?

Quite understandably, anyone used to the comparative comfort of BASIC will not find machine code easy. Machine code is difficult, and it is best to understand what you are up against right from the start. There are many rewards for the extra effort involved. Let us list them:

- (a) A machine code program *can run much faster* than one written in BASIC. Depending on the type of program, anything from 10 to 1000 times as fast.

- (b) A machine code program takes up considerably less RAM space than the equivalent BASIC version.

- (c) Learning machine code will improve your understanding of computers because you are conversing directly rather than through a wall of translation software.

- (d) Animation routines, written in BASIC often appear jerky because of the slow execution time. Machine code versions give a greatly improved display. To drive this point home, we should take note of the fact that commercial games programs are almost always written in machine code.

- (e) It is possible to recoup the money spent on a computer, plus some extra, by selling your programs to a publisher or software house. However, very few commercial organisations accept pro-

grams written in BASIC, a condition which applies particularly to animated games.

(f) Mastering machine code can act as an ego boost. A shallow advantage perhaps but few of us are entirely without vanity.

#### Mixing BASIC with machine code

Until you gain experience, you would be well advised to mix BASIC with machine code subroutines. Rather than attempt to write complete machine code programs, be content with writing BASIC programs which call up machine code at critical points. Use BASIC lines for actions which are not sensitive to execution time and machine code where its properties justify the extra effort. For example, in a general purpose database, much of the program will work quite satisfactorily in BASIC but where it is required to search for a particular record, or to sort them in to some form of order, use machine code subroutines.

#### The microprocessor instruction set

A program written in BASIC for one make of machine will not necessarily run on another make. Although the majority of the statements and commands remain the same for different machines, there will be a few variants. In spite of this, it is usually a fairly simple job to modify a BASIC program, written for one make of machine so that it will run on another.

With machine code the program must be written to suit the particular type of microprocessor used, not the machine system as a whole. The microprocessor is the chip which forms the so-called 'brain' of a microcomputer and it will only understand machine code written in its own special language. For example, a program written in BASIC for, say the Commodore 64, can be persuaded to run on the Amstrad or the BBC machine, providing a few trivial changes are made. However, a program written in machine code for the Amstrad would have to be completely re-written before it could work on the Commodore 64 or the BBC machine because the Amstrad uses the Z80 microprocessor and the BBC and the Commodore 64 machines both use the 6502/6510. Studying machine code for the Amstrad, or any other machine which uses the same microprocessor, will involve learning the instruction set of the Z80. The instruction set of a microprocessor is the list of machine code instructions which it is capable of executing, together with the hexadecimal or mnemonic codes which it recognises. It is a formidable looking list of over 600 different instructions. Nobody in their right senses would attempt to memorise them all, in any case only a small percentage of them are in regular use. As long as you can learn how to read the instruction set, that is all that matters.

#### **Summary**

- 1 BASIC is relatively easy to understand but uses a lot of memory and is slow in execution.

- 2 BASIC, PASCAL and ALGOL are examples of high-level computer languages.

- 3 Each statement in a high level language is equivalent to a great many machine code instructions.

- 4 High-level language translators are either compilers or interpreters.

- 5 A compiler must translate the entire high-level program into machine code before it can be executed.

- 6 An interpreter translates, then executes, line by line.

- 7 Source code is a program in the original form. Object code is how it appears after translation to machine code.

- 8 An assembler is software designed to aid the writing of machine code.

- 9 Without an assembler, machine code can only be entered by POKE statements from BASIC.

- 10 Machine code executes rapidly and is economic on memory.

- 11 Machine code programs must be written to suit the microprocessor in use. In the case of the Amstrad, this is the Z80.

## 2 Machine hardware

The hardware and memory usage of the CPC 464 are described here, but much of the material is still valid for the later CPC664/6128 models.

#### Is hardware important?

In some respects, a computer is no different from a washing machine. Providing you know how to use it, knowledge of what's inside is of little importance. Certainly, if your use of a computer is restricted to buying and running commercial software there is no need whatsoever to concern yourself with hardware details. To a slightly lesser extent, you can maintain the same lofty indifference if you write your own programs in a high level language such as BASIC. After all, the general idea behind any high level language is to protect the user from the harsh realities of computer technology. A BASIC interpreter does just that by forming a cosy software blanket between the user and the machine. But the machine code enthusiast is normally a different kind of animal, who wants an in depth understanding, even if it does entail additional mental labour. The question now arises as to the level at which hardware needs to be studied by the newcomer to machine code. For example, considering that a computer is virtually 100% electronic in nature, is it necessary to study electronics? Fortunately for most of us, the answer is no. It may be useful to have a superficial electronic awareness but, unless you intend to go in for computer repairing or designing as a side line, you can get away with little more than lamp, battery and switch knowledge. Gone are the days when the circuit diagram of a computer stretched over hundreds of pages, each filled with resistor, capacitor and transistor symbols. All this complexity ended with the introduction of the integrated circuit, back in the middle sixties. In a modern home computer, such as the Amstrad, over 90% of the complexity is buried inside a handful of integrated circuits, ICs. The machine code enthusiast need not bother with the insides of the ICs. All he needs is a rough idea of the

function of each major IC and how they are connected together to form a computing system. The highly simplified version of the system can then be reduced to one or two block diagrams. That is to say, diagrams containing 'boxes', representing the ICs, connected to bundles of wires called buses. A bus is the term used for a set of wires, all conveying the same kind of information. The address bus, the data bus and the control bus are concepts which will be mentioned frequently during this chapter. However, before continuing, we should make it plain that information given in this chapter is not absolutely essential for the machine code programmer. You don't have to understand what follows. All we can say is that the knowledge will not be wasted. It will help you appreciate the finer points of the art and, more importantly, it will help you understand what is actually happening in the computer when you later write, say,

LD A, (HL).

#### Logic chips

Logic is a much abused term. In everyday speech, it usually means clear thinking. In computer language, it means circuits which can only be in *one of two states*, called either ON or OFF, or 1 and 0. Apart from a few exceptions, all wires on the computer board are either in the '1' state (voltage around three to five volts) or the '0' state (voltage around zero to one volt state). Complex logic systems are based on a few building bricks known as *logic gates*. These have a single output and, normally, several inputs. The output of a logic gate depends on the right combination of '1's and '0's being present on the inputs. ICs may contain hundreds or even thousands of internal logic gates, all interconnected to form an overall subsystem. All subsystems are synchronised by an electrical oscillator known as the *clock*. The clock is driven by a *quartz crystal* in order to maintain frequency stability. In the Amstrad, the clock frequency is maintained at 16 million oscillations per second (16 MHz).

#### The Z80A microprocessor

There is one particular chip in the Amstrad, and indeed in all home and personal computers, which actually does the computing. This chip is called the *microprocessor* and, in the Amstrad CPC464/664/6128 machines, it bears the type number Z80A. All other chips in the system are subservient to it. It is capable of responding to outside instructions which 'tell' it whether to add, subtract, fetch some data from memory etc. The instructions must be given in patterns of '1's and '0's because it only understands *binary* and can only perform with binary numbers (Chapter 3 treats binary in detail). Needless to

say, it doesn't understand a word of English. Furthermore, it can only respond to instructions which are within a limited repertoire known as the *instruction set*. The Z80A has a particularly rich set of over 600 instructions. You may think this is a bewildering number from which to pick out the one you want but when grouped together, according to respective functions, we find that those in the same group are merely subtle variations on a main theme. All data into or out of the Z80A takes place via *registers*. The Z80A is well equipped with registers, details of which are in Chapter 5.

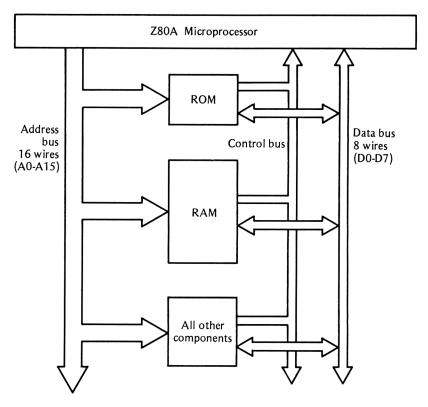

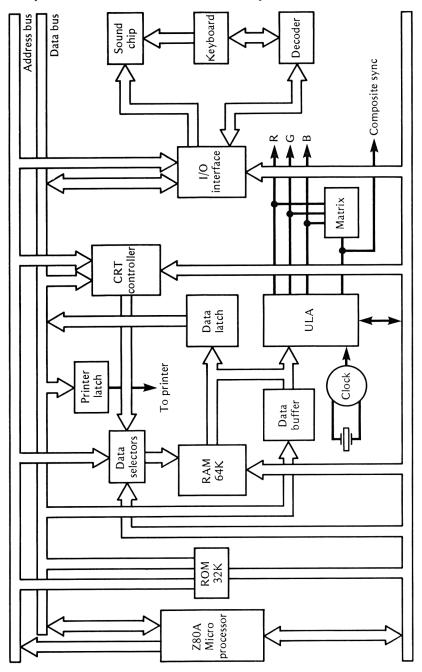

Figure 2.1 is our first block schematic. It is a highly simplified version of the Amstrad circuit board intended only to illustrate the central position of the microprocessor in relation to the general scheme of things.

Fig 2.1 The microprocessor and buses

All information between the microprocessor and the rest of the main components (lumped together as one box) take place via three buses.

#### The address bus

Each memory cell (and certain auxiliary components) is identified by

a unique binary code known as its *address*. So when a particular cell is to be activated, the microprocessor sends out the personal code of this cell down the address bus. Cells ignore all address signals other than their own. There are two important details to note:

- 1 The direction arrows on the diagram show that the address bus is *one-way*. Address codes can only originate from the microprocessor and travel *down* the bus.

- 2 There are 16 wires in the bus, (labelled A0 to A15) so there is an upper limit on the number of different addresses. Chapter 3 gives reasons why this limit can not exceed 65,536 different addresses. Decimal numbers such as this are not easy to memorise. Large numbers are best expressed in terms of 'K'. One K in computer jargon is 1024 (2<sup>10</sup>) not 1000. In termsof K, the number 65,536 is reduced to a nice round figure of 64K. (64×1024=65,536.) The lowest address is address 0 and the highest is address 65,535. We shall learn in Chapter 3 that, when working in machine code, addresses are far better expressed in the *hexadecimal* (hex) number system. In terms of hex, the address range is from 0000 to FFFF.

#### The data bus

This is an 8-wire bus (labelled D0 to D7) which carries *data* between the microprocessor and the rest of the system. All 8 bits (known as *one byte*) are transferred simultaneously along the data bus. Note that the direction arrow, unlike the one for the address bus, is *two-way* which means that data can pass to the external devices (called *writing*) or from the external devices (called *reading*). The fact that the data bus is 8 bits wide, brands the Z80A as an '8-bit' microprocessor because only numbers which can be held within the compass of 8 bits can be transferred in one go. The highest absolute decimal number using 8 bits is only 255 so larger numbers must be fetched in 8-bit instalments.

At this point, perhaps we should mention 16-bit microprocessors which are heralded as forming the new generation of home computers. A true 16-bit microprocessor, apart from whatever other qualities it may have, is one which has a full 16 bit data bus. A few so-called '16-bit' machines which are now on the market do indeed have microprocessors which, internally at least, operate on 16 or even 32 bit numbers simultaneously. But they employ one of the cheaper versions of the 16 bit family which only have an 8 bit data bus. This means that 16 bit data still has to be transferred in two instalments.

#### The control bus

The control bus, unlike the address and data buses, is a bundle of odds and ends, a hotch potch in fact. Each wire has an entirely distinct function. Some carry orders from, and some carry requests to, the microprocessor. For example, one of them will be the read/write control line, another will carry the clock signal and another will be the reset line.

Figure 2.2 gives a more detailed picture of the microprocessor and components, and is an advance on the previous block schematic

Fig 2.2 The block schematic of the Amstrad 464 and 664

although even this is still an enormously simplified version of the true picture. Nevertheless, the detail shown is more than adequate for our purpose.

#### The clock

This runs at 16 MHz for direct drive to the ULA (see later) but counted down by a factor of four to drive the microprocessor at 4 MHz. However, a slight complication arises because of the need to synchronise with the video scanning circuits. This has the effect of reducing the effective clock rate to 3.3 MHz.

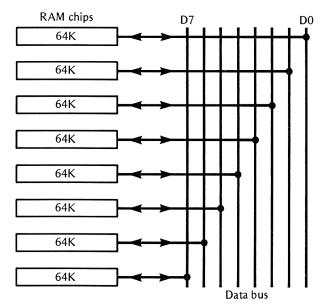

#### The RAM chips

The total complement of read/write memory is contained in *eight identical chips*, each capable of storing 64K separate data bits. Because there are eight of them and because each contributes one bit of data, they collectively act as a 64K byte memory. The address inputs of the RAM chips are fed from the address bus, and the eight separate data wires are connected to the D0 to D7 lines of the data bus. Figure 2.3 illustrates the RAM chip connections.

Fig 2.3 RAM chip connections

One of the lines (labelled R/W) in the control bus is also connected, albeit indirectly, to the RAMs for controlling the *direction* of data flow. That is to say, whether data is to be read from or witten to RAM.

#### The ROM chip

The single ROM chip holds 32K of permanent programs. Programs

held in ROM are known under the collective title of *firmware* rather than software. Although in a single chip, the ROM should be considered as two functionally separate 16K ROMS, the 'lower' and the 'upper'.

The *lower* ROM occupies the address range 0000 to 3FFF hex and contains the *Operating System*. Duties under the heading of the operating system include reading the key board, handling peripherals, sending information to the screen display circuitry etc. In short, all the various mundane duties which help to provide a friendly man/machine interface. The success of any machine, whatever other qualities it may have, can stand or fall on the quality of the operating system. Only programmers of high calibre are employed in writing operating system firmware. Needless to say, firmware is written in machine code.

The upper ROM contains the BASIC interpreter firmware and occupies addresses C000 to FFFF hex. It contains all the translation rules for converting BASIC programs into machine code. The quality of the Amstrad BASIC interpreter is excellent.

#### Addressing problems

Most home computers take the easy way out and restrict the total RAM and ROM complement so as to fit comfortably into the available 64K addressing space of 8-bit microprocessors. (You will remember that a 16-bit address bus can only supply 64K different addresses.) But, Amstrad has 64K of RAM and 32K of ROM! This apparent violation of the laws of address combinations obviously calls for some explanation. The problem is overcome by bank switching. The upper and lower ROMs 'overlay' the RAM areas beneath them. That is to say, the areas of RAM, which underlay the ROMs, share each other's addresses. This is all very nice but an obvious problem remains. Since parts of RAM and ROM share the same addresses, how does the system distinguish between them? The problem is sorted out by the mysterious ULA but is helped by the following reasoning:

- 1 If the instruction is to write to memory, it must mean the RAM because you can't write into a ROM.

- 2 If the instruction is to write or read to any address between 4000 and BFFF hex, it must be RAM because there is no ROM in this area.

- 3 If it's reading information from ROM areas, it can be from either ROM or the underlying RAM. This is where the ULA takes over and decides whether the ROM should be isolated, leaving the coast clear for the RAM or vice versa.

The above description has been based on the normal (default) conditions of the Amstrad. However, it is possible to modify this arrangement by a certain machine code call. Thus it is possible to

disable one or both ROMs although such adventures are best left until your experience has matured a little.

#### Start up conditions

On first switching ON, the lower ROM takes over, resets all devices and clears all RAM locations. On completion, control switches to the upper ROM, ready for the first BASIC command.

#### The ULA

Computers, up to a few years ago, used to bristle with logic chips, most of which performed primitive gating functions. Reliability is inversely proportional to the chip count so designers were constantly searching for ways to reduce the number without sacrificing sophistication. One ingenious solution was the *Uncommitted Logic* Array (ULA for short). The idea is to construct a large number of separate gates on one chip with provisions for 'burning in' the interconnections between them afterwards. This means that the chip was initially undedicated to any particular function. The actual burning in stage is left until the end user supplies a plan of the final interconnections. When this is done, the once uncommitted ULA becomes committed to undertake a complex but specific task. It becomes a customised chip, capable of replacing a large number of untidy separate chips. The ULA solution is commercially viable for bulk orders in excess of, say, 20,000. The cost per chip of the final burning in process is excessively high for small quantities.

The ULA in the Amstrad is labelled IC 116 on the circuit diagram and is responsible, amongst other things, for the following:

- (a) Dividing the clock frequency by four to feed the Z80A.

- (b) Controlling the data selectors which switch the address bus between the video controller and the Z80 on a time ratio of 3 to 1.

- (c) Indirectly controlling the colour of the screen output characters by means of a *palette latch*. The input to the palette latch is derived from the data bus (because the programmer decides the colour) and the output is in the form of a five bit code. Decoder circuits in the ULA reduce this to the three Red, Green and Blue (RGB) wires which feed the colour monitor. There is one mystery here. It is possible to program up to 27 different colours and yet there are only three wires! The answer is to feed them with *tristate* instead of *two state* logic. Thus, each of the separate RGB outputs have been arranged so that they can rest in any one of three states, logic 1, logic 0 or virtually open circuit. Three wires, each capable of resting in any one of three states, are capable of  $3^3$ =27 combinations.

- (d) Periodically switching in the Cathode Ray Tube Controller (CRTC) to the screen RAM. It does this by *interrupting* the microprocessor every few instruction cycles.

#### The CRT controller

This is a standard commercial chip bearing the type number 6845. It

is quite a complex affair with eighteen internal registers and is almost as flexible as a microprocessor. It is a *peripheral*, in the sense that it has a port address block which can be activated by the BASIC instructions INP and OUT. However, most of the CRT controller registers are loaded by the operating system ROM and require no help from us. It performs, by hardware, a large number of screen operations, including scrolling, sync, high-res graphics and text positioning. A less complex CRT controller would require extra software in the ROM to achieve the same control of the screen.

#### Data selectors

Referring to Figure 2.2, the block marked 'data selectors' consists of 4 chips, responsible for steering the data bytes to RAM from either the Z80A or the CRT controller. The chips act like 8-way, two-pole switches controlled by the ULA.

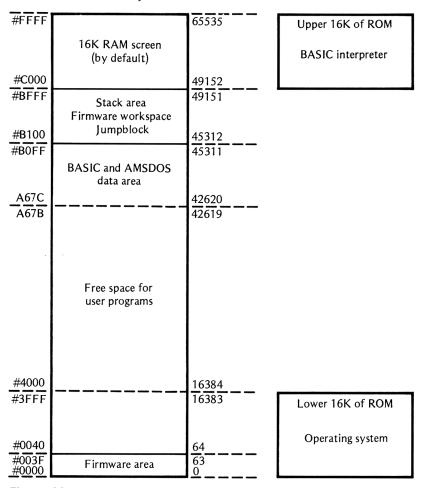

Fig 2.4 Memory map

#### The memory map

The memory map of the Amstrad is shown in Figure 2.4. For convenience, the memory addresses have been given in both decimal and hex. To indicate hex numbers, we have used the character '#' because it conforms to the notation used by the Hisoft DEVPAC assembler.

The map shows the areas in which the upper and lower ROM addresses overlay RAM. Note the *stack* (explained in later chapters) is left by the operating system in a position below the screen RAM area.

#### The sound generator

The Amstrad sound effects are produced by the industry standard AY-3-8912 chip. It is connected via the input-output interface. It is possible to program the hardware registers direct but it would be a dangerous procedure because of its close linkage with the keyboard scanning. This is a highly critical area because of precise interrupt timing.

#### Disc workspace

The Amstrad CPC664/6128, or the 464 fitted with a disc drive, requires an extra 1284 bytes of RAM for the disc operating system (DOS) workspace. This means that HIMEM will be lowered from #ABFF (44031) down to #A67B (42619). Some lengthy programs written for the 464 on tape may not work if a disc drive has been added. The solution is to leave the disc drive switched off. On the 664, the DOS is always on so the simple solution won't work. However, an excellent software patch for overcoming the problem has been designed by Cliff Lawson (see 'Amstrad User' magazine, July 85 issue).

#### **Summary**

- 1 A bus is a bundle of wires, each conveying the same kind of information.

- 2 The 16 wire address bus carries the code for selecting one particular memory cell.

- 3 The 8 wire data bus conveys data bytes around the system.

- 4 The control bus contains a mixture of wires (so it is not a true bus) each having a specific control function.

- 5 Logic, in computer parlance, refers to any two state switch system. The states can be called 1 and 0, ON and OFF or HIGH and LOW.

- 6 A logic gate has one output, the state of which depends on the logic combination applied to the inputs.

- 7 A 16 MHz clock is the source of all timing pulses in the Amstrad machines.

- 8 The clock frequency is divided by 4 to obtain the 4 HMz drive to the Z80A microprocessor.

- 9 Due to the requirements of video scanning, the effective Z80A clock frequency is reduced to 3.3 MHz.

- 10 The read/write memory consists of 64K of RAM.

- 11 The read-only memory is a 32K pre-programmed ROM.

- 12 Permanent programs in ROM are known as firmware.

- 13 The upper 16K of ROM contains the BASIC interpreter firmware and the lower 16K contains the Operating System.

- 14 A 16 wire address bus can only manage 64K different address combinations so ROM addresses overlay some RAM addresses.

- 15 The upper ROM overlaps the screen RAM (C000 to FFFF hex.)

- 16 The lower ROM overlaps the operating system workspace (0000 to 3FFF hex).

- 17 The ULA is a customised chip responsible for a range of assorted switch actions.

- 18 The RAM screen area, the upper ROM and the CRT controller all share RAM addresses. The ULA arranges the periodic switching at speeds transparent to the user.

- 19 The ULA also takes care of the colour palette decoding, mode information, and composite sync generation.

## Binary and hexadecimal

#### Digital versus analogue computers?

The term 'computer' is well established. So we are inclined to forget that there are two species and that when we speak of the computer age we are automatically referring to the digital, rather than the analoge, species. And yet, the analogue computer came first mainly because the physical characteristics of the real world can be modelled more naturally by analogue techniques. Ignoring sudden volcanic eruptions or similar violent catastrophies, physical changes in the real world take place in a smooth orderly manner. For example, wind speed will not suddenly jump from 10 mph to 20 mph. A plot of windspeed against time will always be a smooth curve. It may be a steep curve during the onset of a storm but it will still be smooth providing, of course, that enough plotting points are taken. The same can be said of temperature changes. Even the dramatic heat rise at the beginning of a nuclear explosion may appear instantaneous but the temperature plotted at nanosecond intervals would still show a steep, but nevertheless smooth, curve. Nature, apart from some rather weird 'quantum' behaviour at subatomic levels, seems to dislike sudden jumps. Measurement of physical quantities is carried out with instruments which convert them to an analogous form, which we will assume here to be electrical, and are therefore known as analogue instruments. These instruments give readings, usually in the form of a voltage, which are, as far as possible, proportional to the physical quantity. For example, a wind velocity instrument may be calibrated such that each additional volt represented an increase of 5 miles per hour. But whatever the physical quantity, the essential ingredient of any electrical analogue device is that a certain voltage (or perhaps current) corresponds to a particular value of the physical quantity. In the case of our example wind measuring instrument, 1 volt= 5 mph, 2 volts=10 mph and 20 volts= 100 mph. How can we use analogue methods for manipulating numbers? In other words, how is an analogue computer constructed, assuming it is capable of addition, subtraction, multiplication, division and all the common-

place trigonometrical operations. All we need is a panel full of knobs which we can adjust to represent the numbers, a collection of fairly straightforward electrical circuits which can add, subtract etc and a few meters to present the results in a visual form. Indeed, this is exactly what a commercial analogue computer looks like. Such instruments still have a place in laboratories and are superior in some respects to the digital computer, particularly in their ability to handle complex differential equations. They have two drawbacks. Firstly, they require highly skilled operators to set up all the knobs and to check the preliminary reset conditions. Secondly, the analogue circuitry requires frequent adjustment to counteract voltage drifting caused by heat changes. The accuracy of an analogue computer relies absolutely on the accuracy of a voltage or current reading. Even with modern circuitry, equipment designed for voltage tolerances better than 1 part in 1,000 would be quite costly. This means that any attempt to use an analogue computer to work out a balanace sheet for a business organisation would fail the first auditor's check.

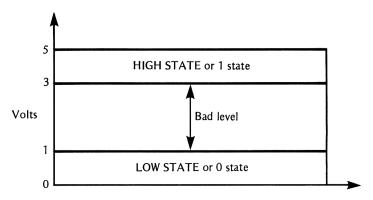

A digital computer overcomes all problems caused by measurement errors. In fact, the term 'accuracy' doesn't really apply to the digital computer because measurement is not part of its nature. Instead of *measuring*, the digital computer *counts*. To humans, counting can be tedious and error prone but a machine built to count, rather than measure, can be foolproof. The circuits of a digital computer need only be designed to detect whether a voltage is above a certain upper threshold limit or below a certain lower threshold limit. In other words, any individual circuit is always in the 'LOW' state or the 'HIGH' state. In the case of the Amstrad and most other current microcomputers, the two levels are approximately as follows:

Voltage between 3 to 5 volts is the HIGH state. Voltage between zero to 1 volt is the LOW state.

The terms HIGH and LOW were chosen to suit electronic engineers but, from a computing point of view, it is better to adopt the terms 1 and 0 respectively. Figure 3.1 may help you to visualise these states.

#### Representing numbers by switches

Almost all circuits in a digital computer act as electronically operated *switches*, capable of changing rapidly from one state to the other on receipt of an appropriate signal. A series of switches can be made to represent numbers providing we are prepared to dispense altogether with the familiar decimal system and adopt the primitive numbering system known as *binary*. Decimal is out because it would

Fig 3.1 The two digital states

require a ten state electrical system. In other words, it would be necessary to revert back to an analogue system in which each circuit would have to respond to ten different levels of current or voltage. This demands expensive circuitry and frequent calibration. There are no calibration problems with a switch because it is either ON (the 1 state) or OFF (the 0 state)

#### Bits and bytes

Only the digits 1 and 0 are allowed in the binary counting system so it is inherently simple. The term bit, derived from binary digit, refers to either a 1 or 0. A string of eight bits is nowadays called a byte. The numerical value of each bit is based on 'place weighting', similar to decimal. However, each bit is worth twice as much (instead of ten times as much) as the bit on its right. For example, the byte 00001111 is equal to 15 in decimal because, proceeding from right to left, we have a 1 and a 2 and a 4 and an 8. Study the following examples:

$00001001 = 9. \ 00000101 = 5. \ 00101110 = 46. \ 111111111 = 255. \ 10000000 = 128.$

#### Number of ways of arranging bits

With two bits, there are 4 possible patterns, 00, 01, 10 and 11. With 3 bits, there are 8 patterns, 000, 001, 010, 011, 100, 101, 110 and 111. Instead of laboriously writing down all the possible arrangements of bits in a given string, we can use the following general rule:

Number of ways=2<sup>N</sup> (where N=the number of bits)

For example, for 8 bits, there are  $2^8$ =256 ways. Every time we add one more bit to the string length, we double the possible number of arrangements.

#### **Nybbles**

It is convenient to consider the byte in two halves, each known as a nybble and to introduce a space between them. For example, 0010 1101 is easier on the eye than 00101101 although it is important to remember that the space is quite artificial and has no arithmetic meaning.

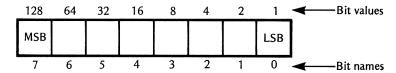

#### Naming individual bits

When referring to individual bits in a byte, the terms illustrated in Figure 3.2 are well standardised. The bit on the extreme right, named bit 0, is the *least significant bit* (1sb) and the bit on the extreme left, named bit 7, is the *most significant bit* (msb). Note carefully, because there is a chance of confusion, that the bits are numbered 0 to 7, not 1 to 8.

#### Binary addition

The process of adding two binary numbers together is essentially the same as we use for adding decimal numbers. In decimal, when the sum of a column exceeds 9, we carry a 1 over to the next higher significant column. In binary, a carry is made whenever the sum of a column exceeds 1. Rather than explain the procedure in detail, it is eaier to study a few examples, using complete bytes.

| To add 1 to 1:   | 0000 0001=1<br>0000 0001=1   |

|------------------|------------------------------|

| Sum              | 0000 0010=2                  |

| To add 3 to 5:   | 0000 0011=3                  |

|                  | 0000 0101=5                  |

| Sum              | 0000 1000=8                  |

| To add 17 to 31: |                              |

|                  | 0001 0001=17<br>0001 1111=31 |

| Sum              | 0011 0000=48                 |

|                  |                              |

Fig 3.2 Naming the bits

# Double byte numbers

The Z80 micro processor is an eight-bit device. This means that all trips to and from memory take place in bundles of eight bits. This is why, up to now, we have concentrated on the byte. The trouble with the single byte is the limited storage capacity. The maximum binary number (every bit a 1) which can be held in one byte is only equivalent to 255 decimal. Obviously, a computer would not be much use if it could only handle numbers up to this value. The way out is to use two or more bytes for each number by considering them to be arranged *end to end*. Assume we use two bytes and fill them both with '1's as follows:

#### 1111 1111 1111 1111

This is equal to 65,535 decimal. You can of course check this by adding up the value of each binary digit but there is an elegant formula which, providing you have a scientific calculator handy (or the Amstrad in direct mode), can do the job quickly,

Largest number in a string of N bits is 2<sup>N</sup>-1

For example,

```

4 bits can hold 2<sup>4</sup>-1=15

8 bits can hold 2<sup>8</sup>-1=255

16 bits can hold 2<sup>16</sup>-1=65,535

20 bits can hold hold 20<sup>20</sup>-1=1,048,575

```

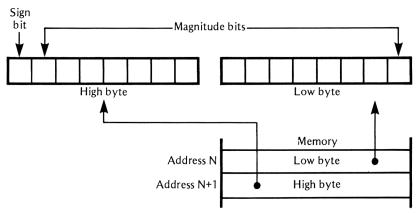

When using double byte numbers, the least significant half is known as the *low-byte* and the most significant half, the *high-byte*. Note that each bit in the high byte has a value 256 times that of the equivalent bit in the low byte. This morsel of knowledge is of far reaching importance and justifies the appearance of Figure 3.3.

If the two bytes together are considered as one number the decimal value of the total is given by:

Total=(low byte value)+(256 $\times$ high byte value)

Fig 3.3 Equivalent bit values

If the low-byte holds 0000 0100 (4 decimal) and the high-byte holds 0010 0100 (36 decimal). The total becomes  $4+(256\times36)=9,220$  decimal.

# Signed numbers

A computer would be of little use if it could only handle positive numbers. Arithmetic used by humans uses the unary minus character '-' to indicate that the number is negative. This is not possible in binary because, as we have seen, the only characters recognised are 1 and 0. The Z80A microprocessor, in common with most other types, employs a system known as two's complement notation for dealing with signed numbers and, as an indirect consequence, subtraction. Before delving into the details of two's complement, it is worth devoting some space to the hardware mechanism of subtraction employed by most microprocessors. The only true arithmetic operation built into the Z80A microprocessor is addition. It can, of course, perform subtraction but, were we to examine the inernal hardware, we would discover that it still uses the additioin process but in a roundabout way by adding the two's complement of the number to be subtracted. This is because every square micrometre on the silicon chip area is precious. In fact the old Silicon Valley boffins used to refer to the area as 'real estate'. They decided that to include a hardware subtraction circuit in a microprocessor, as well as an addition circuit, would be a waste of chip area which could otherwise be used for more rewarding functions.

# Two's complement numbers

The fundamental difference between normal binary (which we shall refer to as unsigned binary) and two's complement is the role of bit 7, the msb. This bit no longer represents magnitude. Instead, it is used to indicate the sign of the number and, indeed, is often referred to as the *sign bit*. The sign bit is 1 for negative numbers and 0 for positive numbers. Although quite straightforward for positive numbers, there is a rather strange twist involved when the number is negative. Before giving the rules, consider the following examples of what positive and negative numbers would look like in two's complement notation:

```

0000 \ 0010 = +2

1111 \ 1110 = -2

```

As you can see, +2 is easy but -2 looks a horrible mess. You may ask why, since the msb is the sign bit, why not write -2 as 1000 0010? This would certainly appear more logical (and certainly easier) but there would be a snag when writing zero. For example, +zero would be written as 0000 0000 and -zero as 1000 0000. In other words, we would have two different ways of writing the same number. In any case, mathematicians have decreed that zero must always be positive so you see the simple way doesn't work.

# The rule for two's complement numbers

First we must introduce the jargon term 'flip'. To *flip* a bit means to change it from 1 to 0 or from 0 to 1. Either of two rules can be used but the following is the accepted academic version:

To obtain the equivalent negative, flip all the bits and add 1.

If, as the result of adding the extra 1, a carry propagates through to the end and 'drops out' then simply ignore it. Some examples based on the rule now follow.

| 1 To find $-2$ , first write | down the binary for +2 which is, 0000 0010=+2 |

|------------------------------|-----------------------------------------------|

| flip the bits                | 1111 1101                                     |

| add 1                        | 1111 1110=-2                                  |

| 2 To find $-8$ ,             | 0000 1000=+8                                  |

| flip the bits                | 1111 0111                                     |

| add 1                        | 1111 1000=-8                                  |

| 3 To find $-1$ ,             | $0000 \ 0001 = -1$                            |

| flip the bits                | 1111 1110                                     |

| add 1                        | 1111 1111=-1                                  |

We have said that this rule is the academic version. Flipping the bits produces the *one's complement* (also called the 'logical' complement)

and adding the extra 1 converts it to the two's complement. However, this rule may have the blessing of the establishment but adding that extra 1 is a nuisance because of keeping track of the carry. There is another way of finding the equivalent negative which does not involve messing around with that awful carry:

Starting from the right, copy down up to and including the first 1 then flip the remaining bits.

#### Examples:

- +2 = 0000 0010

- -2=1111 1110

- +8=0000 1000

- -8 = 1111 1000

- +17=0001 0001

- -17 = 1110 1111

- +1=0000 0001

- -1=1111111111

Two's complement numbers work both ways. That is to say, the rules remain valid for finding the equivalent positive, given the negative version. For example, if we start with 1111 1111 (which is -1) and use the rule, we obtain 0000 0001 (which is +1 again). Thus the two's complement of a number doesn't necessarily mean the negative version. It simply means the same number with opposite sign.

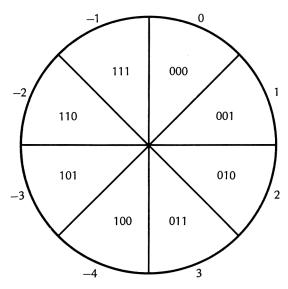

Fig 3.4 The two's complement circle

### The circle of signed numbers

Although two's complement notation seems weird and even illogical, it is, in fact, based on sound number theory. To appreciate this, have a look at Figure 3.4 which, for simplicity, examines all the eight ways of arranging 3 bits. Note the following points:

- (a) The binary combinations proceed smoothly from 000 to 111 as we journey clockwise round the circle. Thus, if we choose to treat the meaning in terms of unsigned binary, the combinations progress from 0 to 7.

- (b) If we treat the meaning in terms of two's complement, we progress clockwise for positive numbers up to +3 or anticlockwise for negative numbers up to -4.

- (c) There are 4 positive numbers, 0, 1, 2, 3 and four negative numbers -1, -2, -3, -4.

Because zero is a positive number, it follows that there will always be room for one larger negative number than positive in two's complement notation. For example, the largest positive number in a byte is  $0111\ 1111=+127$  but the largest negative number is  $1000\ 0000=-128$ . To allay possible criticism, we should point out that mathematically, a number like -128 is considered to be 'smaller' than -127 but playing lip service to the demands of academic purity often hampers initial understanding.

# Two's complement and double byte numbers

When dealing with double byte numbers, bit 7 in the low byte has no significance other than representing part of the overall magnitude. Only bit 7 of the high byte is the true sign bit. For example, consider the following double byte number, 0001 0000 1000 0000. The low byte has a 1 in bit 7 position but it does not represent sign because the number, taken in its entirety, is positive because bit 7 in the high byte is a 0. The largest double byte positive number, treated in two's complement form, is 0111 1111 1111 1111 +32,767 and the largest negative double byte number is 1000 0000 0000 0000 = -32,768. On the other hand, if we treat the numbers as unsigned binary, the largest two byte number becomes 1111 1111 1111 1111 1111 e65,535. Perhaps this would be a good point at which to introduce a few equations for finding the maximum numbers that can be held in a string of N bits.

Largest positive two's complement number= $2^{(N-1)}-1$ Largest negative two's complement number= $-2^{(N-1)}$ Largest positive unsigned binary number= $2^N-1$

# Unsigned binary or two's complement?

Readers may be a little confused at this point as to whether the microprocessor works in two's complement or unsigned binary. The

answer is simple. It depends entirely on your own intepretation of the result. If, for example, you are writing a program which is dealing with numbers that must always be positive (such as vibration frequency or population) then you would interpret the result as unsigned binary. On the other hand, programs concerned with banking accounts, must allow for both credit and debit situations and both positive and negative numbers. In which case numbers would be interpreted in two's complement form. As far as the microprocessor is concerned, arithmetic operations are carried out exactly the same, irrespective of the human interpretation placed on the results. To see why this is so, consider how the processor would add 1 to 0111 1111:

| Add   | 0111<br>0000 |      |

|-------|--------------|------|

| Total | 1000         | 0000 |

Now, as far as the microprocessor is concerned, the job is complete. However, if the programmer is working in pure binary, the result is valid and equal to 128 decimal. If, on the other hand, the operation is dealing with both negative and positive numbers, the result is invalid because the result is a negative number. In other words, two's complement *overflow* has occurred. Fortunately, the microprocessor will set a flag bit in a special register to warn the programmer of this condition. Dependant on the interpretation, the necessary steps can be taken in the program to either deal with an overflow or ignore the flag bit altogether.

# Decimal and binary conversion

Although computers are quite happy with binary, humans are not. Most of us find a page full of '1s' and '0's monotonous and virtually unintelligible. Unless every bit is studied with great care, mistakes will be all too frequent. For example, try and spot (quickly) which bit is different in the following versions:

| Version A | 1001 0010 |  |

|-----------|-----------|--|

|           | 1101 0101 |  |

|           | 1110 1101 |  |

|           |           |  |

|           | 1101 1010 |  |

| Version B | 1001 0010 |  |

|           | 1101 0101 |  |

|           | 1110 1001 |  |

|           | 1101 1010 |  |

|           |           |  |

Fortunately, it is no great problem for software specialists to write binary to decimal conversion routines so that numbers can be entered

in normal decimal form. Indeed, when writing programs in high level languages such as BASIC or PASCAL, it may not even be necessary to understand binary since all entries and transactions take place via decimal numbers. It would seem that similar routines for shielding us from the boredom of binary could be employed in machine code programs. Indeed, most machine code assemblers allow decimal entries. But there is a snag because, even with an assembler, it is often necessary to be aware of the binary bit pattern corresponding to a decimal entry. Unfortunately, decimal and binary are far apart in the number stakes and it is by no means easy to visualise the binary pattern corresponding to the decimal equivalent or vice versa. That is to say, few people could take a quick glance at the pattern 0110 0111 and recognise the decimal equivalent. The problem is even worse for double byte patterns. What is needed is a numbering system which is a compromise between decimal and binary. A system which will enable a human to recognise almost instantly the associated binary pattern. One numbering system, popular in the earlier computers, was octal but this was eventually superseded by the now popular hexadecimal system.

#### Hexadecimal

The *base* of a numbering system is the number of *different characters* used. Binary only uses the character 0 and 1 so the base is 2. Decimal uses the characters 0, 1, 2 . . . 9 so the base is 10. The hexadecimal numbering system (known simply as hex) has a base of 16 because it uses the characters 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F. Notice that decimal and hex are the same for numbers up to 9 but the remaining six characters are the letters A to F inclusive. The table overleaf shows the relationship between the three numbering systems.

#### Machine addresses

When working in BASIC, we seldom need to concern ourselves with actual machine addresses, except of course when we use POKE or PEEK. In machine code, actual machine addresses are constantly in use and, here again, we shall find that hex is far better than decimal for specifying addresses. The Amstrad machine addresses, expressed in decimal, would be address 0 to address 65,535. Expressed in hex, the address range is from 0000 to FFFF which is tidier in appearance. Besides, it is easier to break down the address range into 'pages' each of 256 bytes. The two left hand digits can then represent the page and the two right hand digits can represent the address on that page. For example, the hex address A324 can be visualised as address 24 on page A3.

| Binary | Нех | Decimal |

|--------|-----|---------|

| 0000   | 0   | 0       |

| 0001   | 1   | 1       |

| 0010   | 2   | 2       |

| 0011   | 3   | 3       |

| 0100   | 4   | 4       |

| 0101   | 5   | 5       |

| 0110   | 6   | 6       |

| 0111   | 7   | 7       |

| 1000   | 8   | 8       |

| 1001   | 9   | 9       |

| 1010   | A   | 10      |

| 1011   | В   | 11      |

| 1100   | C   | 12      |

| 1101   | D   | 13      |

| 1110   | E   | 14      |

| 1111   | F   | 15      |

Note that one hex digit can represent any 4-bit pattern whereas two decimal digits are required for the patterns 1010 to 1111 inclusive. This means we can express the contents of a byte with only two hex digits or a double byte with only four. It should not take too much practice on your part before you are able to convert binary to hex almost at sight and with no hesitation. Here are some examples:

| Binary | 1001 | 0001 | 1111 | 1111 | 0111 | 1010 |

|--------|------|------|------|------|------|------|

| Hex    | 9    | 1    | F    | F    | 7    | Α    |

As a final impressive example, consider the pattern, 0111 0000 1111 1010. You should soon be able to convert this at sight to 70FA hex. How long would it take you to convert it to decimal? The Z80 instruction codes are far better written in hex than in decimal. In fact most assemblers, including the one we shall be using, will display them in hex code so this is another reason why we should make some effort to master hex.

# Converting hex to decimal

Although anyone intending to take up machine code seriously should learn to think in hex, there are times when it is necessary to convert from hex back to decimal. You will find this a bit awkward at first because the place weightings of hex digits go up in powers of 16 instead of in powers of 10. Instead of progressing in units of 1, 10, 100, 1000 etc, hex progresses in units of 1, 16, 256, 4096 etc. (Note that 256 is 16 squared and 4096 is 16 cubed). Fortunately, we seldom

have to deal with hex numbers of more than four digits. Here are some examples of hex to decimal conversion:

```

3F hex=(3\times16)+15=63 decimal

A2 hex=(10\times16)+2=162 decimal

FF hex=(15\times16)+15=255 decimal

101 hex=(1\times256)+1=257 decimal

100A hex=(1\times4096)+10=4106 decimal

2ACB hex=(2\times4096)+(10\times256)+(12\times16)+11=10955 decimal

FFFF=(15\times4096)+(15\times256)+(15\times16)+15=65,535.

```

You can of course use the Amstrad in direct mode for hex to decimal conversion.

# Adding two hex numbers

We don't often want to perform actual arithmetic using hex numbers but it is well to underlying mechanism. Just remember that if the sum of any column exceeds F, a carry is passed onto the next column. Here are some examples:

|     | 0F<br>01 | FF<br>01 | 3E<br>56 | F0FA<br>0006 |

|-----|----------|----------|----------|--------------|

| Sum | 10       | 100      | 94       | F100         |

|     |          |          |          |              |

# Largest hex numbers

We listed earlier the numerical limits of bit strings expressed in decimal.

It is useful to also know these limits in hex. In the case of unsigned binary, the largest hex number is FF for single byte and FFFF for double byte.

In the case of two's complement, the largest single byte positive number is 7F (+127 decimal) and the largest negative is 80 (-128 decimal). For double byte two's complement numbers, the limits are 7FFF (+32767 decimal) and 8000 (-32768 decimal).

# Binary coded decimal

There is another numbering system in use, known as binary coded decimal or simply, BCD. It is a system designed to bridge the gap between binary and decimal but, unlike hex, it does not use all of the possible binary patterns in a byte. Here is a table of binary to BCD conversions:

| Binary                                                                       | BCD                                                            |

|------------------------------------------------------------------------------|----------------------------------------------------------------|

| 0000<br>0001<br>0010<br>0011<br>0100<br>0101<br>0110<br>0111<br>1000<br>1001 | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7<br>8                      |

| 1010<br>1011<br>1100<br>1101<br>1110<br>1111                                 | Illegal<br>Illegal<br>Illegal<br>Illegal<br>Illegal<br>Illegal |

Here are some examples of BCD patterns:

0100 1000=78 decimal. 1001 1001=99 decimal. 0000 0101=5 decimal. 0110 0011=63 decimal.

Note that the two nybbles within a byte must be treated independently of each other and must be read as two four-bit patterns.

# Adding two numbers in BCD format

Certain difficulties arise when we try to add two numbers in BCD format because of the possibility of creating one of the six illegal combinations. Study the following two examples of addition in BCD:

| Add 5 to 23            | 0000 0101<br>0010 0011 | (5)<br>(23) |

|------------------------|------------------------|-------------|

| Sum                    | 0010 1000              | (28)        |

| This is a valid result |                        |             |

| Add 8 to 23            | 0000 1000<br>0010 0011 | (8)<br>(23) |

| Sum                    | 0010 1011              | Illegal     |

The low order nybble of the result has fallen into the illegal band. The solution is, at first sight, rather weird. The addition is performed and, if the low order byte result is illegal, just *add a further six*. Let us add a further six to the previous illegal result:

| Add 6 | 0010 1011<br>0000 0110 | Illegal |  |

|-------|------------------------|---------|--|

|       | 0011 0001              | (31)    |  |

Note that adding the extra six has resulted in a carry from the low nybble to the high nybble. This procedure always works and can be summed up as follows:

- 1 Perform normal binary addition.

- 2 Test the result for illegalities (any nybble greater than 1001).

- 3 If illegal, add six.

The reason why this works is because the extra six cause the result to skip over the six illegal patterns, 1010 to 1111.

#### What use is BCD?

Unless your interests extend to linking external digital instruments to the Amstrad, the answer is, not much! It is becoming almost commonplace nowadays to provide digital instrumentation with sockets which can be interfaced to a computer. These readings are normally given in BCD format and may be designed to link up with a special input/output bus system, pioneered by Hewlett Packard, and now known as the IEE 74 standard. Such a bus is not provided on the Amstrad but no doubt its popularity may encourage manufacturers of add-ons to provide a suitable interface.

# Logical operations

There will be time when it is necessary to alter, or perhaps examine, one or more particular bits within a byte without disturbing the remaining bits. For example, we may need to ensure that bit 4 is a '1' without disturbing the remaining bits. On the other hand, we may wish to ensure that bit 7 is a '0'. We may even wish to change the state of certain bits. Normal arithmetic is not of much use to us in these circumstances. Fortunately, most computers (including the Amstrad) are able to carry out three, so called *logical* operations called AND, OR and XOR. They are used in conjunction with a mask word in which the bit pattern is chosen in accordance with certain rules.

To ensure certain bits within a byte are '0'

Use AND with a mask as follows:

'1's in the mask will leave corresponding bits alone, '0's will ensure the corresponding bits are '0'.

To ensure certain bits within a byte are '1'.

Use OR with a mask as follows:

'0' in the mask will leave corresponding bits alone, '1's will ensure the corresponding bits are '1'.

To ensure certain bits in a byte are changed (flipped)

Use XOR with a mask as follows:

'0's in the mask will leave corresponding bits alone, '1's will ensure they are changed.

### Here are some examples:

- 1 To ensure bit 7 in a byte is 0, AND it with the mask 0111 1111, (7F hex).

- 2 To ensure bit 3 in a byte is 1, OR it with the mask 0000 1000, (08 hex).

- 3 To ensure that bit 5 in a byte is changed, XOR it with the mask 0010 0000, (20 hex).

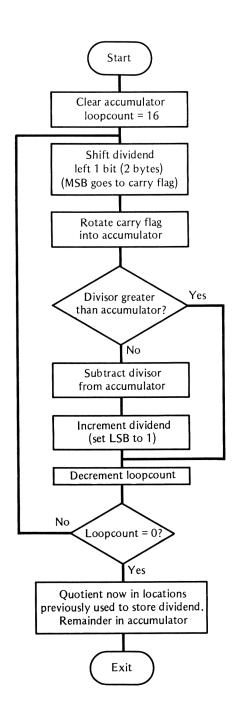

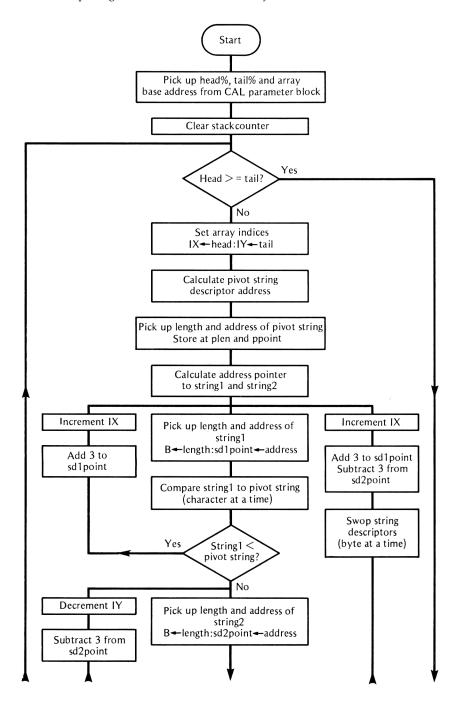

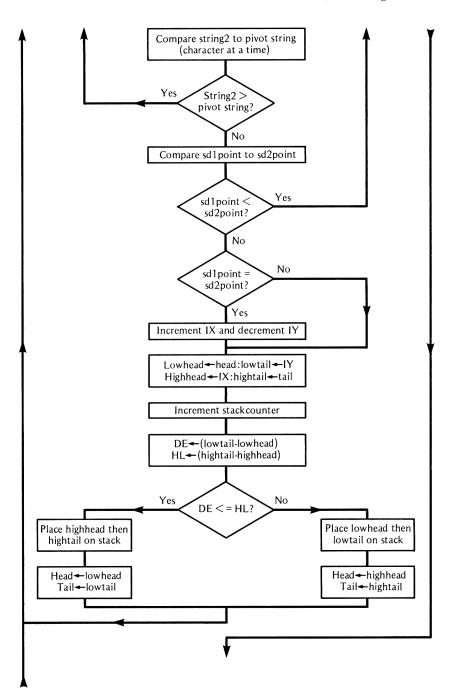

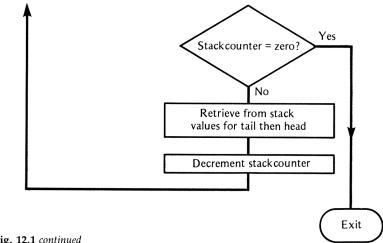

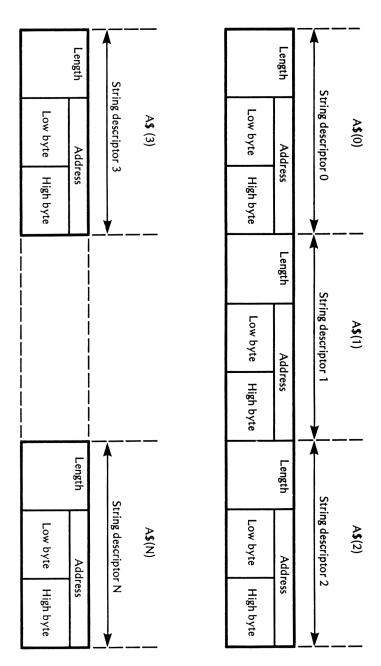

As a final example, if a byte originally contained 1101 1110 and we ANDed it with mask 0111 1111, it would then contain 0101 1110. The three logical operations are purely bitwise in character. That is to say, each bit is treated quite independently of the others. There is no such thing as a carry from one bit to another as happens in arithmetic operations.