B Y T E B O O K S

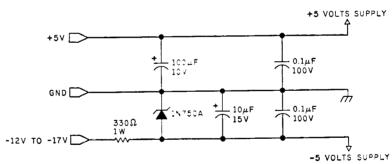

### BUILD YOUR OWN Z80 COMPUTER

by Steve Ciarcia

#### A Note about this book and its free availability online

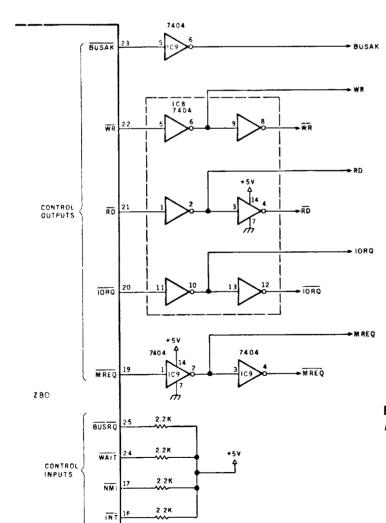

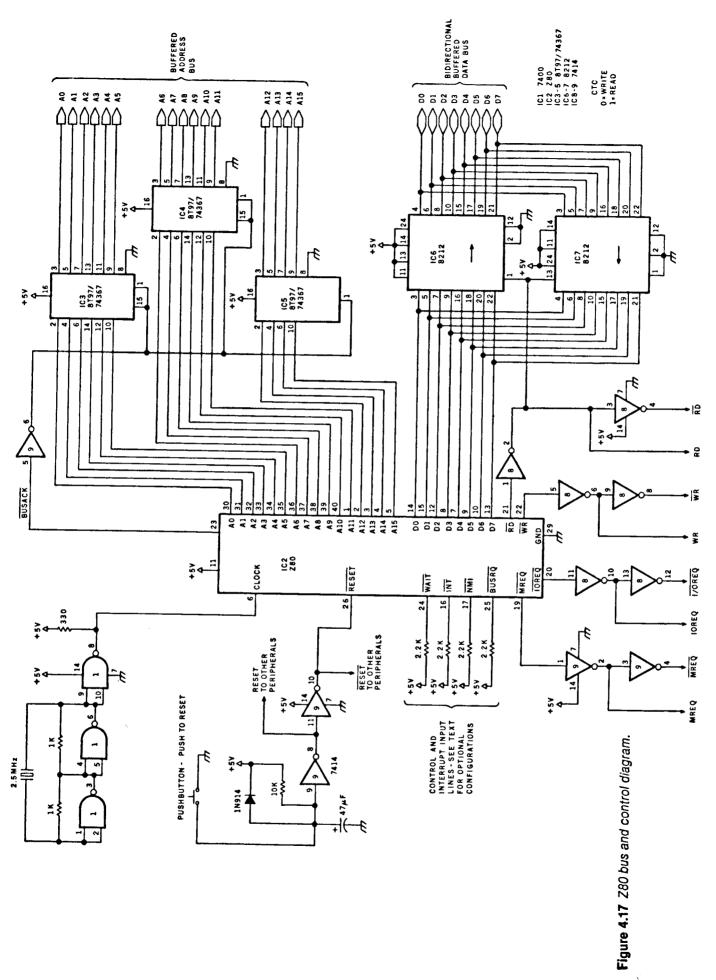

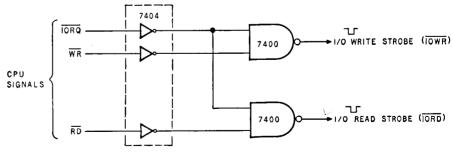

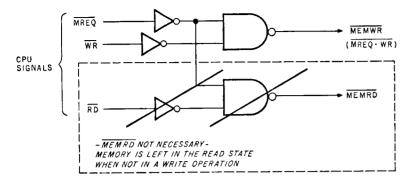

Readers are encouraged to download this book of design guidelines and application notes from Steve Ciarcia, founder and editorial director of Circuit Cellar magazine. Although the original title first appeared in 1981, pre-dating Circuit Cellar "the magazine," I still get a number of purchase requests each year from electronics enthusiasts. Some are just interested in Steve's brand of designing and ability to overcome obstacles, while others still find themselves tweaking projects that use parts described in Steve's projects.

Please note: The original work was only available as a hard copy. Thanks to Andrew Lynch and Bill Bradford for their work in creating the PDF and getting permission from copyright holder Steve Ciarcia to release it. Scanning done by Bill Bradford.

You will be pleased to know that the same style of embedded computing articles can be found each month through Circuit Cellar magazine. Please visit <a href="www.circuitcellar.com">www.circuitcellar.com</a> to learn about this monthly resource for professional designers and electronics enthusiasts alike.

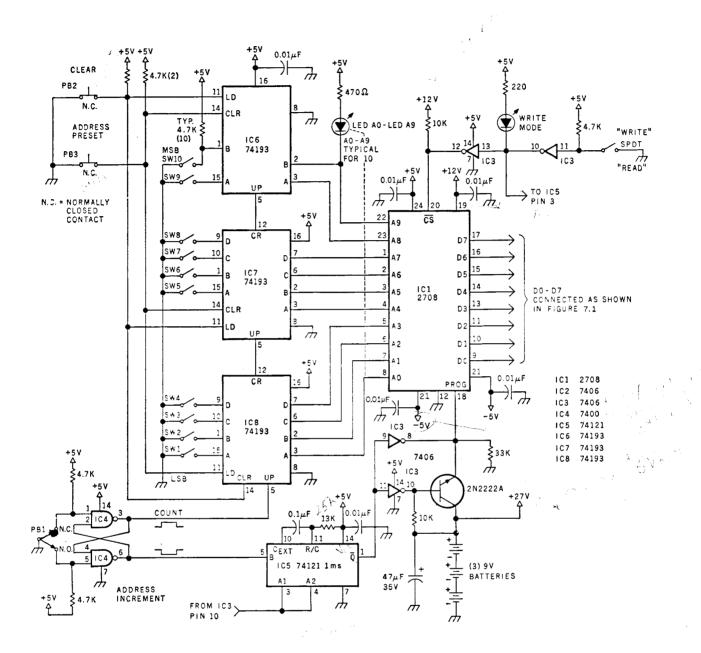

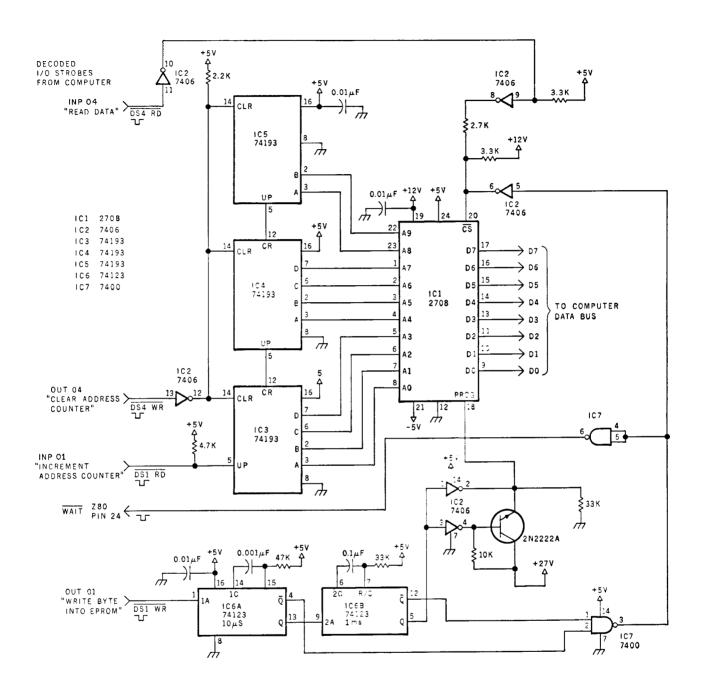

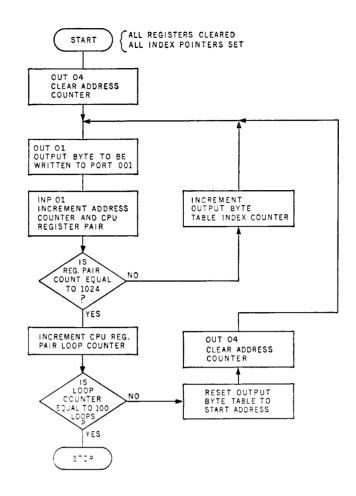

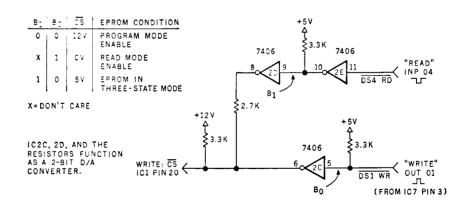

Please enjoy "Build Your Own Z80 Computer" as a great blast from the past. Its style is the foundation on which Circuit Cellar magazine was built and continues to grow. I look forward to seeing you become a part of the ongoing Circuit Cellar success story.

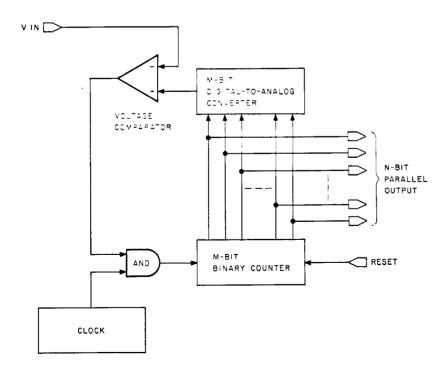

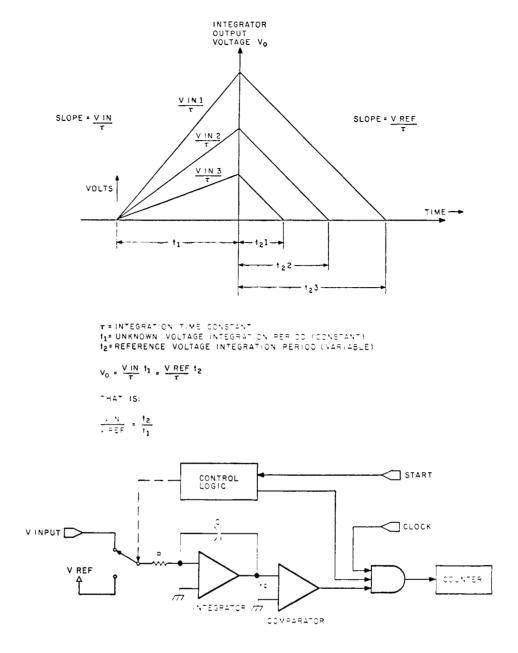

Sincerely,

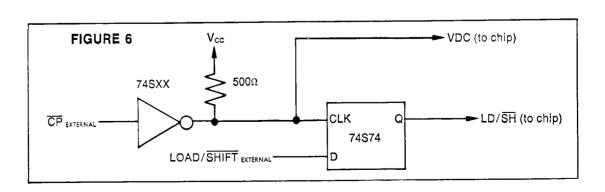

Sean Donnelly, Publisher – Circuit Cellar <a href="mailto:circuitcellar@circuitcellar.com">circuitcellar@circuitcellar.com</a>

## Build Your Own Z80 Computer

Design Guidelines and Application Notes

Steve Ciarcia

#### Build Your Own Z80 Computer

Copyright © 1981 by Steve Ciarcia. All rights reserved. Printed in the United States of America. No part of this book may be reproduced, stored in a retrieval system, or transmitted, in any form, or by any means, electronic, mechanical, photocopying, recording, or otherwise, without the prior written permission of the author.

The author of the circuits and programs provided with this book has carefully reviewed them to ensure their performance in accordance with the specifications described in this book. Neither the author nor BYTE Publications Inc., however, make any warranties concerning the circuits or programs and assume no responsibility or liability of any kind for errors in the circuits or programs, or for the consequences of any such errors. The circuits and programs are the sole property of the author and have been registered with the United States Copyright Office.

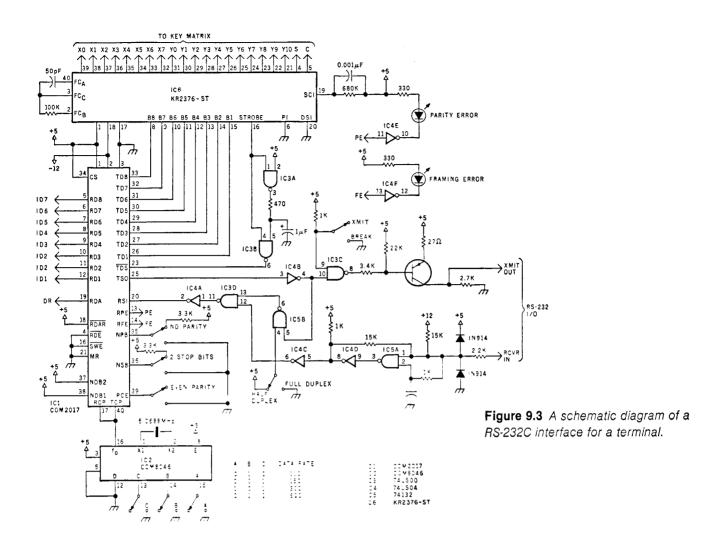

The author would like to acknowledge that portions of this book have been reprinted by permission of the manufacturers. The instruction codes in Chapter 3 and Z80 CPU technical information have been reprinted by permission of Zilog, Inc. Chapter 9 is based on an application note reprinted by permission of SMC Microsystems Corporation.

Library of Congress Cataloging in Publication Data

Ciarcia, Steve.

Build your own Z80 computer.

Includes index.

1. Electronic digital computers--Amateurs' manuals.

2. Zilog Model Z-80 (Computer) I. Title.

TK9969.C52 621.3819'582

ICDNI 0 07 010073 1

81-4335

ISBN 0-07-010962-1

AACR2

Text set in Paladium by BYTE Publications

Edited by Bruce Roberts and Nicholas Bedworth

Design and Production Supervision

by Ellen Klempner

Production by Mike Lonsky

Cover Photo by Charley Freiberg

Copy Edited by Rich Friedman and Peg Clement

Figure and Table Illustrations

by Tech Art Associates

Printed and bound using 45# Bookmark

by Kingsport Press, Kingsport, Tennessee

## Build Your Own Z80 Computer

To my wife Joyce, Steve Sunderland, and Judy and Lloyd Kishinsky

### Introduction

A few years ago, when microprocessors were first introduced, computer enthusiasts and electrical engineers were one and the same. Those of us who lived only to solder kluge after kluge basked in our glory. Now, however, the prices of completely assembled and packaged systems have plummeted. Today anyone with an interest, almost regardless of technical capabilities, can own and operate a computer. Buying a computer is now similar to purchasing a television set and the ranks of computer enthusiasts have swelled accordingly.

With any popular movement, the available literature reflects the concerns of a majority of the followers. And, consistent with the popularization of computer science, the technical emphasis on computer bookshelves has shifted away from hardware design. Other than introductory texts called, say, *How Logic Gates Work*, most computer books either treat microcomputer hardware simplistically or attempt to be "catch-all" cookbooks, sometimes omitting tasty ingredients. Often, the only alternatives are engineering texts and trade journals, tedious reading at best.

For a number of years, I have been writing a column for *BYTE* magazine, and reader response has shown that there still exists a great deal of interest in hardware design and do-it-yourself projects. At the same time, I've been painfully aware of the lack of materials for such people. Most queries come from technical or high school students who have read all the descriptions and studied the block diagrams, but who crave practical answers and system examples. Unfortunately, there are very few books I can suggest.

Build Your Own Z80 Computer is a book written for technically minded individuals who are interested in knowing what is inside a microcomputer. It is for persons who, already possessing a basic understanding of electronics, want to build rather than purchase a computer. It is not an introductory electronics handbook that starts by describing logic gates nor on the other hand is it a text written only for engineering students. While serving to educate the curious, the objective of this book is to present a practical, step-by-step analysis of digital computer architecture, and the construction details of a complete and functional microcomputer.

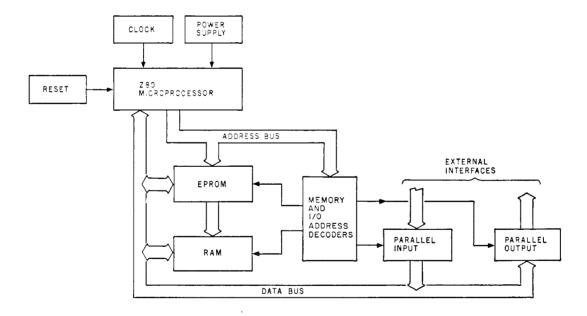

The computer to be constructed is called a Z80 Applications Processor—ZAP computer for short. It is based on the industry standard Zilog Z80 microprocessor chip. This chip was chosen on the basis of its availability and low cost, as were the other components for ZAP. To further help the homebrew enthusiast, and for those experimenters who prefer to start a book at the back, I have listed in Appendix A a company that supplies parts and programmed EPROMs (erasable-programmable read-only memory).

I have structured the book as a logical sequence of construction milestones interspersed by practical discussions on the theory of operation. My purpose is twofold: to help a potential builder gain confidence, and to make the material more palatable through concrete examples.

Though this is basically a construction manual, considerable effort is given to the "why's" and "how's" of computer design. The reader is exposed to various subjects, including: the internal architectures of selected microprocessors, memory mapping, input/output interfacing, power supplies, peripheral communication, and programming. All discussions try to make the reader aware of each individual component's effect on the total system. Even though I have documented the specific details of the ZAP computer, it is my intention (and the premise of the book) that the reader will be able to configure a custom computer. ZAP is an experimental tool that can be expanded to meet a variety of applications.

ZAP is constructed as a series of subsystems that can be checked and exercised independently. The first item to be built is the power supply. This is a good way to test ability and provide immediate positive reinforcement from successful construction. The three-voltage supply is both overvoltage and overtemperature protected and has adequate current for an expanded ZAP system.

Next, the reader learns why the Z80 was chosen for ZAP and the architectural considerations that affect component selection on the other subsystems. A full chapter is devoted to the Z80 chip. Each control signal is explained in detail and each instruction

is carefully documented.

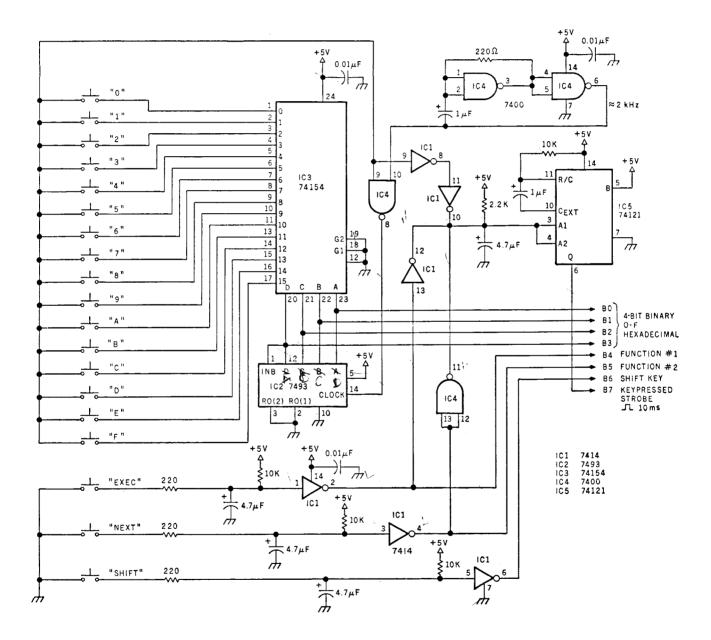

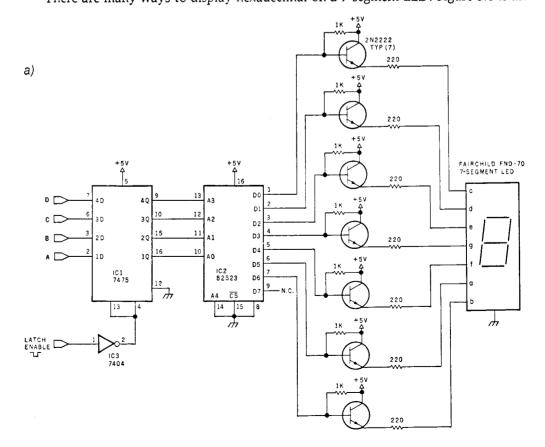

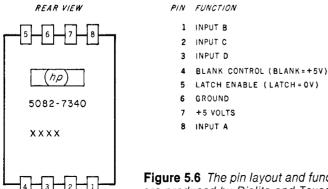

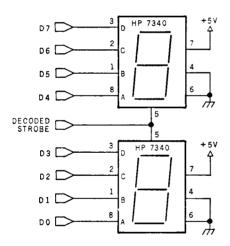

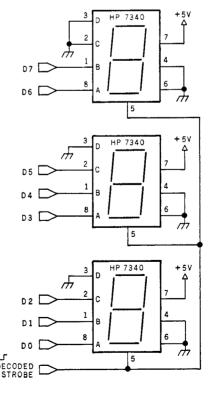

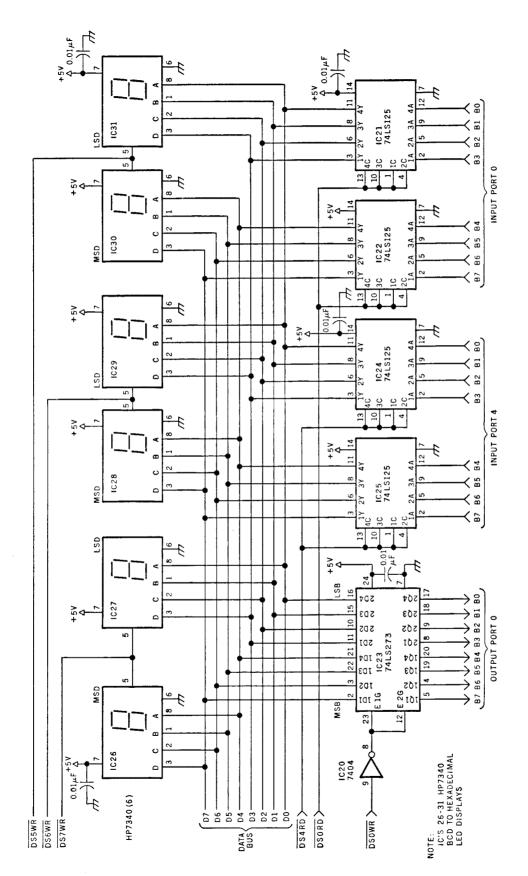

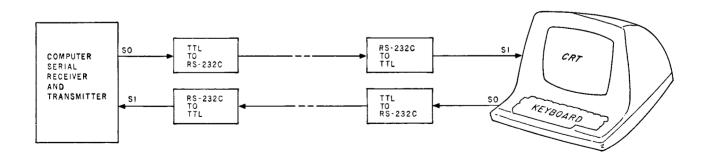

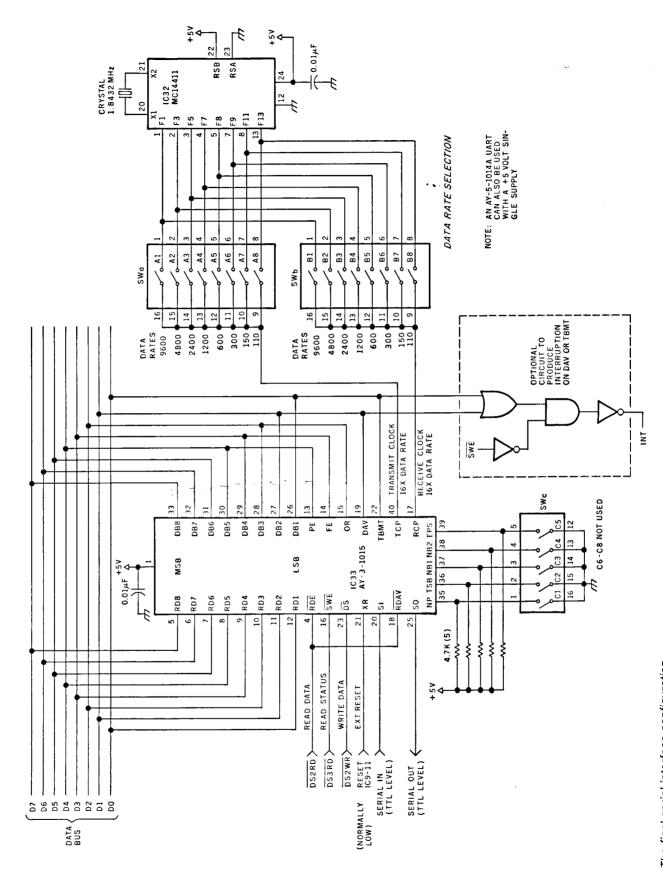

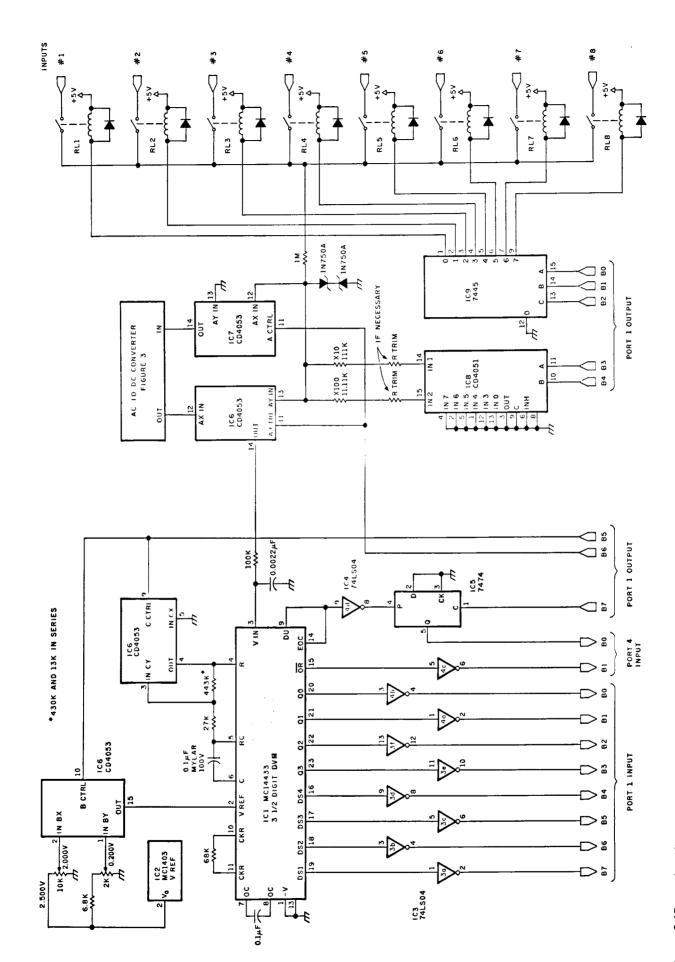

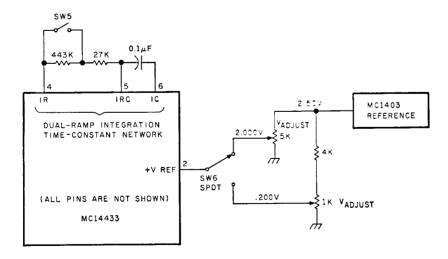

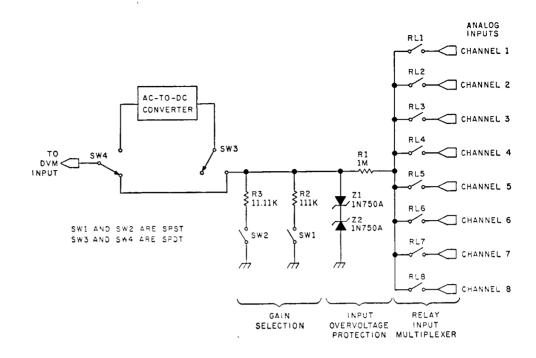

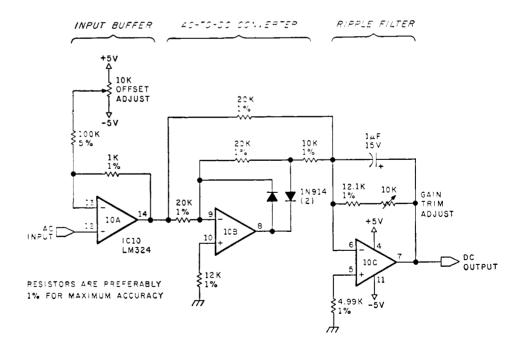

The hardware construction proceeds in stages with intermediate testing in order to ensure success. The basic elements of the computer are assembled first and then checked out. The reader selects which peripherals are to be added. The book contains sections on the construction of a hexadecimal display, keyboard, EPROM programmer, RS-232C serial interface, cassette mass storage system, and fully functional CRT terminal. In addition, a chapter addresses interfacing the ZAP to analog signals. I provide specific circuits that can convert ZAP into a digital speech synthesizer or a data acquisition system and data logger.

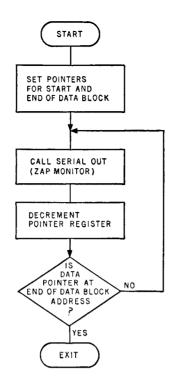

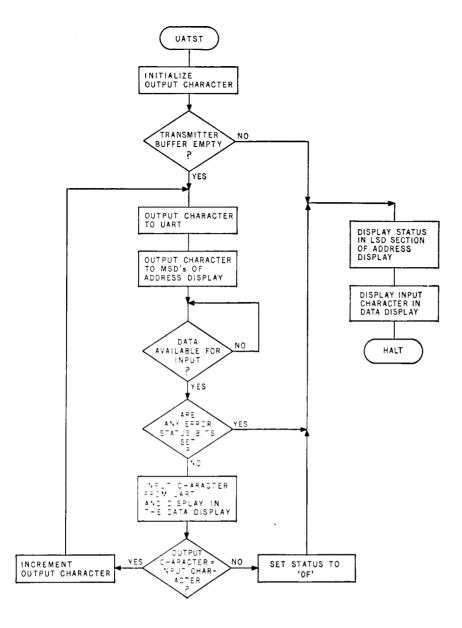

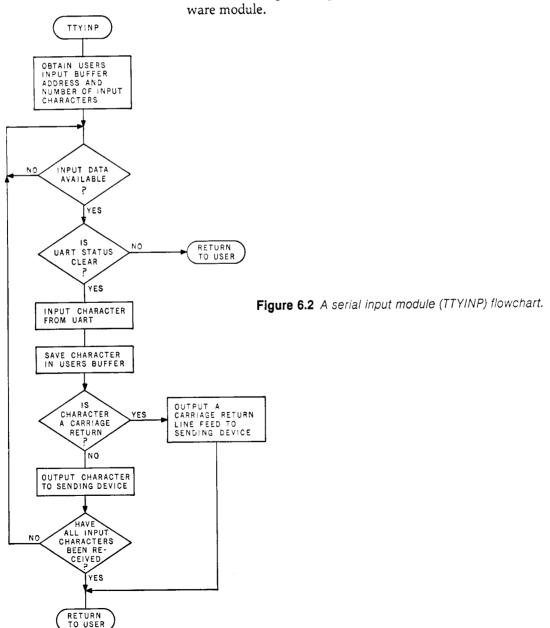

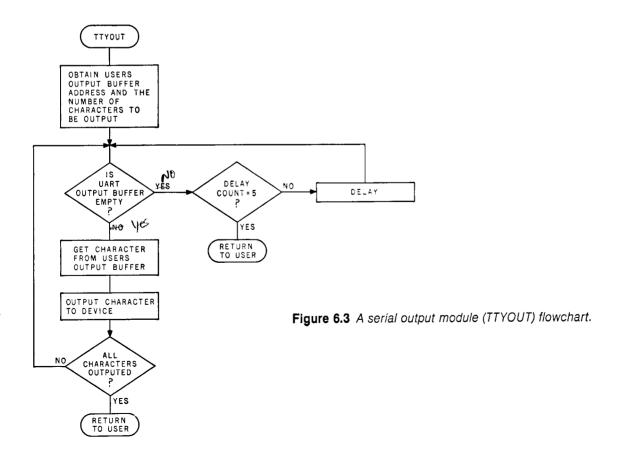

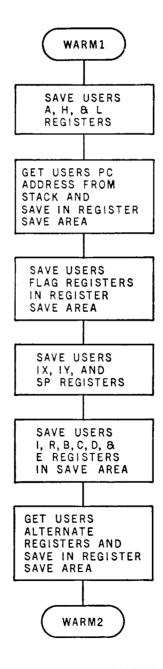

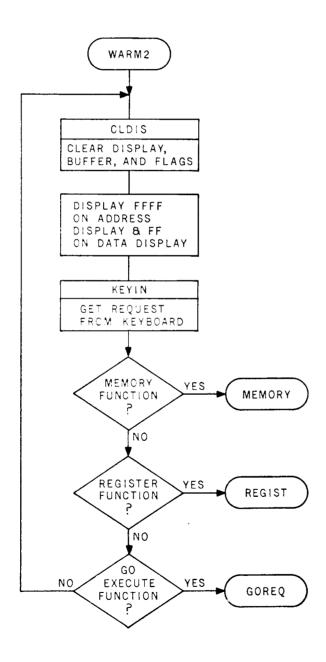

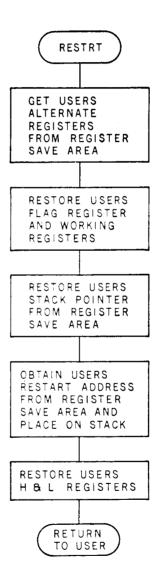

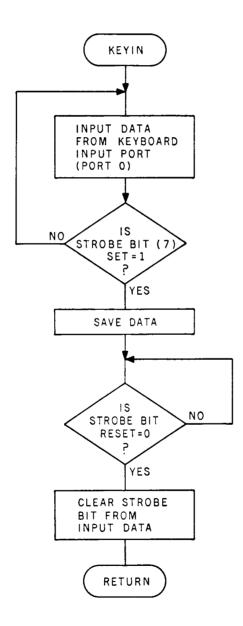

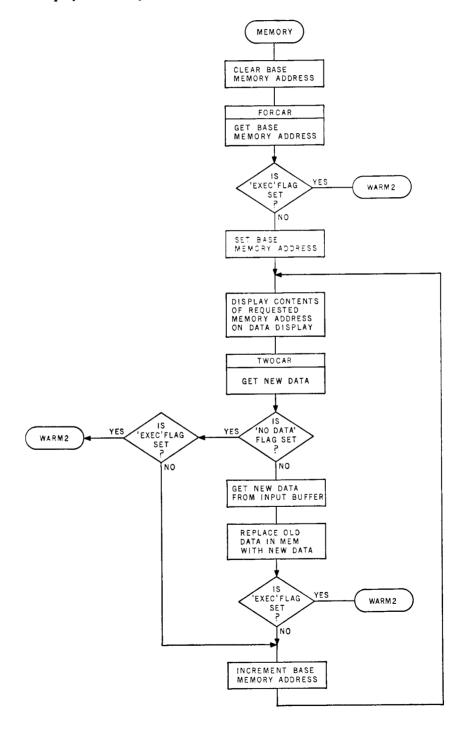

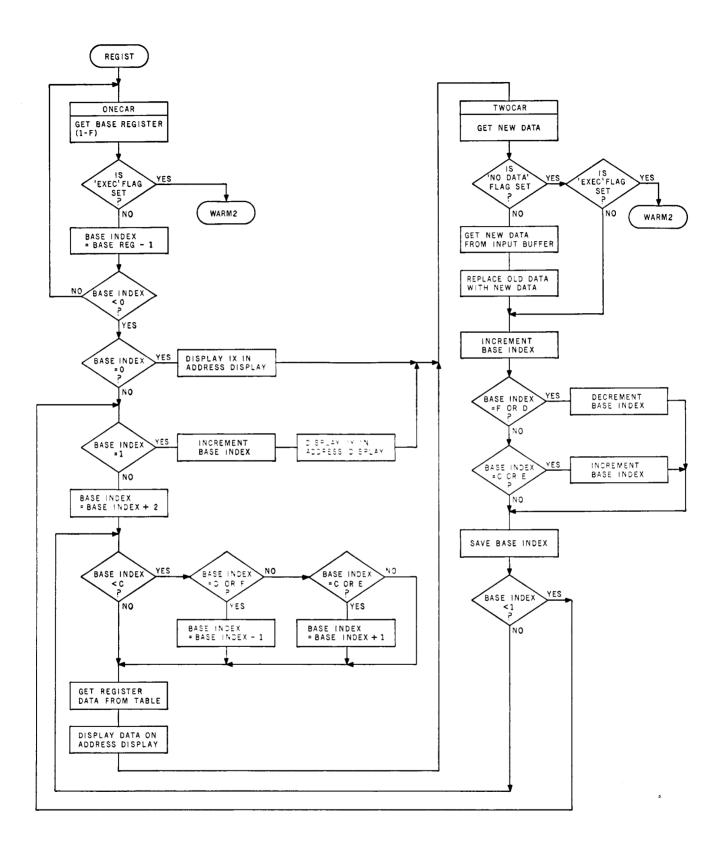

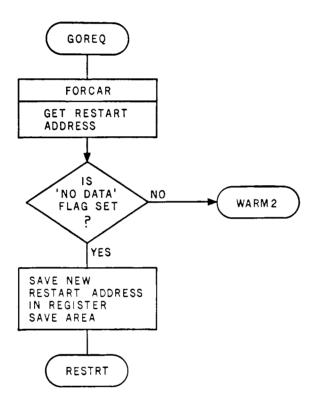

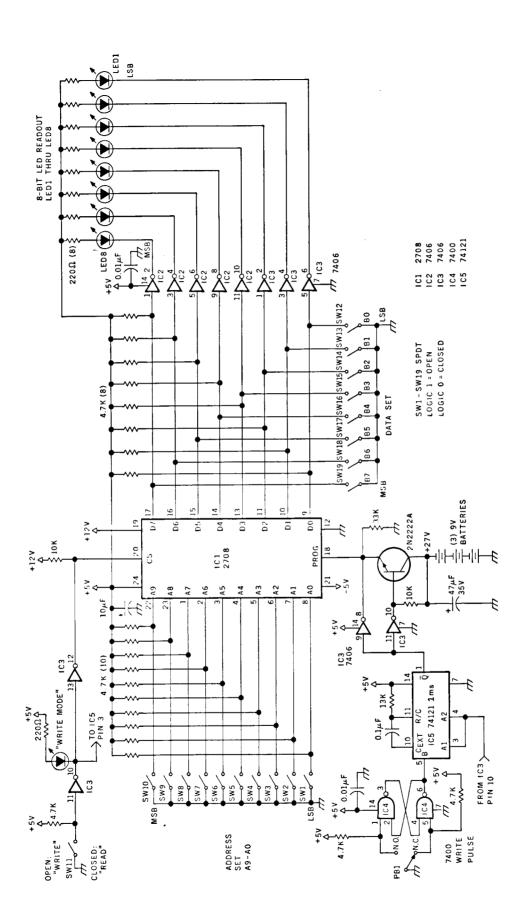

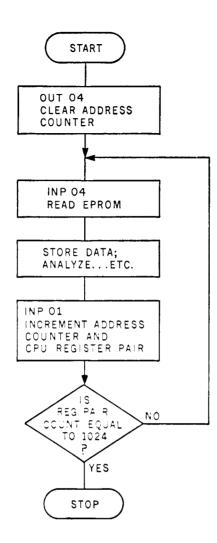

A special 1 K (1024 bytes) software monitor coordinates the activities of the basic computer system and the peripherals. Software is explained through flow diagrams and annotated listings. With this monitor as an integral component, ZAP can function as a computer terminal, a dedicated controller, or a software development system.

Build Your Own Z80 Computer is a book for hardware people. It cuts through the theoretical presentations on microcomputers and presents a real "How-to" analysis suitable for the reader with some electronics experience or for the novice who can call someone for supervision. From the power supply to the central processor, this book is written for people who want to understand what they build.

Steve Ciarcia May 1981

### TABLE OF CONTENTS

| Introduction                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 1                             | Power Supply 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Chapter 2                             | Central Processor Basics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 3                             | The Z80 Microprocessor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Chapter 4                             | Build Your Own Computer - Start With the Basics 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Chapter 5                             | The Basic Peripherals 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Chapter 6                             | The ZAP MONITOR Software 151                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Chapter 7                             | Programming an EPROM 173                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Chapter 8                             | Connecting ZAP to the Real World                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

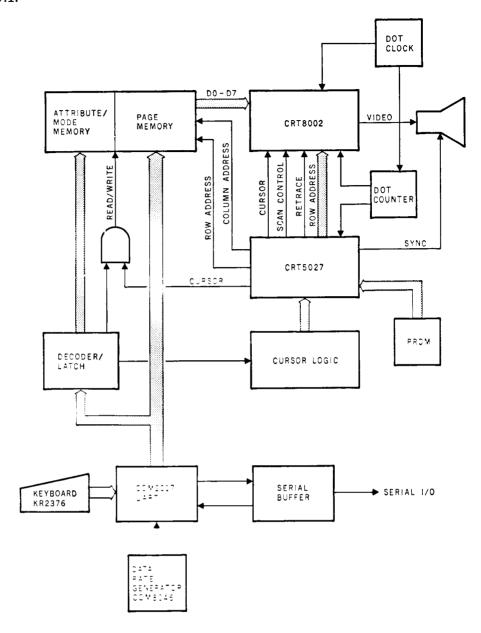

| Chapter 9                             | Build a CRT Terminal 213                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Appendix A                            | Construction Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Appendix B                            | ASCII Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

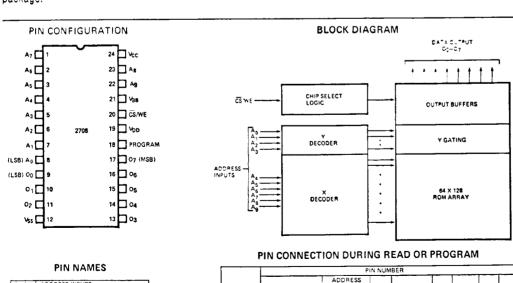

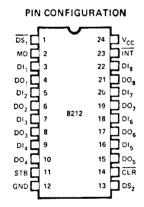

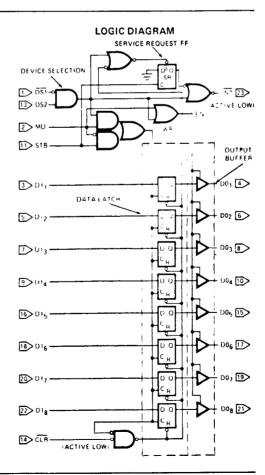

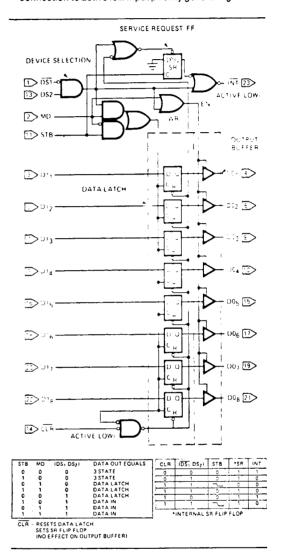

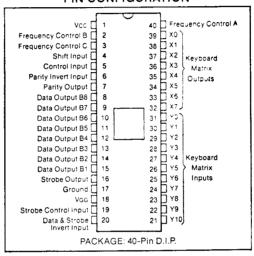

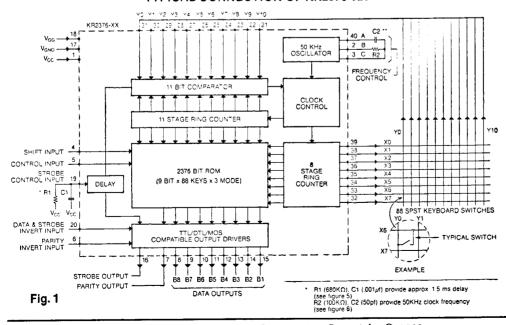

| Appendix C                            | Manufacturers' Specification Sheets       233         C1       2708 8K (1K × 8) UV Erasable PROM       235         C2       2716 16K (2K × 8) UV Erasable PROM       239         C3       2102A 1K × 1 Bit Static RAM       243         C4       2114A 1K × 4 Bit Static RAM       247         C5       8212 8-Bit Input/Output Port       251         C6       KR2376-XX Keyboard Encoder Read-Only Memory       259         C7       COM2017 Universal Asynchronous Receiver Transmitter       263         C8       CRT 5027 CRT Video Timer and Controller       271         C9       CRT 8002 Video Display Attributes Controller       279         C10       COM8046 Baud Rate Generator       287 |

| Appendix D                            | ZAP Operating System 293                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| • • • • • • • • • • • • • • • • • • • | Z80 CPU Technical Specifications307E1 Electrical Specifications309E2 CPU Timing313E3 Instruction Set Summary321                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Glossary                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Index                                 | 329                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## CHAPTER 1 POWER SUPPLY

It's not enough to build a central processor card with a little input/output (I/O) and memory, and call it a computer. From the time you walk over to the computer and flip the switch, the system is completely dependent upon the proper operation of its power supply. A book concerned with building a computer system from scratch would be completely inadequate without a description of how to construct an appropriate power supply.

Much has been written on the subject of direct current (DC) power supplies. There are DC to DC and AC (alternating current) to DC converters, switching and shunt regulators, constant voltage transformers, and so on. It's not my intention to make a power supply expert out of everyone. Instead, I will outline the design of the specific DC power supply which we will use to power the Z80 Applications Processor (ZAP).

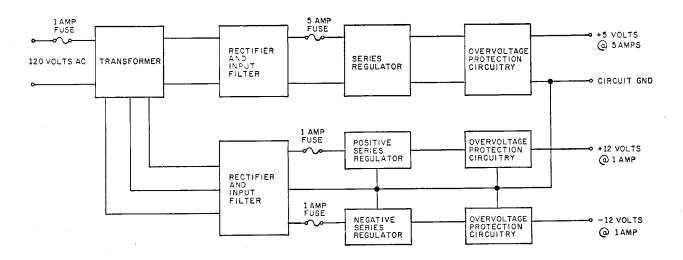

In large computers, the DC supplies convert enormous amounts of power to run thousands of logic chips; by necessity, manufacturers choose the most efficient methods of power conversion. These state of the art methods would be expensive and difficult for the hobbyist to build in prototype form. Fortunately, the power demands for ZAP are much less than those of the large computers; we can take advantage of established design methods while incorporating the latest advances in regulator technology. Figure 1.1 is a block diagram of the power supply for ZAP.

Each of the three DC supplies necessary to power ZAP consists of three basic modules: a transformer section to reduce the 120 VAC line voltage to the lower voltage used by the computer; an input rectifier/filter to convert AC to low ripple DC; and a regulator which stabilizes the output at a fixed voltage level. Overvoltage protection circuitry will be discussed separately.

Figure 1.1 A block diagram of the basic power supply for the Z80 Applications Processor (ZAP).

The proper specification of the transformer and input filter is often neglected by hobbyists who overlook the consequences of a poorly designed filter. This is caused, in part, by the abundant technical information circulated by semiconductor manufacturers extolling the virtues of their regulator circuits. One can easily conclude from this "publicity gap" that the regulation section of the power supply is the only component worthy of consideration; and in fact, advances in regulator design and the advent of high-power, three-terminal regulators have reduced the need for the analog designer in the application. In the past, 25-odd components and considerable calculations were necessary to produce an adequate voltage regulator. Now, however, the majority of applications can be accommodated with a single, compact device. Even so, an input filter section should not be taken lightly and still requires thorough consideration and a modest amount of computation for each application.

There are three supply voltages necessary to operate ZAP. Each supply incorporates an input filter section. Because the +5 V supply is the most important, it receives the most attention. For the purposes of this discussion, we will divide the supply into two sections: transformer/input filter, and output regulator.

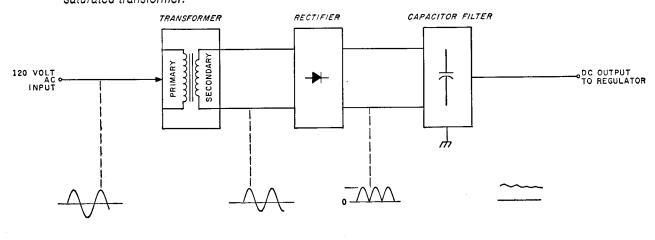

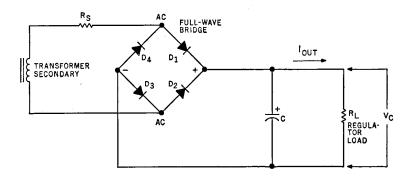

A standard input filter block diagram is shown in figure 1.2. In its simplest form, it consists of three components that function as follows:

- A transformer that isolates the supply from the power line and reduces the 120 VAC input to usable, low-voltage AC.

- A bridge rectifier that converts AC to full-wave DC and satisfies the charging current demands of the filter capacitor.

- A filter capacitor that maintains a sufficient level between charging cycles to satisfy the regulator input voltage limitations.

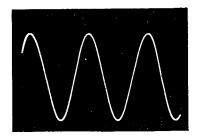

Photo 1.1 120 VAC RMS input/output waveform of a saturated transformer.

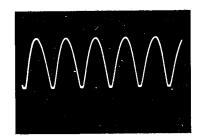

Photo 1.2 Rectifier waveform.

Photo 1.3 Ripple waveform at various loads.

PRIMARY INPUT VOLTAGE SECONDARY OUTPUT VOLTAGE CONTINUOUS CURRENT OUTPUT SECONDARY IMPEDANCE SURGE CURRENT CAPABILITY VOLTAGE DROP CONTINUOUS CURRENT RATING SURGE CURRENT RATING VOLTAGE RATING RIPPLE VOLTAGE

Figure 1.2 A block diagram of a standard input filter.

#### DESIGNING AN INPUT FILTER

You would think that specifying the transformer would be the first consideration when designing a power supply. Yes and no. The approximate output voltage can be determined by rule of thumb, but the exact requirements are deduced only by a thorough analysis that proceeds from the desired output voltage back. In practice, the difference between a reasonable guess and a laborious analysis will be important only to a person capable of manufacturing his own transformer. In most instances, the hobbyist will have to rely upon readily acquired transformers with standard output voltages. For this reason, my approach is predicated on the practical aspects of power supply design rather than on the minute engineering details that have no real bearing on the outcome.

A 120 VAC RMS (root mean square) sine wave is applied to the primary of the transformer. Figure 1.2 illustrates the waveforms anticipated at selected points through the filter section. Photo 1.1 shows that 120 VAC is actually 340 V peak to peak; care should be used in the insulation and mounting of components.

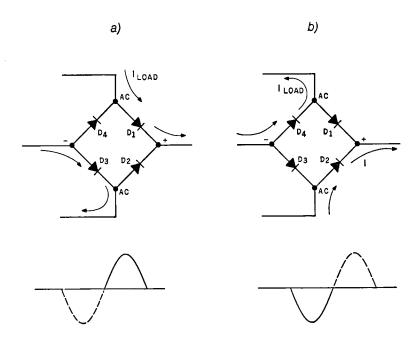

The secondary output of the transformer will be a similar sine wave, reduced in voltage. It is then applied to a full-wave bridge and the waveform will appear as in photo 1.2. You'll notice a slight flat spot between "humps." As a result of dealing with actual electronic components rather than mathematical models, we should be aware of certain peculiarities. Silicon diodes exhibit threshold characteristics and, in fact, have a voltage drop of approximately 1 V across each diode. This voltage drop becomes significant in full-wave bridge designs and, as figures 1.3a, 1.3b, and photo 1.2 illustrate, can accumulate as diodes are added in series. The 2 V loss in the bridge is an important consideration and should be reflected in the calculations.

The voltage regulator requires a certain minimum DC level to maintain a constant output voltage. Should the applied voltage dip below this point, output stability is

Figure 1.3 The direction of the current flow through the full-wave bridge.

- a) During the positive half of the AC cycle, current flow is through  $D_1$  and  $D_3$ ;  $D_2$  and  $D_4$  are not conducting.  $V_{D1} + V_{D3} \approx 2$  volts.

- b) During the negative half of the AC cycle, current flow is through  $D_2$  and  $D_4$ ;  $D_1$  and  $D_3$  are not conducting.  $V_{D2} + V_{D4} \approx 2$  volts.

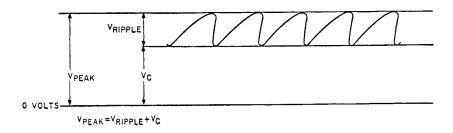

severely degraded. Thus, a filter capacitor is used to smooth out the "humps" in the rectified sine wave. When the diodes are conducting, the capacitor stores enough charge to maintain the minimum voltage required until the next charge cycle. (In practice, we wouldn't want to cut it that close.) The input to the transformer is 60 Hz, but because of the characteristics of full-wave rectification, the charging cycles occur at 120 Hz. The capacitor charges up during one 8.3 ms cycle, and, as the regulator draws power from it to satisfy the load demands, it must continue to provide at least the highest minimum input voltage required by the regulator until the next charge cycle, 8.3 ms later. This periodic charge/discharge phenomenon is shown in photo 1.3. The magnitude of the voltage fluctuation between the two peaks of the cycle is referred to as ripple. The highest magnitude of the waveform including the ripple is designated as peak voltage. Both are important to remember and are shown in figure 1.4.

**Figure 1.4** Output voltage as a combination of a certain steady-state voltage  $(V_c)$  plus a ripple voltage  $(V_{RIPPLE})$ .

Given a basic understanding of the individual components at this stage, we can proceed to the case at hand: a 5 V, 5 A power supply. For reasons we'll discuss later, the 5 V regulator section of this supply will require an absolute minimum of 8.5 V for proper operation. This means that whatever the magnitude of  $V_{PEAK}$  and  $V_{RIPPLE}$ , the final  $V_c$  level must not go below 8.5 V, or the regulator will not work. By giving ourselves some leeway, say  $V_c = 10$  V, we can take a little more poetic license with the calculations and still produce a good design. Going much above 10 V, while still satisfying the input criteria, would increase power dissipation and possibly destroy the regulator. There is an answer to this vicious circle and that's to be conservative. Experience shows that adding a little insurance is worthwhile.

Now that 10 V is the goal, we can appropriately select the other filter components to meet it. Figure 1.5 is the filter circuit of our 5 V supply.  $R_s$  is the resistance of the secondary winding of the transformer. For a 5 to 8 A transformer, it will average about 0.1 ohms. The first values to recognize follow:

$$\begin{array}{l} V_{\it C} = V_{\it regulator\ minimum\ input\ voltage} = 10\ V \\ I_{\it out} = I_{\it regulator\ load} = 5\ A \\ R_{\it S} = R_{\it transformer\ secondary\ resistance} = 0.1\ ohms \end{array}$$

$V_{\it PEAK}$  can be any voltage up to the maximum input for which the regulator is rated. However, this will increase the circuit power dissipation. The rule of thumb I use when designing supplies of this type is that  $V_{\it PEAK}$  should be approximately 25% higher than  $V_{\it C}$ . In this way, the capacitor value will be kept within reasonable limits. The ratio of  $V_{\it C}$  to  $(V_{\it PEAK}-V_{\it C})$  is referred to as the ripple factor of the filter capacitor.

$$Y_F = \frac{V_{FEAK} - V_C}{V_C} = \frac{12.5 - 10}{10} = 25\%$$

A ripple factor of 25% at 5 A will fall well within the acceptable capacitor ripple current ratings and eliminate the need for the hobbyist to dig into manufacturers' specifications of capacitors. This ripple factor is arbitrary, but it is best to keep it as low as possible.

Figure 1.5 The input filter circuit of the 5 V power supply.

#### SIZING THE CAPACITOR

We now know that the capacitor must sustain 10 V from a peak input of 12.5 V.

$$\begin{array}{l} V_{PEAK} = 12.5 \text{ V} \\ V_C = 10 \text{ V} \\ V_{RIPPLE} = 2.5 \text{ V} \end{array} \right\} \quad V_C = V_{PEAK} - V_{RIPPLE}$$

The next consideration is to choose a capacitor that will accomplish this goal. Another rule of thumb calculation that saves considerable labor is

$$C = \frac{dt}{dv} I$$

where

C = capacitor value in farads = ?

I = maximum regulator current = 5 A

dt = charging time of capacitor = 8.3 ms (120 Hz)

dv = allowable ripple voltage = 2.5 V

Plugging in the values of our circuit,

$$C = \frac{(5)(8.3 \times 10^{-3})}{(2.5)} = 16.6 \times 10^{-3}$$

farads

or,

$$C = 16,600 \text{ microfarads } (\mu F)$$

Generally available commercial electrolytic capacitors have a tolerance of +50 and -20%. To be on the safe side and to make it easier to find a standard stock component, a value of 20,000  $\mu$ F is better. The added 3,400  $\mu$ F reduces the ripple by another 0.4 V and gives us a little "insurance." The only other item to consider with the capacitor is operating voltage. Because the design dictates that  $V_{PEAK}$  is 12.5 V, this should be a satisfactory rating. However, experience shows that transformers end up running at higher output voltages than labeled and that 12.5 V at 115 VAC hits 13.6 V when the line voltage goes up to 125 VAC. A capacitor voltage of 15 VDC would appear to satisfy the requirement, but I recommend using the next increased standard value of 20 VDC.

The capacitor is therefore 20,000  $\mu$ F at 20 VDC. The rectifier can be a monolithic full-wave bridge, or it can be four discrete diodes. Note that because a bridge is usually encapsulated, the four terminals are labeled instead of showing the polarity markings of the individual diodes. The designations for the four terminals are two AC input terminals, and a + and - output terminal.

#### THE RECTIFIER

There are three considerations when choosing a rectifier: surge current rating, continuous current, and PIV (peak inverse voltage) rating. These choices are not inconsequential and must be considered carefully.

When a power supply is first turned on, the capacitor is totally discharged. In fact, it will instantaneously appear to be a 0 ohm impedance to the voltage source. The only aspect of the circuit that limits the initial current flow is the resistance of the secondary transformer windings and the connecting wiring; designers often add a series resistance to limit surge current.

The surge current in this circuit is

$$I_{SURGE} = \frac{V_{PEAK}}{R_S} = \frac{12.5}{0.1} = 125 \text{ A}$$

and the time constant of the capacitor is

$$\tau \cong R_s \times C \cong (0.1)(20 \times 10^{-3}) = 2 \text{ ms}$$

As a rule of thumb, the surge current will cause no damage to the diode if  $I_{SURGE}$  is less than the surge current rating of the diode and if

$$\tau$$

< 8.3 ms (which it is)

We can't check surge rating until after we choose a diode bridge, but the other two parameters can be defined.

The bridge can be either of the following:

Motorola MDA 980-2:

$$I_{CONT} = 12$$

A,  $I_{SURGE} = 300$  A, PIV = 100 V Motorola MDA 990-2:  $I_{CONT} = 27$  A,  $I_{SURGE} = 300$  A, PIV = 100 V

Both of the above bridges have a surge current rating of 300 A, so our surge requirement is also satisfied.

#### PIV

PIV (peak inverse voltage) is the maximum voltage that may appear across the diode before it self-destructs. Diodes, unlike capacitors, are unforgiving; transients will wipe them out. It is not unusual to have 400 V transients on the 115 VAC input line. This causes our 12.5 V to shoot up momentarily to 43 V! The bridge rectifier should therefore have a minimum PIV rating of 50 V. For a few pennies more, you can get a bridge rated for 100 PIV. Remember, insurance costs less than computers.

#### **CONTINUOUS CURRENT**

The last consideration is continuous current rating. Whereas the regulator may be designed for a 5 A output, the particular regulator I have chosen will draw 7 A if shorted. This is not standard operating procedure, but it can happen. The suggested standard component would be a 12 A, 50 PIV bridge. A preferred component would be one rated for 12 A at 100 PIV or, for an additional 15% cost premium, a 27 A at 100 PIV. This last design choice is strictly brute force, but it saves the diode bridge should the capacitor ever short-out accidentally. A 6 A transformer might put out more than 12 A in a short-circuit mode, but it's unlikely that it would be capable of 27 A. Either choice will satisfy the design, but only one saves the design from the builder.

#### THE TRANSFORMER

Now let's consider the transformer. We have determined the voltage drops across the various components. The values are used to calculate the required RMS (root mean

square) secondary voltage in the following way:

$$V_{SEC(RMS)} = \frac{V_C + V_{RIPPLE} + V_{RECT}}{\sqrt{2}}$$

$$= \frac{10 + 2.5 + 2.0}{1.414}$$

$$= 10.25 \text{ V}$$

$$V_{RECT} = \text{Voltage drop across each diode} - \text{(approximately 1 V per diode)}$$

In practice, a 10 V, 6 A standard value transformer will be close enough.

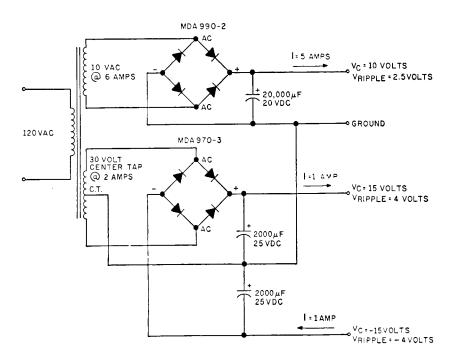

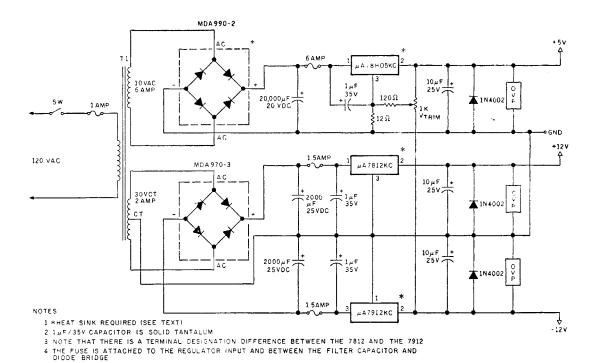

The components of the + and -12 V supplies are chosen in a similar manner, with the exception that required current is only 1 A, and a 200 PIV bridge is recommended because of the particular rectifier configuration. The finished schematic of the transformer and filter section of our computer is illustrated in figure 1.6.

Figure 1.6 A schematic diagram of a transformer and input filter section.

#### **VOLTAGE REGULATORS**

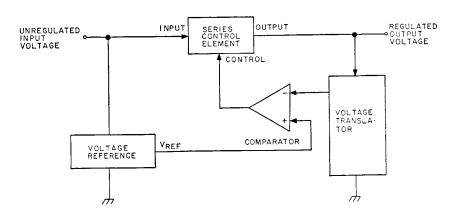

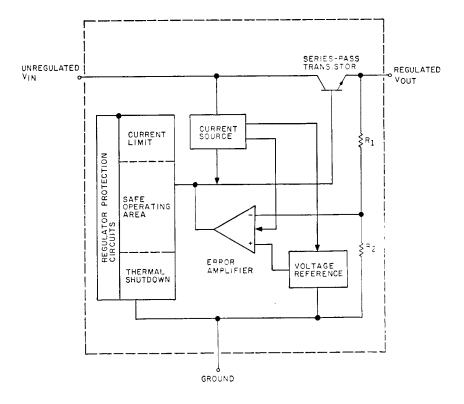

The voltage regulator section of our power supply is the next consideration. All voltage regulators perform the same task: they convert a given DC input voltage into a specific, stable DC output voltage and maintain this setpoint over wide variations of input voltage and output load. The typical voltage regulator, as shown in figure 1.7, consists of the following:

- a reference element that provides a known stable reference voltage

- a voltage translation element that samples the output voltage level

- a comparator element that compares the reference and output level to produce an error signal

- a control element that can utilize this error signal to provide translation of the input voltage to produce the desired output

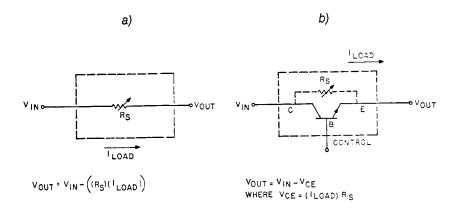

The control element depends on the design of the regulator and varies widely. The control determines the classification of the voltage regulator: series, shunt, or switch-

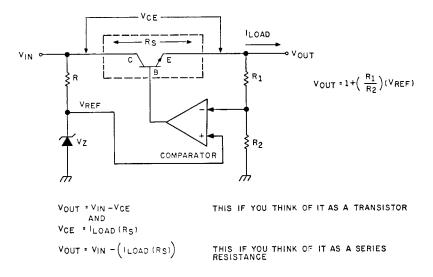

ing. For the series regulator, the control element regulates the output voltage by modulating the series element, usually a transistor, and causes it to act as a variable resistor (figure 1.8). As the input voltage increases, the series resistance  $R_s$  also increases, causing a larger voltage drop across it. In this way, the output voltage ( $V_{out}$ ) is maintained at a constant level.

Figure 1.7 A block diagram of a typical voltage regulator.

Figure 1.8 A series control element in the voltage regulator.

a) The series control element acts as a variable resistance, R<sub>s</sub>.

b) The series element is most often a transistor.

To accomplish this closed-loop control, a reference comparison and feedback system is incorporated into the hardware. A fixed and stabilized reference voltage is easily produced by a zener diode. The current produced is low, however; the device could not serve as a power regulator by itself.

The voltage translator connected to the output of the series control element produces a feedback signal that is proportional to the output voltage. In its simplest form, the voltage translator is a resistor-divider network. The two signals, reference and feedback, provide the necessary information to the voltage comparator for closed loop feedback to occur (figure 1.9). The output of the comparator effectively drives the base of the series pass transistor so that the voltage drop across the transistor will be maintained at a stabilized preset value when subtracted from the input voltage.

Modern power supply designers can still use individual components to construct the modular elements of a series voltage regulator, but most reserve this laborious endeavor for specialized applications. The ZAP computer system outlined here requires +5 V, +12 V, and -12 V. The combined temperature, stability, and drift

tolerances cannot exceed  $\pm 5\%$  on any of the three set points. The easiest way to minimize risk is to reduce the number of circuit components to the bare minimum. Other designers had the same idea and thus the three-terminal regulator was invented. Figure 1.10 is the block diagram of such a device.

Figure 1.9 A schematic diagram of a series voltage regulator.

Figure 1.10 A block diagram of a three-terminal voltage regulator.

Basically, a three-terminal regulator incorporates all the individual transistors, resistors, and diodes into a single integrated circuit. While simple to use, these devices have a far more complicated internal structure than the series regulator of figure 1.9. Only three terminals are necessary in applications where the fixed output is a standard value such as:  $\pm 5$  V,  $\pm 6$  V,  $\pm 8$  V,  $\pm 12$  V,  $\pm 15$  V or  $\pm 24$  V. The three connections are unregulated DC from our input filter, a ground reference, and finally, regulated DC output.

In a three-terminal regulator, the voltage reference is the most important part because any abnormality or perturbation will be reflected in the output. Therefore, the reference must be stable and free from noise or drift. More advanced designs use bandgap reference circuits rather than zener diodes. Because of its complexity, such an approach is practical only in the integrated circuit (IC) environment. Essentially, a bandgap reference voltage is derived from the predictable temperature, current, and voltage relationships of a transistor base-emitter junction.

Another advantage of the three-terminal regulator is that in monolithic circuits, stable current sources can easily be realized by taking advantage of the good matching and tracking capability of monolithic components. Also, as in the previous case, the designer can add as many active devices as necessary without significantly increasing the IC circuit area. Operation of the reference circuit at a constant current level reduces fluctuations due to line-voltage variation. Thus, the output has increased stability. The error amplifier is also operated at a constant current to reduce line-voltage influence.

The most important consideration for the hobbyist is that these chips incorporate protective circuitry, guarding the regulator from certain types of overloads. They protect the regulator against short-circuit conditions (current limit); excessive input/output differential condition (safe operating area); and excessive junction temperatures (thermal limit). Of course, all this circuitry is designed to protect the regulator, not the computer.

#### **CHOOSING A REGULATOR**

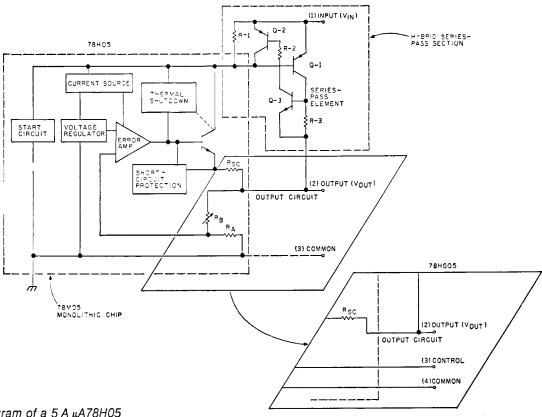

The 5 A  $\mu$ A78H05 hybrid voltage regulator has all the inherent characteristics of the monolithic three-terminal regulator (ie: full protective circuitry). Each hermetically-sealed TO-3 package contains a  $\mu$ A78M05 monolithic regulator chip driving a discrete series-pass transistor Q1 and two short-circuit-detection transistors Q2 and Q3 (see figure 1.11). The pass transistor is mounted on the same beryllium oxide substrate as the regulator chip, thus insuring nearly ideal thermal transfer between Q1 and the temperature-sensing circuit of the 78M05.

Figure 1.11 A block diagram of a 5 A μA78H05 and μA78HG05 hybrid voltage regulator.

|                             |                                                                | μΑ78H05C |         |     |       |

|-----------------------------|----------------------------------------------------------------|----------|---------|-----|-------|

| CHARACTERISTICS             | CONDITIONS                                                     |          | MIN TYP |     | UNITS |

| Output Voltage              | I <sub>OUT</sub> = 2.0 A, V <sub>IN</sub> = 10 V               | 4.8      | 5.0     | 5.2 | ٧     |

| Line Regulation             | V <sub>IN</sub> = 8.5 to 25 V                                  |          | 10      | 50  | m۷    |

| Load Regulation             | 10 mA ≤ I <sub>OUT</sub> ≤ 5.0 A. V <sub>IN</sub> = 10 V       |          | 10      | 50  | mV    |

| Quiescent Current           | IOUT = 0, VIN = VOUT + 5.0 V                                   |          |         | 10  | mA    |

| Ripple Rejection            | I <sub>OUT</sub> = 1.0 A, f = 210 Hz, 5.0 V P-P                | 60       |         |     | dB    |

| Output Noise                | 10 Hz ≤ f ≤ 100 kHz, V <sub>IN</sub> = V <sub>OUT</sub> + 50 V |          | 40      |     | µVRMS |

|                             | I <sub>O</sub> = 50 A                                          |          | 3.0     |     | ٧     |

| Dropout Voltage             | I <sub>O</sub> = 3.0 A                                         |          | 26      |     | ٧     |

| Short Circuit Current Limit | V <sub>IN</sub> = 10 V                                         |          | 70      |     | Apk   |

**Figure 1.12** Electrical characteristics of the μA78H05 voltage regulator.

The output circuit is designed so that the worst-case current requirement of the Q1 base, added to the current through R2, always remains below the current-limit threshold of the 78M05. Resistor R1, in conjunction with Q2 and Q3, makes up a current sense and limit circuit to protect the series-pass device from excessive current drain.

Safe area protection is achieved by brute force and is designed with the hobbyist in mind. The series-pass transistor is capable of handling the short-circuit current at the maximum input voltage rating of the 78H05. (See figure 1.12 for the electrical characteristics of the 78H05.)

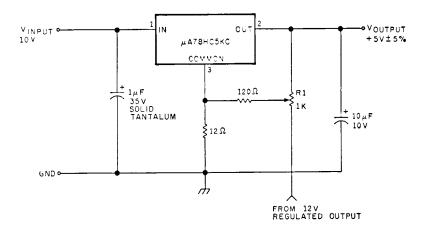

The output of the device is nominally 5.0 V but can vary between 4.8 and 5.2 V. Even though this falls within the 5.0 V  $\pm 15\%$  tolerance necessary to run the computer, there might be a problem with the voltage drop in the cabling between the power supply and the computer. Up to 0.5 V could be lost in the wiring and connectors. Remember that at 5 A, a resistance of only 0.1 ohms can cause a 0.5 V drop. Unfortunately, the 78H05 is a fixed-output device when referenced to ground. If 4.8 V happens to come out, "that's all you gets" (sic). But, in a classic case of engineering razzle-dazzle, we can fool the regulator by making the ground reference adjustable. Figure 1.13 shows the circuit that makes this possible. A potentiometer sourced from the -12 V supply creates a relative-ground reference for the 78H05. If the particular device in question had an output of 4.95 V, and we adjusted R1 for a potential of 0.20 V on the common regulator pin, the output referenced to ground would change to 4.95 + 0.20, or 5.15 V. For the fanatics in the crowd, this particular circuit also allows a high-output device to be reduced to 5.00 V by selecting an appropriate negative voltage ground reference pin.

Figure 1.13 Adding "trim adjust" to the μΑ78H05 three-terminal voltage regulator.

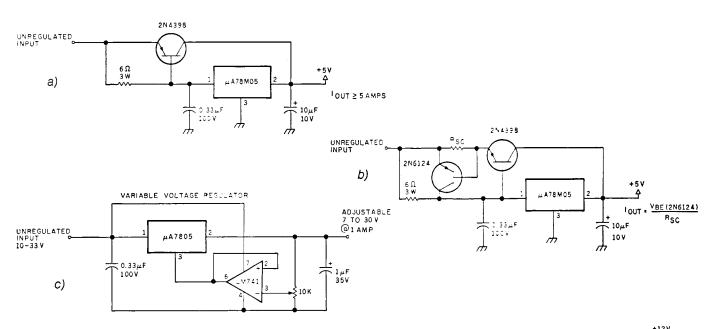

With the 5 V supply complete, our next concern is the +12 V and -12 V supplies. Other devices within the 7800 family of regulators will satisfy the requirements. The 7812 and a 7912 are 1 A positive and negative regulators respectively; they exhibit the same protection characteristics as the 78H05. Figures 1.14 and 1.15 outline the exact specifications. Because we are dealing with much lower currents than the +5 V supply, there is considerably less concern over voltage losses through connecting cables, and it is unnecessary to add trim adjustment circuitry. Figure 1.16 is the finished schematic of the ZAP power supply. Additional regulator circuit diagrams (figures 1.17a, b, c and d) are included to demonstrate how the 7800 series of regulators can be used in our application. Are we finished yet? Of course not. Close examination of figure 1.16 shows two items not discussed previously: heat sinks and overvoltage protection. These two subjects and a short discussion of the importance of correct layout complete the chapter.

| ELECTRICAL CHARACTERISTICS |                       |                                 | 3 μF, C <sub>OUT</sub> | = 0.1 µF, |      |          |

|----------------------------|-----------------------|---------------------------------|------------------------|-----------|------|----------|

| CHARACTERISTICS            |                       | CONDITIONS                      | MIN                    | TYP       | MAX  | Ų        |

| Output Voltage             | T <sub>J</sub> = 25°C |                                 | 11.5                   | 12.0      | 12.5 |          |

|                            | T <sub>J</sub> = 25°C | 14.5 V < V <sub>IN</sub> < 30 V |                        | 10        | 120  | <u> </u> |

| Line Regulation            |                       | 16 V < V <sub>IN</sub> < 22 V   |                        | 3.0       | 60   |          |

|                            | - aria                | 5 mA < 10UT < 1.5 A             |                        | 12        | 120  | Π        |

| Load Regulation            | T <sub>J</sub> = 25°C | 250 mA < IOUT < 750 mA          |                        | 4.0       | 60   |          |

|                            | 15.5 V < V            | 15.5 V < V <sub>IN</sub> < 27 V |                        |           |      | Γ        |

| Output Voltage             | 5 mA < 10UT < 1.0 A   |                                 | 11.4                   |           | 12.6 |          |

| •                          | P < 15 W              | P < 15 W                        |                        |           |      | 1        |

Tj = 25°C

Quiescent Current

Output Voltage

Short Circuit Current

m۷

6.0

.. 47917

| Quiescent Current Change                          | with line | 15 V < ViN <                    | 30 V                              |     | 1    | 0.8 | mA              |

|---------------------------------------------------|-----------|---------------------------------|-----------------------------------|-----|------|-----|-----------------|

|                                                   | with load | 5 mA < I <sub>OUT</sub> < 1.0 A |                                   |     |      | 0.5 | mA              |

| Output Noise Voltage                              |           | TA = 25°C, 10 Hz < f < 100 kHz  |                                   |     | 8    | 40  | μV/VouT         |

| Ripple Rejection                                  |           | t = 120 Hz, 15 V < VIN < 25 V   |                                   | 61  | 71   |     | dB <sub>4</sub> |

| Dropout Voltage                                   |           | 10UT = 1.0 A, TJ = 25°C         |                                   |     | 2.0  | 2.5 | ٧               |

| Output Resistance                                 |           | f = 1 kHz                       |                                   |     | 18   |     | mΩ              |

| Short Circuit Current                             |           | TJ = 25°C, VIN = 35 V           |                                   |     | 0.75 | 1.2 | A               |

| Peak Output Current                               |           | T <sub>J</sub> = 25°C           |                                   | 1.3 | 2.2  | 3.3 | A               |

| Average Temperature Coefficient of Output Voltage |           | 10UT = 5 mA                     | -55°C < T <sub>J</sub> < +25°C    |     | Ī    | 0.4 | mV/°C/          |

|                                                   |           |                                 | +25° C < T <sub>J</sub> < +150° C |     |      | 0.3 | Vout            |

Figure 1.14 Electrical characteristics of the μA7812 voltage regulator.

| CHARACTERISTICS                                      |           | CONDITIONS  T1 = 25°C             |                                   | MIN   | TYP<br>-12.0 | MAX<br>-12.5 | UNITS              |

|------------------------------------------------------|-----------|-----------------------------------|-----------------------------------|-------|--------------|--------------|--------------------|

|                                                      |           |                                   |                                   | -11.5 |              |              |                    |

| Output Voltage                                       |           | <del></del>                       | -14.5 V < V <sub>IN</sub> < -30 V |       | 10           | 120          | mV                 |

| Line Regulation                                      |           | Tj = 25°C                         | -16 V < VIN < -22 V               |       | 3.0          | 60           | mV                 |

|                                                      |           | т」 = 25°C                         | 5 mA < IOUT < 1.5 A               |       | 12           | 120          | m∨                 |

| Load Regulation                                      | ļ         |                                   | 250 mA < IOUT < 750 mA            |       | 4.0          | 60           | mV                 |

|                                                      |           | -15.5 V ≤ V <sub>IN</sub> ≤ -27 V |                                   |       |              |              |                    |

| Output Voltage                                       |           | 5 mA < IOUT < 1.0 A               |                                   | -11.4 |              | -12.6        | V                  |

|                                                      |           | p < 15 W                          |                                   |       |              |              |                    |

| Quiescent Current                                    |           | T <sub>J</sub> = 25°C             |                                   |       | 1.5          | 3.0          | mA                 |

| 0                                                    | with line | -15 V < V <sub>IN</sub> < -30 V   |                                   |       |              | 1.0          | mA                 |

| Quiescent Current Change                             | with load | 5 mA < 1 <sub>OUT</sub> < 1.0 A   |                                   |       |              | 0.5          | mA                 |

| Output Noise Voitage                                 |           | TA = 25°C, 10 Hz < f < 100 kHz    |                                   |       | 25           | 80           | μV/V <sub>OU</sub> |

| Ripple Rejection                                     |           | f = 120 Hz, -15 V < ViN < -25 V   |                                   | 54    | 60           |              | d <b>B</b>         |

| Dropout Voltage                                      |           | IOUT = 1.0 A, TJ = 25°C           |                                   |       | 1.1          | 2.3          |                    |

| Peak Output Current                                  |           | T <sub>J</sub> = 25°C             |                                   | 1.3   | 2.1          | 3.3          | A                  |

| Average Temperature Coefficient of<br>Output Voltage |           | IOUT = 5 mA, -55°C < Tj < 150°C   |                                   |       |              | 0.3          | mV/°C/<br>VOUT     |

**Figure 1.15** Electrical characteristics of the μA7912 voltage regulator.

VIN = -35 V, TJ = 25°C

Figure 1.16 A schematic diagram of the finished power supply for the ZAP computer.

**Figure 1.17** Additional voltage regulator circuit diagrams to demonstrate how the 7800 series of regulators can be used.

- a) A high-current voltage regulator using a 500 mA 78M05 three-terminal regulator.

- b) A high-current short-circuit protected voltage regulator, an enhanced version of figure 1.17a.

- c) Using a 7805 +5 V voltage regulator to produce a higher output voltage.

- d) A dual  $\pm$  12 V tracking voltage regulator.

#### LAYOUT IS IMPORTANT

Integrated circuit regulators employ wide-band transistors in their construction to optimize response. As a result, they must be properly compensated to ensure stable closed-loop operation. Their compensation can be upset by stray capacitance and line inductance of an improper layout. Circuit lead lengths should be held to a minimum, and external bypass capacitors in particular should be located as close as possible to the regulator control circuit.

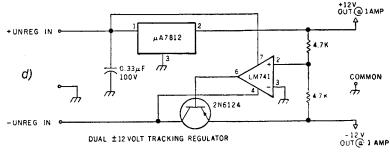

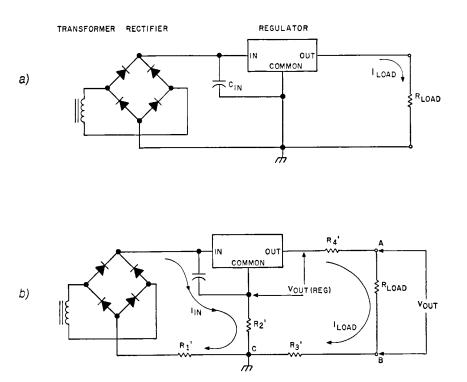

Figure 1.18a illustrates a typical layout of the components of our supply, and figure 1.18b details the areas that can cause problems. Improper placement of the input capacitor can induce unwanted ripple on the output voltage. This occurs when the current flowing in the input circuit influences the common ground line of the regulator. The voltage drop produced across R2' will cause the output of the regulator to fluctuate in the same manner as the voltage trim circuit we discussed previously. The peak currents in the input circuit (which consists of the rectifier and filter capacitor) can be tens of amperes during charge cycles. These high-current spikes can cause substantial voltage drops on long-lead lengths or thin-wire connections. They can also degrade performance to the point that proper input voltage to the regulator cannot be maintained except during low-current operation.

The output current loop is also susceptible to circuit layout. In a three-terminal regulator, the fixed-output voltage  $V_{OUT(REG)}$  is referenced between "out" and "common" of the chip. Because the load current flows through R2', R3', and R4', as well as the load itself, these combined voltage losses may reduce  $V_{OUT}$  to an intolerable level. Notice that the ground for this circuit is at point C while the present R load is between points A and B. If another load, more memory for example, is connected to this supply between points A and C, it would have a different  $V_{OUT}$ . Adjusting the trim setting of such a seesaw supply can be dangerous; it's possible to have one load completely within tolerance and another over or under voltage. One last point to consider is that R4' serves to negate the purpose of the regulator because it continually reduces  $V_{OUT}$  as the load current increases.

Figure 1.18 A typical layout of the power supply components and associated problems.

- a) A typical layout.

- b) Errors contributed by the layout in figure 1.18a.

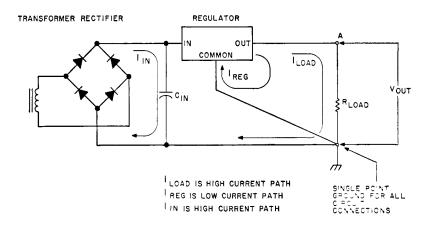

Figure 1.19 is the block diagram of a proper layout. All high-current paths should use heavy wire to minimize resistance and resultant voltage drops. You'll notice now that the input and output circuit current paths are separated effectively. Note that the wires from the rectifier go directly to the capacitor and that two wires from the capacitor send power to the rest of the circuit. If you follow this convention and use two separate pairs of leads, you can eliminate input-circuit induced errors.

Finally, we need to discuss the concept of the single-point ground. One point in the power supply must be designated as ground; the grounds of all other supplies and loads are connected to it. In practical terms, the best way to implement this ground connection is to use a metal strip or several lengths of heavy wire soldered together. The strip is a ground bus with such a low resistance that a voltage measured between point A and any place along the bus will be virtually undetectable. Another +5 V bus should be connected to the output of the supply so that voltage distribution throughout the circuit is consistent. Use thick wire in power supplies. Even if zero-resistance wire isn't easily obtainable, always remember—there is no such thing as wire that is too thick!

Figure 1.19 A block diagram of a proper layout for the power supply components.

#### THERMAL CONSIDERATIONS

You've just built the power supply I've outlined, flipped on the power, and everything works. After a few minutes, something happens and the computer suddenly stops running. Naturally, you start looking around and touching things. Eventually, your fingers will end up on the regulator chip. Immediately you scream, jump back, and in the process knock over the computer and your celebration martini. If you are lucky, your fingers will be the only thing burned!

When not properly cooled, the regulators will protect themselves from destruction by reducing their output or completely shutting off. In this case, the system could cease to function. A more catastrophic problem arises from ICs that use all three voltages for normal operation. Loss of one or more of these voltages could permanently damage the device. This will never happen if power dissipation is limited and the proper cooling methods are employed.

The first step is to check the power dissipation of our design with the ratings of the particular devices. In practical terms, power, expressed in watts, is volts times amperes:

$$P_D = E \times I$$

$$P_{D(NOM)} = (V_C - V_{OUT}) \times 5 \text{ A}$$

$$= (10 - 5) \times 5$$

$$= 25 \text{ W}$$

$$P_{D(PEAK)} = (V_{PEAK} - V_{OUT}) \times 5 \text{ A}$$

$$= (12.5 - 5) \times 5$$

$$= 37.5 \text{ W}$$

$$P_{D(AVERAGE)} = \frac{37.5 + 25}{2} = 31.25 \text{ W}$$

This means that under full load conditions, about 30 W of heat will be produced by the 78H05. The device is fortunately rated for 50 W at  $25^{\circ}$ C and is still capable of handling 30 W up to  $75^{\circ}$ C.

Although the internal power dissipation is limited, the junction temperature must be kept below the maximum specified temperature (125°C) in order for the device to function at all. To calculate the heat sink required, there are specific equations to solve.

The required thermal data and calculations follow:

Typical

$$\theta_{JC} = 2.0$$

Maximum  $\theta_{JC} = 2.5$

Typical  $\theta_{JA} = 32$  Maximum  $\theta_{JA} = 38$

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_{A}}{\theta_{JC} + \theta_{CA}} \qquad \text{for } \theta_{CA} = \theta_{CS} + \theta_{SA}$$

Solving for T<sub>J</sub>,

$$T_J = T_A + P_D(\theta_{JC} + \theta_{CA})$$

or without a heat sink,

$$P_{D(MAX)} = \frac{T_{J(MAX)} - T_A}{\theta_{JA}}$$

$$T_{J} = T_{A} + P_{D}\theta_{JA}$$

where  $T_I = \text{junction temperature}$

$T_A$  = ambient temperature

$P_p$  = power dissipation

$\theta_{JC}$  = junction to case thermal resistance

$\theta_{JA}$  = junction to ambient thermal resistance

$\theta_{CA}$  = case to ambient thermal resistance

$\theta_{CS}$  = case to heat sink thermal resistance

$\theta_{SA}$  = heat sink to ambient thermal resistance

$$\theta_{JA} = \frac{T_J - T_A}{P_D} = \frac{125^{\circ}C - 25^{\circ}C}{31.25 W} = 3.2^{\circ}C/W$$

Because  $\theta_{JA}$  as calculated is less than  $\theta_{JA}$  from the specification sheet, a heat sink is definitely required, and a TO-3 type heat sink of  $3.2^{\circ}C/W$  is the minimum desired.

Before you size a heat sink for the 78H05, realize that there are two more regulators and two bridge rectifiers that will need heat sinking. Each 12 V regulator will average about 5 W dissipation. The diode bridge associated with the +5 V supply (remember the 2 V drop) dissipates about 10 W while the other is good for 2 W. Therefore, any heat sinks in the power supply must handle more than 50 W.

#### WHAT IS THE PRACTICAL METHOD FOR CHOOSING HEAT SINKS?

Choosing a heat sink can be easy or hard depending upon your outlook on rule of

thumb measures. We already know that we need a 50 W heat sink. It's easy to assume that buying one "rated for 50 W" from a local electronics supply will solve the problem. What this rating usually means, however, is that if 50 W is applied through a transistor to this sink, and the ambient temperature is 25°C, the surface temperature of the sink will climb to 100°C. Fried eggs anyone?

We must not forget that manufacturers' specs always refer to limiting maximum junction temperature, not to keeping the case cool enough to touch. Personally, I hate red-hot power supplies. To get a heat sink that would take our 50 W and stay about 60-70°C would probably mean getting one rated for 200-300 W! Remember that heat sinks are expensive—and big.

The simplest solution is best. I prefer forced air cooling. Put the 50 W on an economical heat sink of, say, a 100 W rating and put your money into a good fan. You can still run through all the calculations and determine how many square inches you need, but the effect of blowing a little air over a heat sink multiplies its capabilities enormously.

#### OVERVOLTAGE PROTECTION

The final area to be addressed in the power supply is overvoltage protection. As designed by manufacturers, regulators protect themselves by reducing output voltage or complete shutoff. The chances of computer component damage from low voltage is miniscule by comparison to overvoltage. It is unlikely to happen, but if the 78H05 were to accidentally short out, as much as 12.5 V would be applied to the +5 V bus. You could then kiss the computer good-bye!

| +5 volt OVP      |         |           | 12 volt OVP      |         |           |  |

|------------------|---------|-----------|------------------|---------|-----------|--|

| $D_1$            | 5.6 V   | 1N4734    | $\overline{D_1}$ | 13 V    | 1N4743    |  |

| SCR <sub>1</sub> | 50V 25A | 2N682     |                  | 50V 8A  |           |  |

| Fuse             | 6amp    | fast-blow | Fuse             | 1.5 amp | fast-blow |  |

The semiconductor components of this 12 volt OVP are reversed in polarity for the -12 volt OVP.

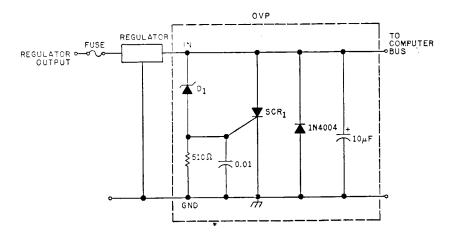

Figure 1.20 A simple overvoltage protection circuit.

The circuit of figure 1.20 is a simple OVP (over-voltage protector). It can be used as shown on the 5 V and 12 V supplies. The appropriate components are listed in the tables of figure 1.20. You'll notice that the fuses are rated higher than the output we've previously discussed. The fuse is for the OVP and not to protect the regulators. Unfortunately, the nature of fast-blow fuses is not to pass 5 A, if it is a 5 A fuse, but to open at 5 A. The fuse must have a higher rating in order to allow circuit operation at 5 A.

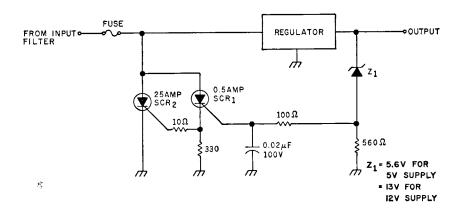

**Figure 1.21** A schematic diagram of a more complex overvoltage protection circuit. The crowbar section of the OVP can be located next to the fuse while the OVP sensor  $Z_1$  is located at the regulator output. This is a preferred placement of the parts if the sensor and clamp can be adequately separated. Low-current sensor  $Z_1$  fires SCR<sub>1</sub> in an overvoltage condition. SCR<sub>1</sub> in turn fires high-current SCR<sub>2</sub>. The combination of SCRs allows considerable leeway in the choice of SCR<sub>2</sub> since the question of gate current becomes less relevant.

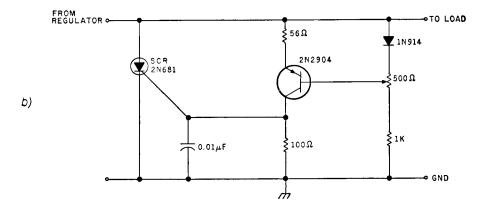

Because the short-circuit current of the 78H05 is 7 A, the 25 A silicon-controlled rectifier (SCR) will certainly make short work of the fuse if it triggers. Figures 1.21 and 1.22 are slightly more complex OVP circuits and can also be used.

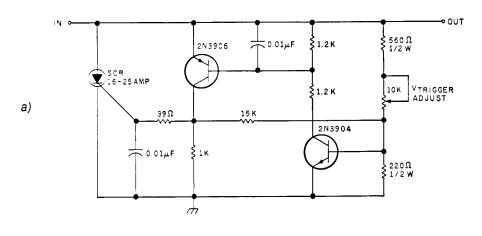

Figure 1.22 Schematic diagrams of adjustable-voltage overvoltage protection circuits.

- a) An adjustable-voltage OVP circuit with an internal current amplifier to drive the SCR gate.

- b) An alternate circuit for a simple adjustable-voltage OVP circuit.

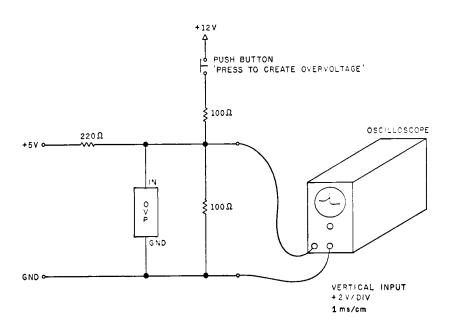

What does an OVP (often called an "overvoltage crowbar") do? It monitors a particular bus voltage and shuts it down if it goes above a predetermined level. OVP circuits can be designed to trigger 1 mV above our 5% tolerance band. Such circuits are not only complicated, but they may also create additional problems through accidental triggerings. The failure modes that are most likely to occur concern a regulator short or accidentally tying two buses together, for example the +5 V and +12 V. In either case, the result is a rapid voltage rise on the output lines. As voltage rises above the zener value, current flows into the SCR gate. At a certain point, usually below where any components would have been damaged, the SCR fires and shorts the output line to ground. The excessive current blows the fuse, eliminating the problem regulator or regulators (both fuses would blow if the +5 V and +12 V were connected). All this occurs very fast. The test circuit of figure 1.23 demonstrates what happens when the +5 V OVP suddenly has +12 V applied. Test circuits are the only way you ever want to see the action of an OVP. If your power supply functions properly, it should never trigger. The SCR never allows the line to go to 12 V before clamping it to ground. Replacing the fuse with a 220 ohm resistor allows multiple applications of the push button without replacing fuses.

Figure 1.23 A test circuit to demonstrate the action of the overvoltage protector.

### CHAPTER 2 CENTRAL PROCESSOR BASICS

There are many different microprocessors on the market and while instruction nomenclature is somewhat different for each one, the basic logical computing processes are similar in all devices. The rule to remember the next time a discussion turns to the capabilities of two computers is that "a computer is a computer." I don't wish to imply that they are all the same, but similarities abound and I would not like to spend a lifetime analyzing instruction sets and interfacing details before choosing one.

I once had lunch with the designer of one of the largest selling personal computer systems on the market. Thousands of computers had been sold, generating immense profits for the manufacturer. Our conversation eventually centered on the cost-effectiveness of his design. I had fanciful thoughts of a design team spending months reducing component count and analyzing instruction sets to determine minimum memory requirements. In actuality, my designer friend was given two months to come up with a manufacturable design. The investors' only question was the price and availability of the particular components he had chosen. Being an avid personal computer enthusiast, he simply built a computer around the microprocessor he already owned. The eventual advertising for his system touted the advanced architecture embodied in the central processor, but no machine-language programming facility was available to the user. It had only a high-level language BASIC interpreter and was, from an engineering point of view, simply a black-box computer. He could have used any microprocessor. So much for textbook engineering design.

Unfortunately, the hobbyist who is building a microcomputer from scratch, and who won't be making a black box, has to try to pick a device that is somewhere in the middle of the performance and capability spectrum. The general rule that all computers perform similar functions is true, but a printed-circuit board is a luxury. The hobbyist who has to do all the wiring by hand will surely be interested in efficient design. It's a fact that some of the more esoteric microprocessors require very expensive peripheral circuitry. Even devices that seem quite straightforward, with limited instruction sets, can require 50 or more ICs as interface elements. The ultimate configuration should be a trade-off between circuit complexity, ease of testing, and component price.

#### MICROPROCESSOR ARCHITECTURE

The internal architecture of the microprocessor determines the support devices required to make a microcomputer system. Perhaps the best place to start is to briefly discuss the major architectural differences.

Definition: A microcomputer is a logical machine that manipulates binary numbers (data) and processes this information by following an organized sequence of program steps referred to as instructions.

All microcomputers, like all computers, have the following features:

- 1. Input Facilities must exist to allow the entrance of data or instructions.

- 2. **Memory** The program sequence must be stored before and after execution, and resources must be available to store the result of any computations.

- 3. Arithmetic logic unit Performs arithmetic operations on input or stored data.

- **4.** Control section Makes decisions regarding program flow and process control based on internal states of the results of arithmetic computations.

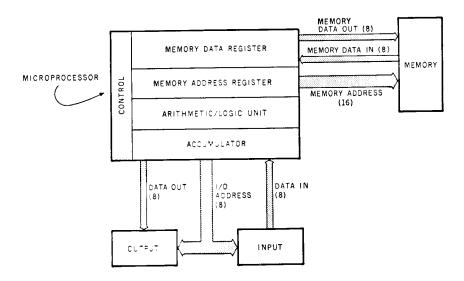

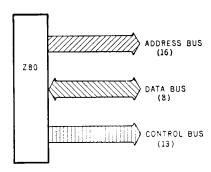

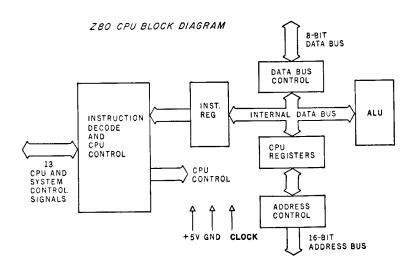

- Output The results are delivered to the user or stored in an appropriate medium.

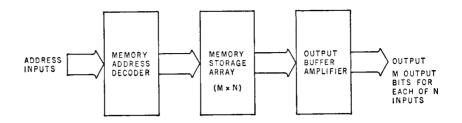

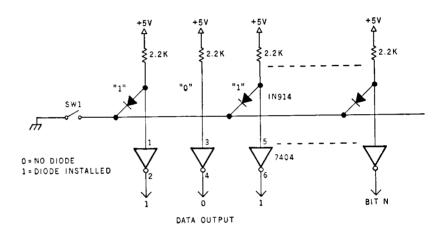

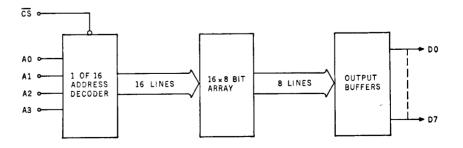

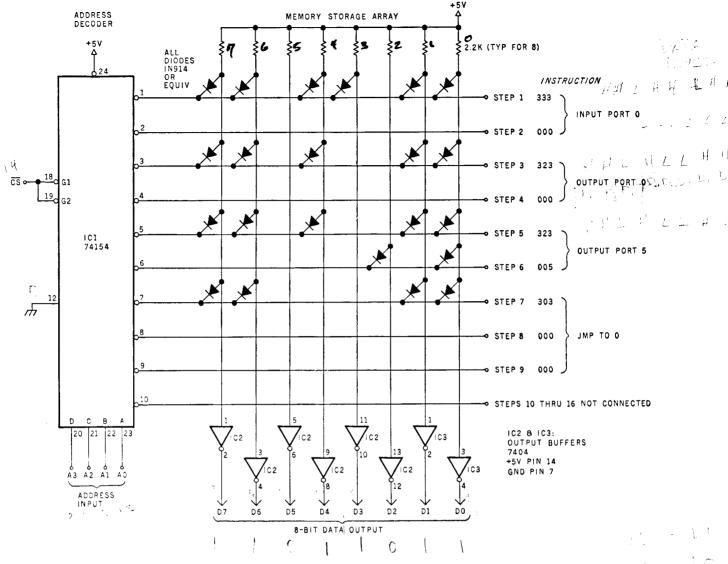

The microprocessor is the single integrated circuit around which a microcomputer is constructed. The microprocessor is a device; the microcomputer is a system. In their least complex form, microprocessors include only the functions of items three and four and must rely on external devices attached to buses to perform the other tasks. Figure 2.1 is the basic block diagram of an 8-bit microcomputer and shows the interconnection of these buses and support elements. The computer in figure 2.1 uses six separate buses: memory address, memory data in and out, I/O address, and data input and output. The microprocessor contains a central processor that consists of the circuitry required to access the appropriate memory and I/O locations and interpret the resulting instructions that are also executed in this unit. The central processor also contains the ALU (Arithmetic and Logic Unit), which is a combination network that performs arithmetic and logical operations on the data. Additionally, the central processor includes a control section that governs the operations of the computer, and the various data registers used for manipulation and storage of data and instructions.

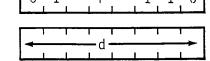

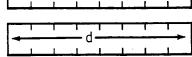

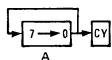

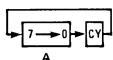

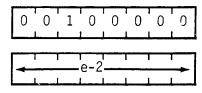

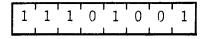

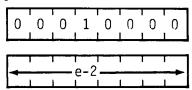

**Figure 2.1** A basic block diagram of a microcomputer illustrating the data busing concept. Numbers in parentneses are the usual required quantity of physical wires to perform bus functions for an 8-bit microprocessor.

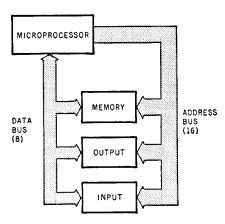

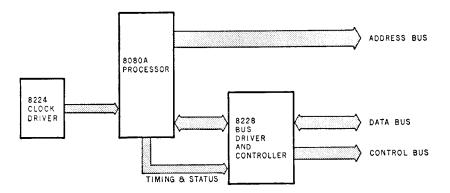

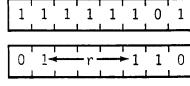

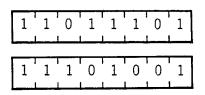

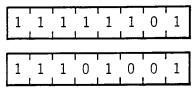

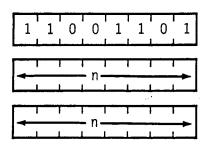

Actually few microprocessors support six separate buses. The number of pins that would be required on the IC is out of the question. Instead, to reduce pinouts, component manufacturers often combine the data input and output buses and make them "bidirectional." During an output instruction, data flows from the microprocessor to the output device and vice versa during an input instruction. To further cut the number of pins required on the central processor, the memory address bus can also serve as the address bus for input and output devices. During input/output instructions, the address present on the address lines references a particular input/output device(s). The resulting reduced configuration is shown in figure 2.2.

The concept of two buses is easy to understand and, from a hardware point of view, easy to utilize. The buses are time and function multiplexed. That is, during memory operations, the bits on the address bus refer to a memory location, and data on the data bus represent the content of memory. The direction of the data flow (to or from the central processor) is controlled within the microprocessor. Activities with input/output devices are performed in a similar fashion. During those instructions, input or output data and device addresses occupy the buses.

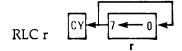

**Figure 2.2** A block diagram of a microcomputer utilizing multiplexed bi-directional busing techniques to reduce pinout.

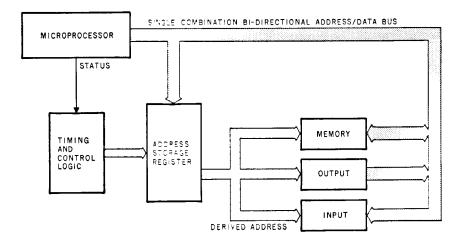

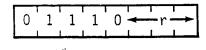

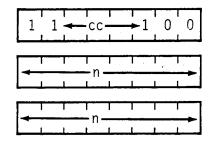

The number of bus wires can be further reduced by combining both data and address on the same lines and time multiplexing the data transfer along them. Figure 2.3 illustrates this final configuration. This method requires additional circuit elements to demultiplex and store pertinent data. The additional external components necessary to use this architectural feature defeat its purpose and make its use inadvisable for the hobbyist. There are other microprocessors that are simpler to use.

Figure 2.3 A block diagram of a microcomputer utilizing a single multiplexed bi-directional bus for both memory and input/output functions.

When building rather than buying a personal computer, the following criteria must be carefully considered:

- 1. **Circuit complexity** Keep components to a reasonable minimum. The more components in a design, the more likelihood of wiring errors and faulty devices.

- 2. Cost While cost is important, it should not be the primary consideration. Any microprocessor function could be simulated by using small scale integrated logic; however, indirect costs resulting from using 200 chips to replace 3 or 4 LSI (large scale integration) devices would negate the value of using cheaper parts initially. On the other hand, in the semiconductor industry, density means dollars. The more functions a device can provide, and the fewer components necessary to ac-

- complish these tasks, the higher the price. The level of integration incorporated in a homebrew computer should fit somewhere in the middle. The ZAP computer outlined in this book is a prime example of this philosophy. It uses a combination of cost-effective LSI (large scale integration) and inexpensive SSI (small scale integration) to produce a computer that the hobbyist can truly build, test, and use.

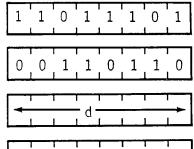

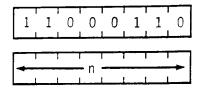

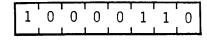

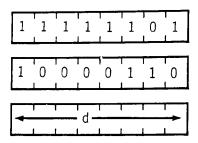

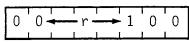

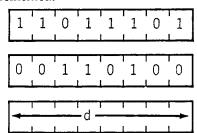

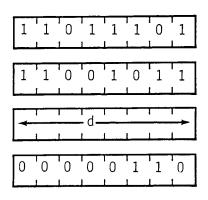

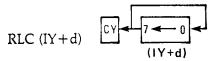

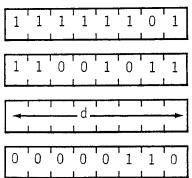

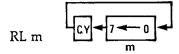

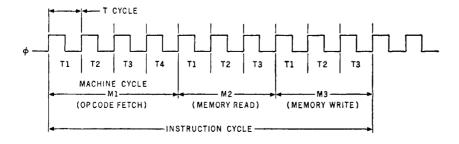

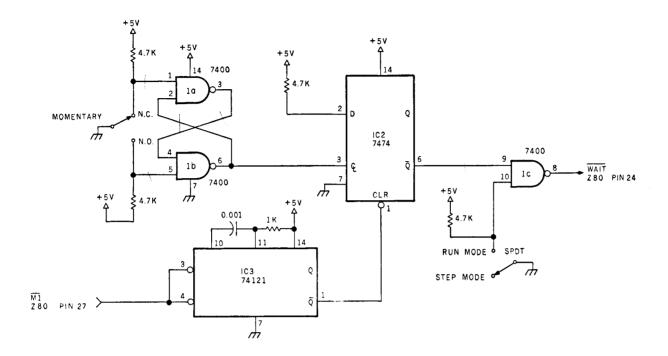

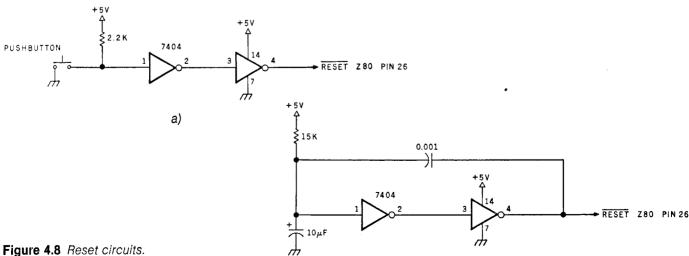

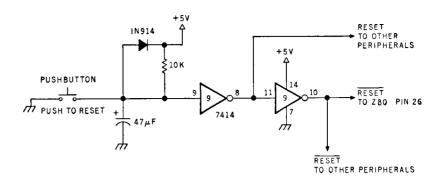

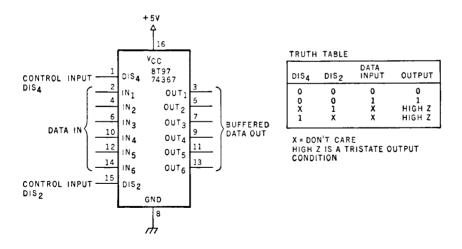

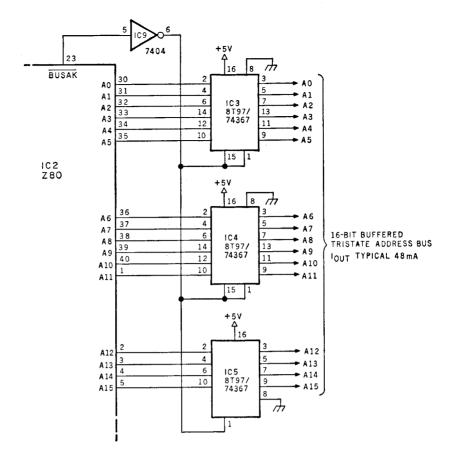

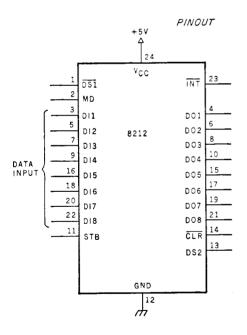

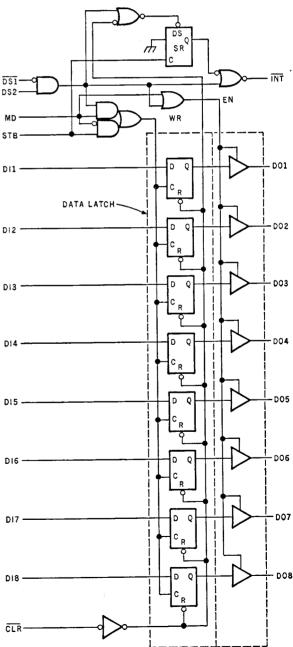

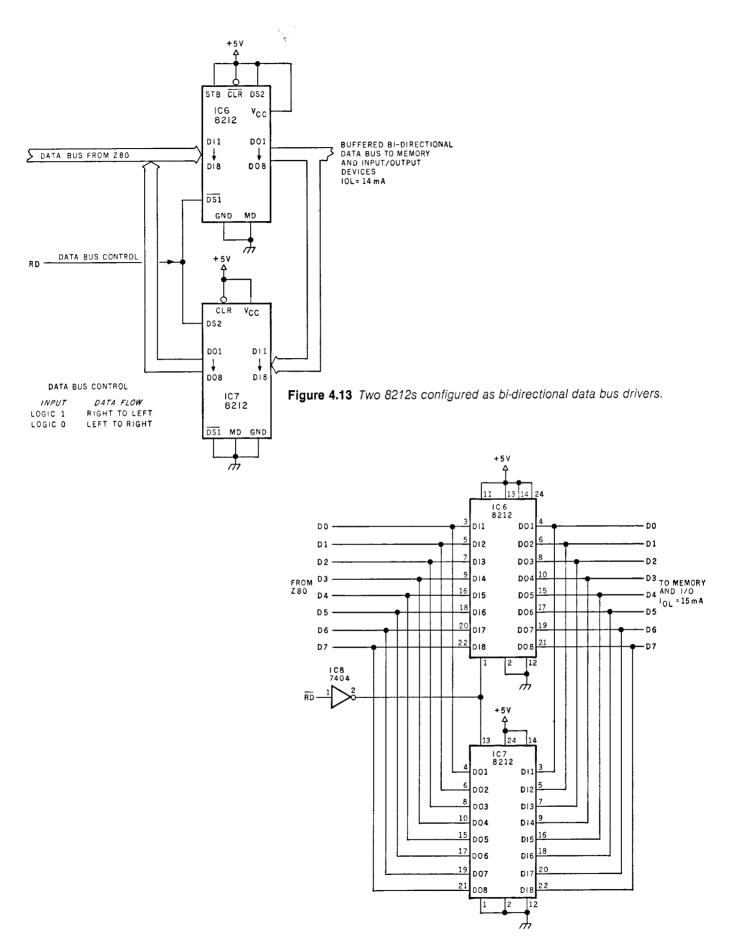

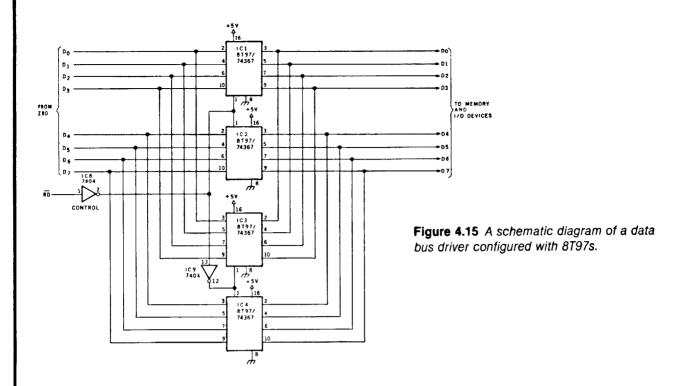

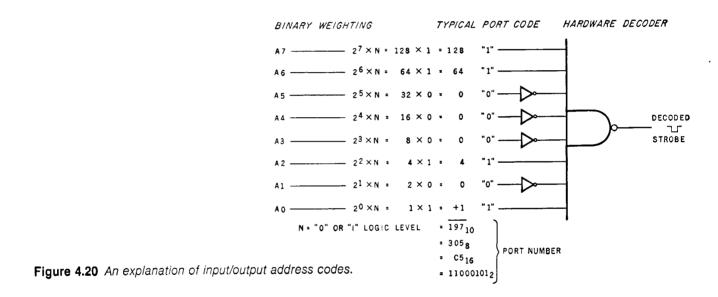

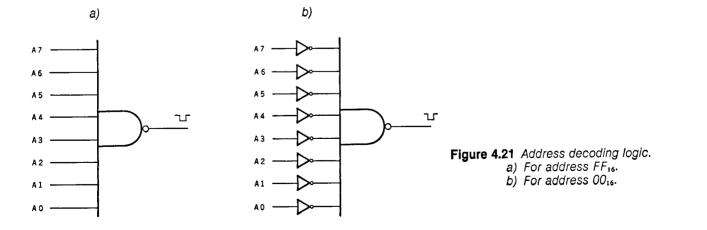

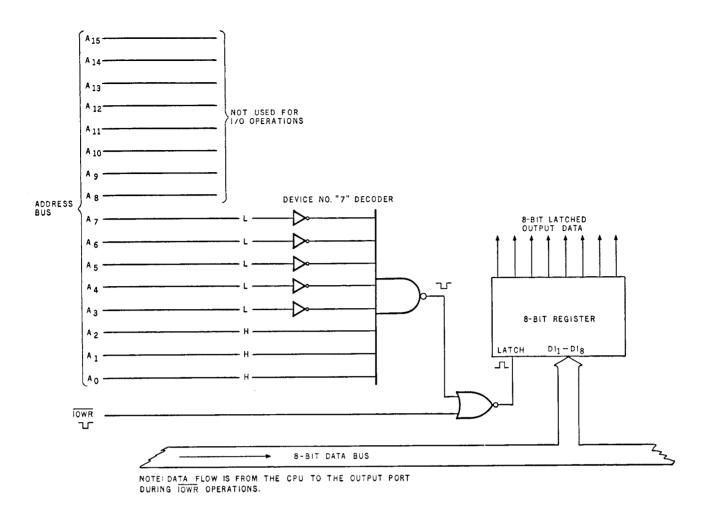

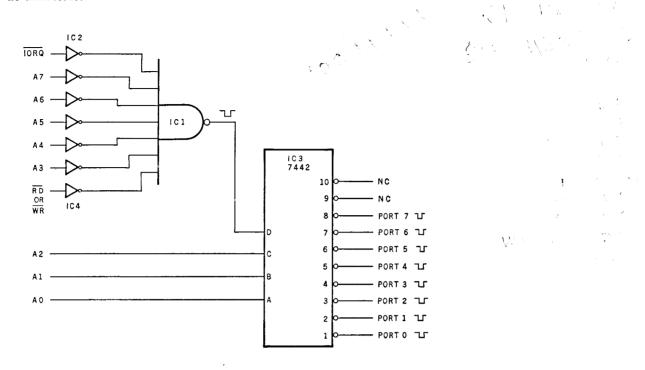

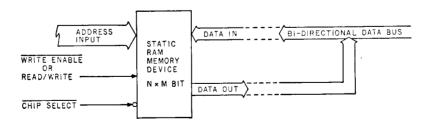

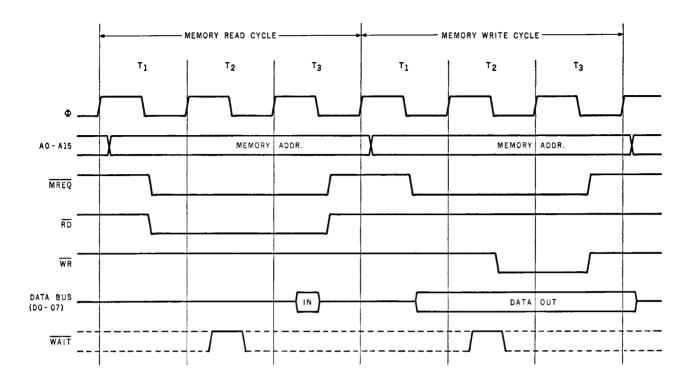

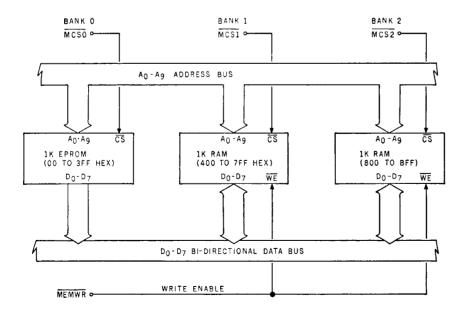

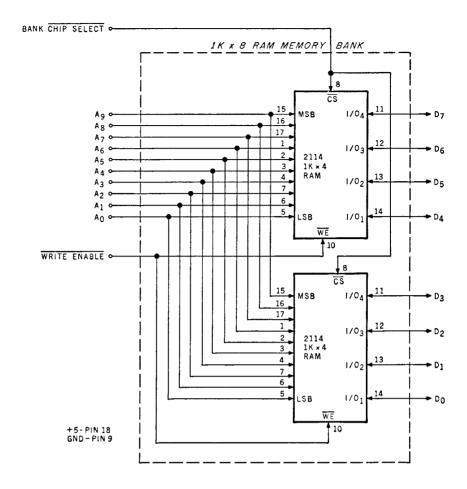

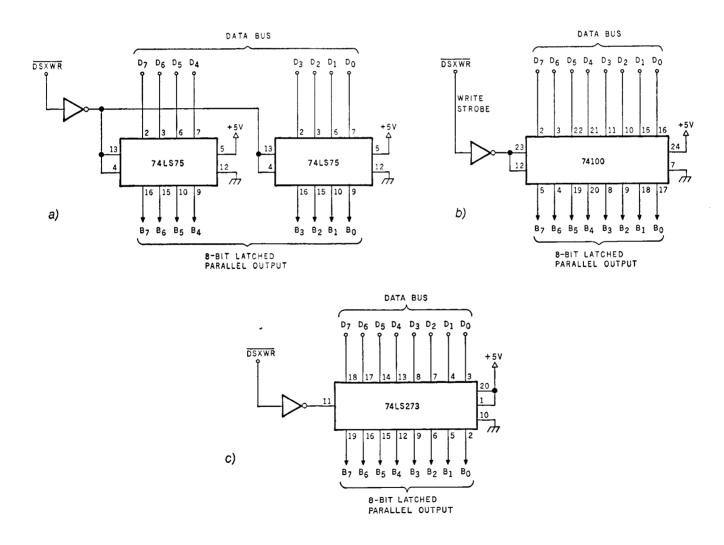

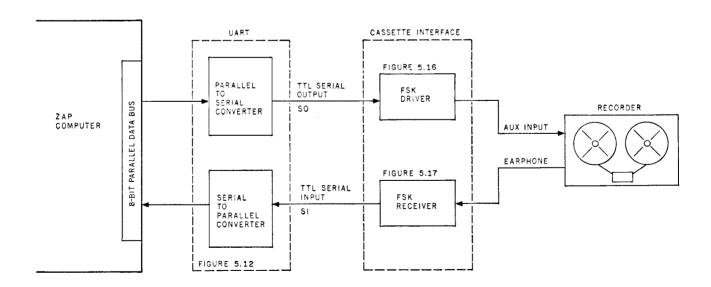

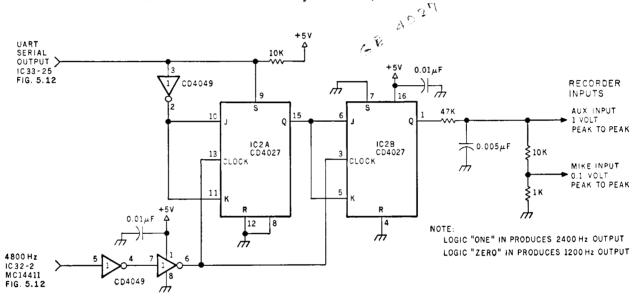

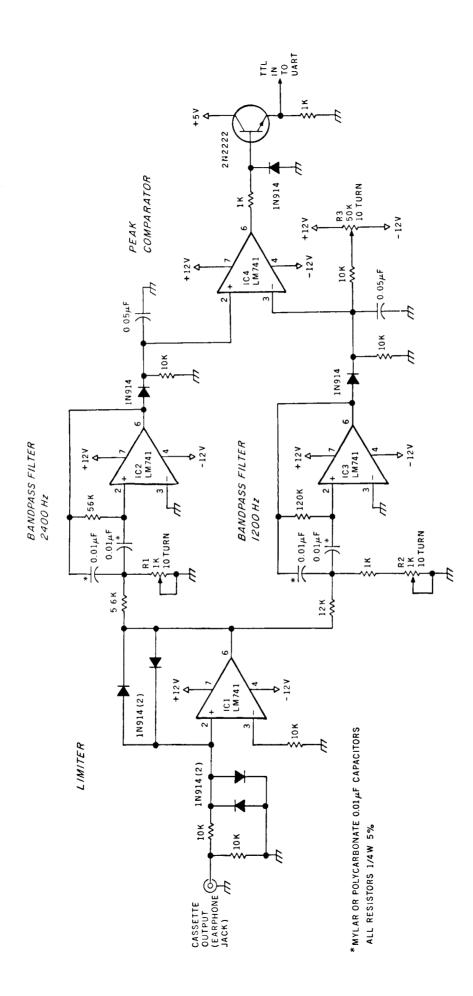

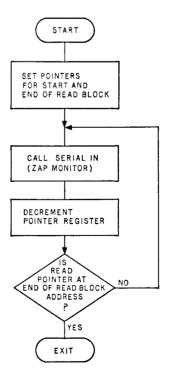

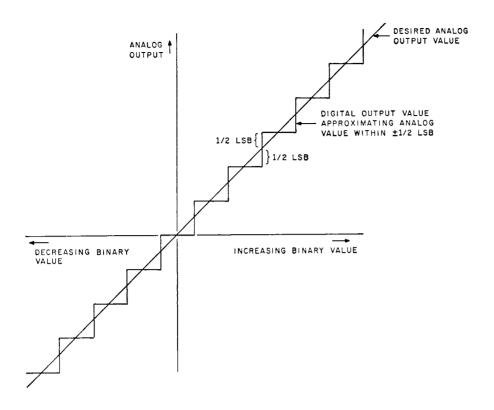

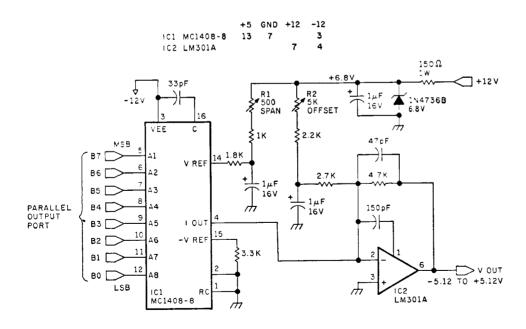

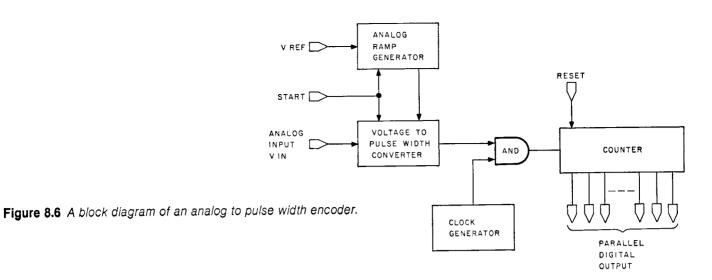

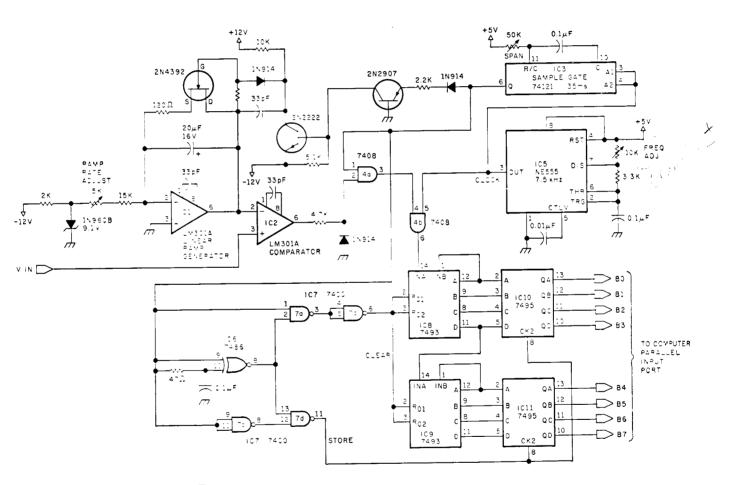

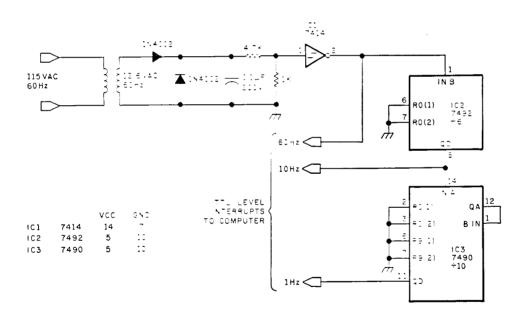

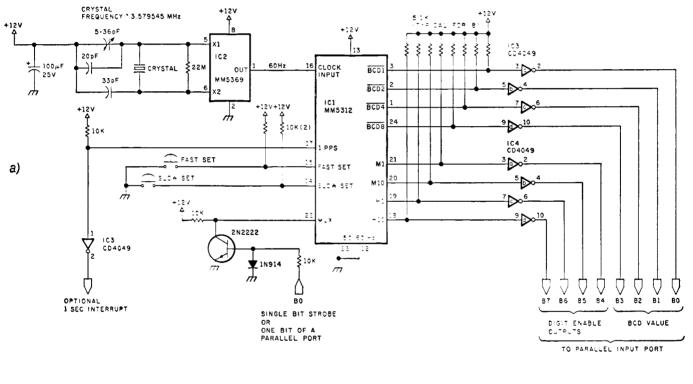

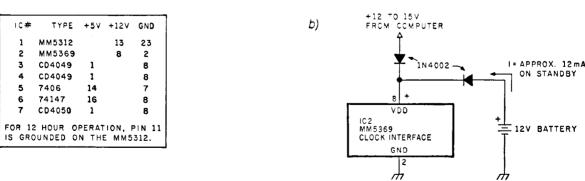

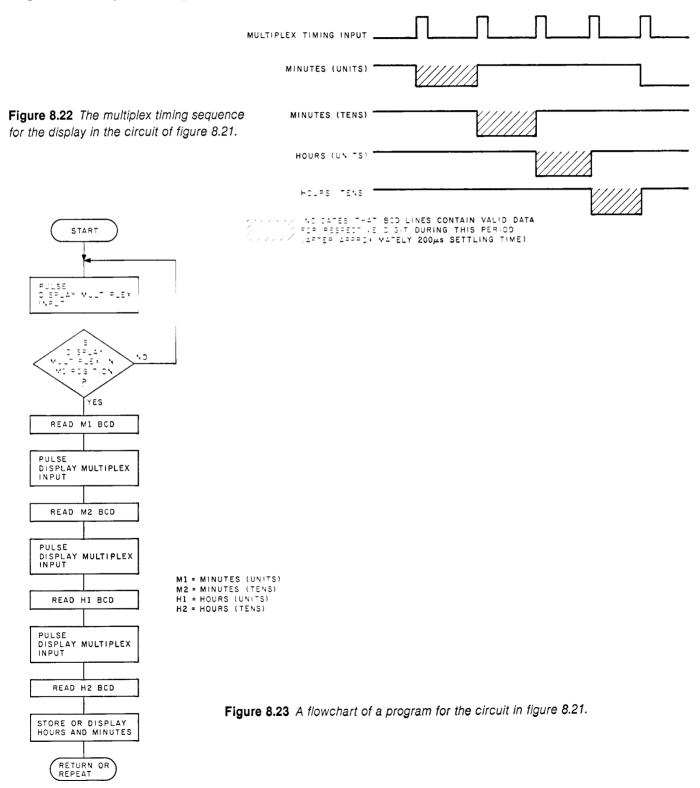

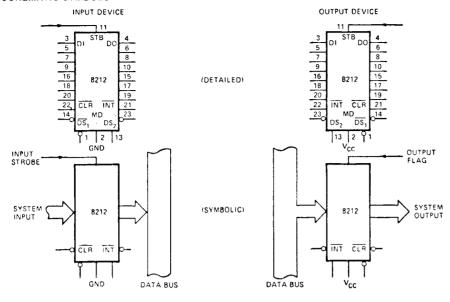

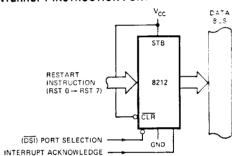

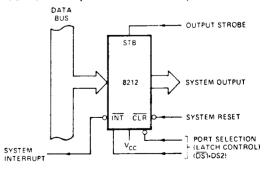

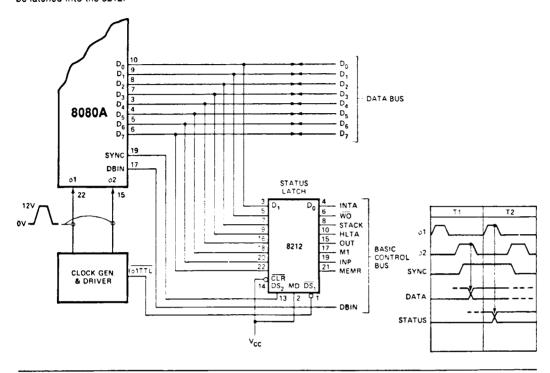

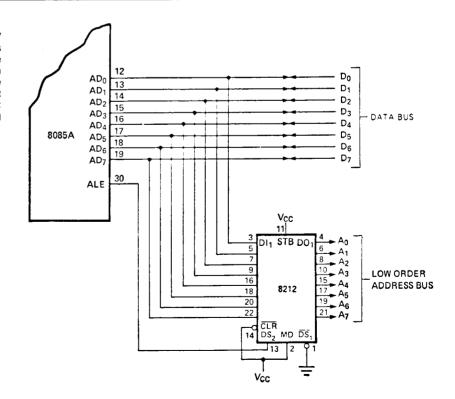

- 3. Software compatibility and availability Building the hardware of a microcomputer is only half the job. It must be programmed to perform useful work. Initially, the builder will by necessity hand code and assemble his own programs. Eventually, however, the need may arise for the computer to do a task requiring a very large program which cannot be easily hand assembled. The user must rely upon an assembler program in a larger machine. The assembler program would, of course, have to be compatible with the instruction set of the microcomputer.