# BESTOFPCW TEACH YOURSELF ASSEMBLER Z80

+X\*X+

长长长长长长大

Paul Overaa

\*\*\* \*\*=+ ? ADI

\*

Ι

) = l

\*1=

X # [

]÷≯÷;(

-++

XIII

# TEACH YOURSELF ASSEMBLER Z-80

**Paul Andreas Overaa**

**Century Communications London**

#### **ABOUT THIS BOOK**

Teach Yourself Assembler provides a clear approach to structured programming through the use of Warnier diagrams. The use of the Z-80 processor and its instruction set are discussed in sufficient detail to allow the novice to start programming. All the main structures of a program are illustrated extensively with Z-80 and BASIC listings. General approaches to problem solving and to the real-life application of programs are considered at the end of the book.

A detailed tabulation of all the major Z-80 op-codes and their functions completes the book.

#### **ABOUT THE AUTHOR**

Paul Andreas Overaa works for a company of consultant analytical chemists in London, England. He initially specialized in gas liquid chromatography, a branch of physical chemistry, and it was through this that he became involved with data reduction techniques and microprocessor programming. Much of his published work centres around the use of language independent design techniques.

He is a Fellow of the Institute of Analysts and Programmers and a Licentiate of the Institute of Data Processing Management. His spare time interests are varied and include pyschology, mathematics, music and Yoga.

#### ALSO AVAILABLE from Century Communications in association with *Personal Computer World* Three new books about assembly language programming:

*Teach Yourself Assembler: 6502* by Paul Overaa, a companion to this book based on this other very popular processor.

Assembler routines for the Z-80 and

Assembler routines for the 6502 by David Barrow, based on the very best of the long running PCW SUBSET series.

Copyright © Paul Andreas Overaa 1984

Based on material published in Personal Computer World magazine

All rights reserved

First published in Great Britain in 1984 by

Century Communications Limited 12-13 Greek Street, London, W1V 5LE

ISBN 0 7126 0549 5

Edited and produced working directly from the author's word-processor by NWL Editorial Services, Somerset, TA10 9DG

# CONTENTS

| Chapter   | 1          | <b>INTRODUCTION</b><br>An introduction to the book and to the approach<br>adopted throughout it                      | 1   |

|-----------|------------|----------------------------------------------------------------------------------------------------------------------|-----|

| Chapter   | 2          | WARNIER DIAGRAMS<br>An explanation of Warnier diagrams in relation to<br>program design                              | 7   |

| Chapter   | 3          | <b>ASSEMBLY LANGUAGE</b><br>A discussion of assembly language and of the facilities offered by modern assemblers     | 19  |

| Chapter   | 4          | <b>THE Z80 PROCESSOR</b><br>An examination of the classes of instructions available<br>for this processor            | 27  |

| Chapter   | 5          | <b>SEQUENCE AND REPETITION</b><br>Two of the basic building blocks of structured<br>programming                      | 37  |

| Chapter   | 6          | <b>ALTERNATION</b><br>The third basic building block of programming is<br>examined                                   | 47  |

| Chapter   | 7          | ADDRESSING<br>An explanation of addressing techniques                                                                | 59  |

| Chapter   | 8          | <b>REPRESENTING NUMBERS</b><br>A description of the different techniques used for<br>different types of numbers      | 79  |

| Chapter   | 9          | DATA STRUCTURES<br>An introduction to commonly used data structures                                                  | 93  |

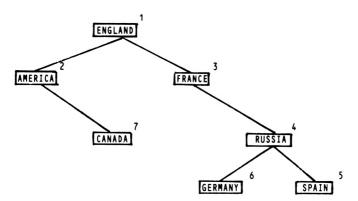

| Chapter I | 10         | SORTING AND SEARCHING 1<br>Some simple search techniques are examined before<br>looking at tree structures and sorts | 13  |

| Chapter I | 11         | <b>SOLVING YOUR PROBLEMS</b> A general approach to problem solving and program design                                | 139 |

| Chapter I | 12         | LINKING INTO BASIC<br>Two simple projects are described                                                              | 147 |

| Chapter I | 13         | WHERE TO GO FROM HERE<br>Where indeed?                                                                               | 157 |

| Appendix  | с <b>А</b> | The Z-80 Instruction set listing                                                                                     | 167 |

| Appendix  | с <b>В</b> | Assembler conventions                                                                                                | 221 |

| Appendix  | с <b>С</b> | The ASCII Character set                                                                                              | 223 |

| Appendix  | с <b>D</b> | The CP/M Operating system                                                                                            | 227 |

| Appendix  | с <b>Е</b> | Glossary                                                                                                             | 231 |

| Index     |            | 2                                                                                                                    | 236 |

|           |            |                                                                                                                      |     |

#### Understand the stillness that lies within you and be content to know that you are not alone

dedicated to

#### BOO

for very special help

# SOLVING PROBLEMS

There are so many methodologies scattered around under the heading 'structured approaches to problem solving', 'structured programming techniques', and so on, that we are apt to look on new ideas and thoughts about how we should program with a certain contempt. Frequently such contempt is justified because writers often re-hash the work of others – using little more than a different terminology to hide the fact. This book collects together some important ideas that have appeared over the last few years and attempts to illustrate how these ideas can give you a foothold into the world of assembly language programming. Emphasis is placed on how these newer techniques are evolving to form a self-consistent framework of ideas applicable to both high and low level programming.

Let us start by examining some very general points, closely related to the field of computer programming – they are concerned with how we think and how we solve problems.

# STRUCTURE, LOGIC AND CODE

It is generally accepted that the easiest way to learn about any new subject is to break it up into small manageable pieces. Each piece is then far less formidable and consequently far easier to get to grips with. Inherent in this idea is the implication that an ordered or 'structured' approach exists which enables our understanding of the lesser problems to be integrated into our understanding of the original more complex ideas and problems.

Once you have a computer (or access to one), instruction manuals and books explaining how to program your computer, and a certain amount of 'hands-on' experience, you will begin to feel ready to tackle larger problems – and this is when the difficulties arise. As often as not you find yourself searching through large amounts of coding in an attempt to locate a 'bug' which is preventing your program from working. If you are examining a program that you wrote some time ago the problem may be even more exasperating (especially if you did not document it properly). In even worse cases you find yourself trying to understand programs written by other people. You may well have come to the conclusion that either every programmer is a latent masochist – or that there must be a better approach to use. The emphasis towards 'structured programming' is an important step in the right direction but it is not in itself a complete solution. This is because a serious fundamental error is continually made by both professional and amateur programmers alike. The difficulty in programming a computer to solve a particular problem consists of two very distinctly different parts:

- The inherent logical basis of the problem

- Writing the code in the language of your choice

The confusion between these two problems is one of the reasons why so many people run into problems as they start to tackle larger projects. It is also one of the factors that can make the difference between being able to learn assembly language and giving up; this next paragraph offers the key to overcoming 99 percent of your programming difficulties:

• Any envisaged use of computers to solve a problem requires that you find a logically correct solution *before* you make any attempt to to actually code your computer solution – you should not try to solve the quite separate problems at the same time.

The problems associated with tackling each part in turn have, time and time again, been found far easier to deal with than the difficulties incurred by approaches not making this distinction. The isolation of a logical program design produces a logical solution that is portable i.e. is independent from the computer hardware and software on which it will be implemented.

From a practical viewpoint it is obviously advantageous to find ways of solving problems and designing logical solutions that can produce good, efficient, well structured programs in any language you care to name.

We are now going to examine three ideas related to how we solve problems, and to how we react to difficulties, and we shall see how the concept and use of the *Warnier diagram* can reduce many problems to the status of an open book. These ideas are unusual material for an assembly language book, but their relevance should not be underestimated: learning to program in assembly language is more difficult than high level language programming and it is useful to know a little about the way in which we think and how we react when things go less smoothly than we might wish.

# ENACTIVE, SYMBOLIC AND ICONIC MODELS

The way in which we approach a problem plays an important role in determining how successful or not our solution will be. In the last

twenty years much work has been done by psychologists to try to discover the basic mechanisms we use when we solve a problem, i.e. how we learn, how we conceptualize and abstract and in general what mechanisms we use to come to terms with our intellectual and physical environment.

Jerome Bruner has attempted to describe and characterize the ways in which young children react when confronted with a problem. He was able to identify three broad stages in the problem solving experience. The words used by Bruner – *Enactive*, *Iconic* and *Symbolic* – can be thought of as keywords for a basic problem solving framework. This framework is applicable to adult as well as children's patterns of thought.

- The *Enactive* stage relates to the use of physical models and the ability and confidence to manipulate them. One of the characteristics of this enactive level is the inability to describe the situation, i.e. the inability to communicate effectively without resorting to actual demonstration.

- The second, *Iconic*, stage describes the use of diagrams or pictures to represent the 'enactive elements' of the problem. This has been called the 'iconic' stage and is sometimes seen as the initial stage of abstraction, i.e. of separating the physical or real problem into a 'modelling situation'. Such a model will hopefully embody all the enactive elements of the problem in a form that is easier to translate into totally abstract form.

- The third, *Symbolic*, stage describes the use of signs and symbols, previously defined, to produce an abstract version of the problem. This characterizes the 'symbolic' level of confidence in problem solving.

Mathematics is typical of symbolic abstraction and it is commonly recognised that difficulties associated with learning and understanding mathematics frequently stems from a lack of confidence in symbol manipulation.

In children these stages can be identified by the way that simple problems are tackled. Of equal importance is how the approach changes as a child gets older: given a dozen bricks a very young child, if asked how many he would get if he had to share his bricks with two other children, will resort to physically (*enactively*) sharing the bricks. At a later stage he might solve such a problem by drawing three boxes and placing dots in them to represent bricks. He will be able to deduce from his *iconic* model that each child will receive four bricks. Later still in his development his confidence at the symbolic level will enable him to write ' $12 \div 3 = 4$ ' without hesitation – and to know that the answer produced symbolically is as valid as both the enactive and iconic results.

#### SOLVING PROBLEMS

In many situations these three levels of confidence occur simultaneously; they should not therefore be thought of as being physically distinct. The distinction to make is that the stages are conceptually different. We will often be able to look at particular lines of reasoning and identify problem areas as being 'symbolic' as opposed to 'iconic' (or whatever).

This framework is equally recognizable in adult thinking and the various levels of confidence can often be identified. A point that is important is that when we have difficulties in tackling a problem we frequently fall back to a lower level of problem representation in an attempt to achieve a better understanding.

As an example consider how many times you have been presented with a mathematical problem to solve in which you plunged straight in with some symbolic argument only to find you got 'stuck' and rapidly resorted to a graph or diagram – an 'iconic model' – in order to get a better understanding of the problem itself.

These ideas produce some interesting generalities which have implications of particular benefit to us in our quest for better methods of designing and writing computer programs.

Firstly, when you solve programming problems you are frequently solving other people's problems. You may very often need to explain your solutions and your lines of reasoning to others and there is a need to ensure proper communication of your ideas (often to non-technical people).

Secondly the problems you examine will often be ill defined or imprecisely defined. Frequently restrictions will be added to the problem whilst you are in the middle of finding a solution and the problem will change.

During all your programming you will regularly and inevitably encounter a number of quite severe difficulties. If you are working at a purely symbolic level you may conclude that some particular difficulty is insurmountable. Providing you have an 'iconic model' to fall back on you are more likely to come to terms with the new restraints.

The ways in which we describe a problem are important to us as we attempt to conceptualize and solve problems. The description is also important because of the ease or difficulty with which we can convey our ideas and thoughts to others.

## **WARNIER DIAGRAMS**

One of the techniques which capitalizes on the above ideas is the Warnier diagram. The power of using such diagrams to design programs is due in part to the separation of the logical from the practical difficulties. In addition to this the diagrams provide an iconic level with which to examine a problem.

The next chapter shows you what a Warnier diagram is and introduces you to the way it can be used to describe a computer program. We use these diagrams no matter what language we program in because they help to define and clarify the fundamental logical problems of the program design – regardless of the code which will be written to execute it. We hope that by the time you have finished this book you also will appreciate their usefulness, not only in relation to learning Z-80 assembly language but to programming and system design problems in general.

The ideas that have been discussed have implications not only in the field of programming but in thinking itself. In the Warnier diagram we have a technique which enables us to draw a picture of the logical structure of a problem. We can successively redefine our thoughts, change the problem, add or remove restrictions, all while maintaining a diagrammatic version of the current solution ready to be translated into any language we choose to use. Throughout this book vou will see Warnier representations of various problems and we hope you will, as we have done, realize that the work of Warnier goes far beyond the realms of programming and system design, he has in fact given us the techniques for analysing our thoughts and organizing the contents of our minds in a way that enables us to document those thoughts whilst we examine problems. We can illustrate our progress diagrammatically and use the diagrams produced to successively refine our ideas etc. The techniques actually help us think about the problems we examine.

If you are a newcomer to micro-computing then take heart. Although some of the ideas may take a certain amount of time to digest they are basically simple. Be patient and think about the concepts. Apply them to problems of your own choosing and you will achieve a real and useful understanding.

## The Z-80 PROCESSOR

We know from first hand experience that too much dependence on any particular processor often tends to result in the teaching of selected tricks based on the particular facilities that the processor provides. Whilst obviously it is important to use such techniques to utilize the available facilities of a particular processor, we feel that teaching underlying general principles is far more important.

We considered that the concept of working with a 'hypothetical processor' also leaves much to be desired. You only learn about assembly language programming by doing it and you can't easily run programs based around a hypothetical processor. We will use many of the concepts that you know about already from languages like BASIC, and re-apply them to assembly language – we will also try, as far as possible, to avoid involvement with the I/O problems of specific machines.

The 'chip' we have chosen to work with is the Zilog Z-80 microprocessor. This is used in the Sinclair ZX-81 computer, the Osborne-01 and many other popular computers. So if you want to step into the world of assembly language programming but have been worried about the difficulties then please join us now as we take our first steps.

# 2 warnier diagrams

A program design approach must satisfy several criteria; it must be able to produce results of consistently high quality, it must be rapid, it must allow for easy 'program maintainence', and it must be simple and straightforward to use. You will be pleased to hear that a technique already exists which – to a large extent – satisfies all of the above objectives.

The pioneering work of Jean Dominique Warnier (References 1 and 2) in France represents a major step forward in the design of logically structured programs. The use of the 'Warnier diagram' has been recently publicized in some of the works of Kenneth T. Orr (References 3 and 4) and others in the United States.

# SEPARATING OUT THE PROBLEM

Before looking in detail at the ideas involved it is important to emphasise that we are aiming to obtain solutions to problems that are completely independent of the computer or languages you use. Such factors will affect how you 'code' your solution, but they should not usually influence your logical solution to a design problem. The same techniques are applicable whether programs end up being coded in high level languages such as BASIC, PASCAL OT COBOL, OT coded in low level languages such as Z-80 assembly language. When you program in a high level language it is frequently possible to write short programs without explicitly designing your program. When programming with assembly language, the design stage becomes not just more important – it becomes vital. It provides a means of separating the *logical problems of design* from the *practical problems of coding* and by doing so enables you to tackle your programming in coherent stages.

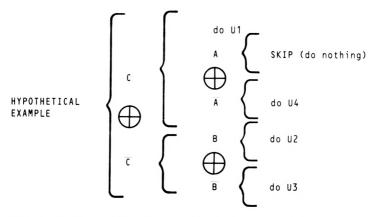

Essentially a Warnier diagram is a set of 'curly brackets', that defines particular groups of operations and the order in which they should be performed. The easiest way to show you about these diagrams is to take some examples.

#### WARNIER DIAGRAMS

# EXAMPLE A

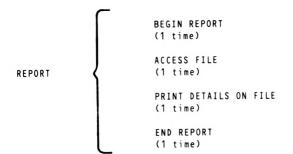

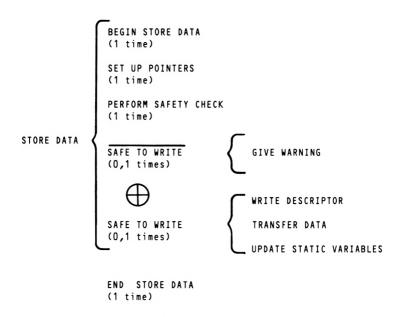

Imagine we wish to produce a report, consisting of details held on a computer file on disc or tape. The Warnier diagram of the basic problem is shown in figure 2.1.

# Figure 2.1: Warnier diagram of the essential characteristics of a simple report generator

The bracket is read from top to bottom and describes a procedure or group of operations that we have arbitrarily called REPORT. Underneath each item we have identified how many times the item is to be performed and, with this, our first diagram illustrates the essential features known about our problem.

Do we know anything more about our problem? Can we think of any information that could be relevant? Well, we know that:

• Computer files need to be *opened* before reading and *closed* once the read operation is complete.

These details could therefore be added to the diagram. To enable us to explain some further conventions used with Warnier diagrams let us first add a minor complication to the problem – let us suppose:

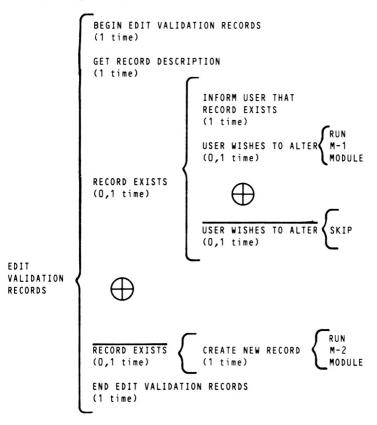

- The user wishes to access a file of his (or her) own choosing and to obtain a printed report of the details on the file.

- The specified file may not exist, and, if this is the case the user should be informed.

These changed or altered requirements can be represented by a more detailed Warnier diagram as we shall now show.

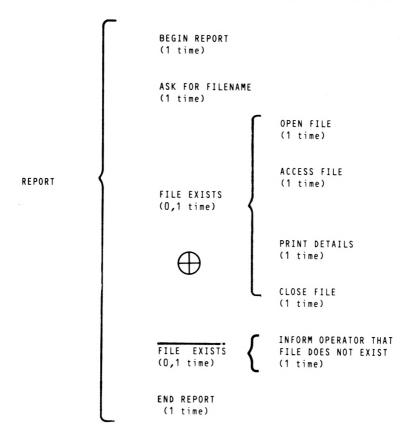

#### Figure 2.2: Some new restrictions added to Figure 2.1

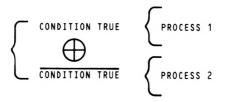

Figure 2.2 shows, in Warnier diagram form, the requirements of our problem as it is at the moment. We are using the convention that the logical opposite of a statement is written by placing a bar over it:

FILE EXISTS means FILE DOES NOT EXIST

We are also using a sign  $({}^{\circ}\oplus{}^{\circ})$  to separate mutually exclusive operations (sets of operations which will not occur together). In our example the file will either exist or it will not exist – so only one of these two operations would be performed at any one time. In some cases (where one of two or more alternatives exist) there will be sets of operations which may not be performed or which may be performed once, or many times. This is shown on the diagrams as (0,1 time), (0,N times), etc.

The conventions we have used so far are in fact the only ones you will need for the majority of problems that you will encounter. Let's collect them together for convenience:

- Brackets are used to define sets of operations.

- Brackets are read, and performed, downwards within any one 'level'. The item at the top of the bracket is performed first, the item at the bottom performed last.

- The logical opposite of a statement can be written as the original statement with a bar drawn over it.

- Brackets written to the right of a statement indicate the operations to be performed if *that statement is performed*.

- Underneath each item or statement we indicate the number of times the operations should be performed.

Using these conventions we can express in English exactly what figure 2.2 tells us; we are dealing with a certain procedure, called REPORT that starts by asking for the name of a file. If the file exists then it is opened, accessed, the details printed, and then the file is closed. If it does not exist then the operator is informed of the fact. Remember that if the file does exist then it is the group of actions (subset) shown to the right of the label FILE EXISTS that are performed.

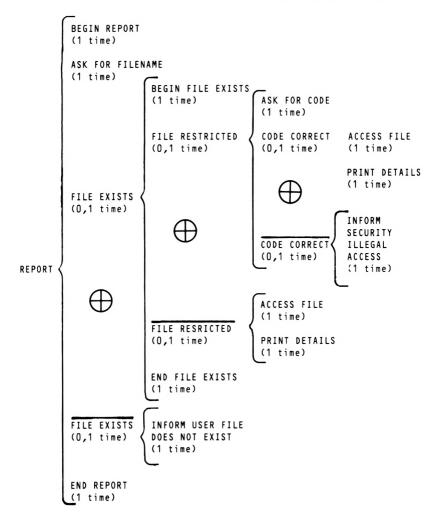

To appreciate the elegance and speed with which these diagrams can accommodate changing requirements let us place some further restrictions on our problem: within our 'hypothetical system' are files containing sensitive data (personnel data, wages, medical records, etc.). Such data must be protected from unauthorised access and users are therefore issued with access code numbers, so that examination of sensitive files is restricted to those users with the proper authority. If unauthorised attempts to access this data are made the computer should inform those in charge of system security.

Let us first consider the new constraints in isolation. We need to check whether the file specified by the user is a restricted file, if it is we must ask for the user's code number. If the code is correct then we allow access, if not we inform the system security of an attempted illegal access.

# Figure 2.3: A hierarchy is forming within the revised problem

The diagram in figure 2.3 shows the Warnier form of our new requirements. Notice that as we redefine the problem and add more detailed restrictions we do not have to rearrange the complete diagram, as one frequently needs to with flowcharts, etc. All we do is superimpose the new details and restrictions on to the existing diagram structure. The diagram is actually growing as we successively modify and redefine the known details of the problem. Additionally the diagram is documenting and expressing the logical requirements of the problem in a way that will make the transition to a computer language equivalent remarkably simple.

The ability of the Warnier diagram to display, help formulate, and to grow with the changing logical requirements of a problem, as that problem is examined, is of great importance. Once the quite simple conventions have been learnt these diagrams can be read just like the written English equivalent but, unlike the written English form, a Warnier diagram contains within its deceptively simple notation, the complete solution to coding of the problem.

We will see several examples of how this is achieved in assembly language in later chapters but for now figure 2.4 gives an example using a 'pseudo BASIC' type of code to show the general idea. The secret of converting a Warnier diagram into a finished program lies in regarding each bracket involving more than one operation as a subroutine. There are certain exceptions to this general statement but these will become apparent during the course of the book.

```

PSEUDO-BASIC-REPORT-MODULE

* _____

INPUT NAME OF FILE

IF FILE EXISTS THEN GOSUB 'FILE EXISTS'

ELSE PRINT 'FILE DOES NOT EXIST'

RETURN TO CALLING PROGRAM

* _____

REM SUBROUTINE......FILE EXISTS

IF FILE IS RESTRICTED THE GOSUB 'RESTRICTED FILE'

ELSE GOSUB 'ACCESS'

RETURN

* _____

REM SUBROUTINE.....RESTRICTED FILE

INPUT SECURITY CODE

IF SECURITY CODE=CORRECT CODE THEN GOSUB 'ACCESS'

ELSE GOSUB 'ILLEGAL ACCESS'

RETURN

* _____

REM SUBROUTINE.....ILLEGAL ACCESS

WRITE TO I/A LOG FILE THE TIME OF ATTEMPT AND THE ACCESS CODE

PRINT 'THIS IS A RESTRICTED FILE - PLEASE MAKE NO FURTHER ATTEMPTS'

RETURN

* _____

REM SUBROUTINE.....ACCESS

THIS WOULD BE A ROUTINE TO ACCESS THE DATA IN THE FILE AND DISPLAY

ON TERMINAL OR PRINTER ETC.

RETURN

```

#### Figure 2.4: Pseudo-BASIC code for Example A

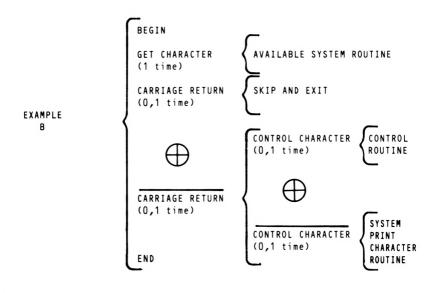

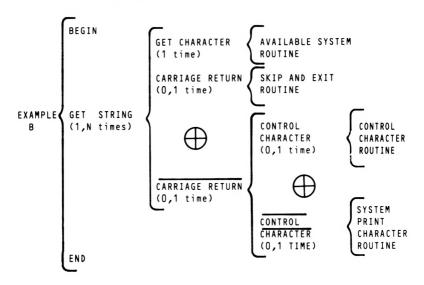

## **EXAMPLE B**

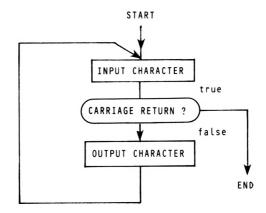

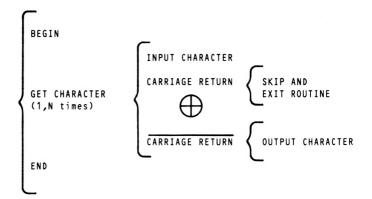

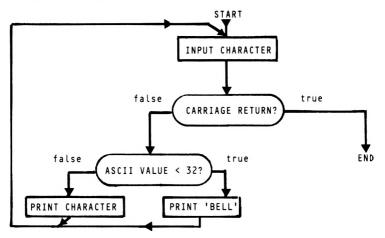

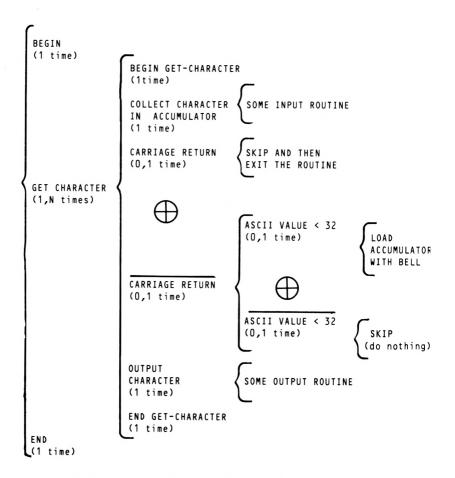

We wish to design the basic structure of a routine that collects characters from a keyboard device. If the character is a carriage return (i.e. ASCII 13) then we should leave the routine, if it is

WARNIER DIAGRAMS

another control character then an appropriate control character subroutine should be performed. If the character is not a control character then it should be passed to a printing routine to display it on a VDU or other output device.

Let us quantify what we know about the problem in terms of the sort of operations we may need to perform. We will have to input a character, possibly using an input routine available within the operating system. We must also make some type of check to see if it corresponds to a control character (note that for our purposes we shall regard a control character as one with an ASCII value of less than decimal 32). Additionally we will need some means of printing characters and again this may be a facility provided by the operating system. Let us draw a Warnier diagram to indicate the objectives we can recognize so far.

#### Figure 2.5: First Warnier diagram for Example B

Figure 2.5 shows our first attempt at describing the problem. The diagram implies that we can perform a test that will indicate whether a given input character is a carriage return or not, additionally it implies that we can test to see if a character is a control character or not. We should be fairly happy with this initial diagram because we know that all computer languages provide the type of testing we

would need to use. In the BASIC language we are, for example, able to use statements such as:

```

IF ASC(X$)=13 THEN ...

```

and

IF ASC(X\$)<32 ...

to perform the necessary tests.

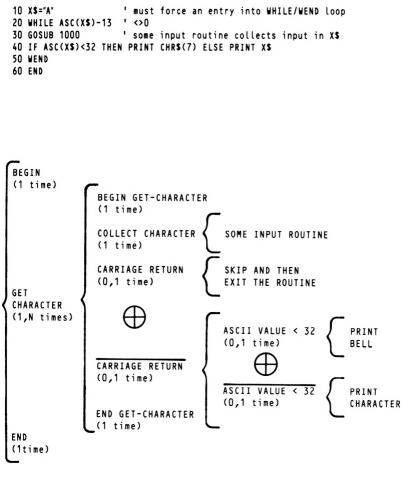

At present the Warnier diagram does not indicate that we collect anything more than one character by performing the illustrated operations. It is necessary in practice to perform the operations in figure 2.5 any number of times from 1 to N times, depending on when the user supplies a carriage return character.

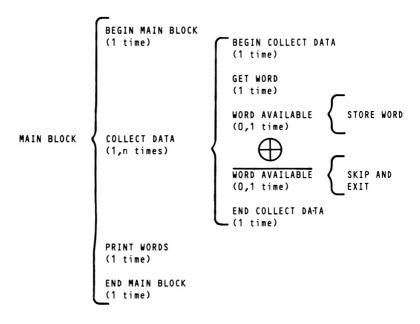

Figure 2.6: Expanded Warnier diagram for Example B

Figure 2.6 explicitly shows that we perform the operations indicated in figure 2.5 at least once, and up to a maximum of N times. The labels we use are, of course, arbitrary, but it is obviously advisable to use meaningful English expressions since this enables the diagrams to be easily understood.

We now have an accurate representation of the problem we are dealing with let's see how we can continue to redefine parts of the problem and expand the corresponding parts on the Warnier diagram. Let us suppose that the control characters detected are going to be used to perform the operations shown in figure 2.7. We will, on the basis of the ASCII value of the control character, perform *one* of the routines listed.

| ASCII code | <b>Operation to be performed</b>      |

|------------|---------------------------------------|

| 8          | Move cursor to Left                   |

| 16         | Move cursor to Right                  |

| 10         | Perform a Line Feed                   |

| 9          | Perform a Tab                         |

| 11         | Move cursor Down                      |

| 12         | Move cursor $Up$                      |

| OTHERS     | Take no action (i.e. ignore them all) |

#### Figure 2.7: Actions associated with the control characters

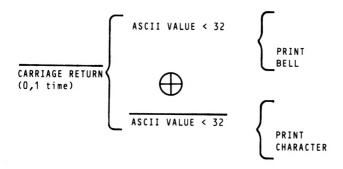

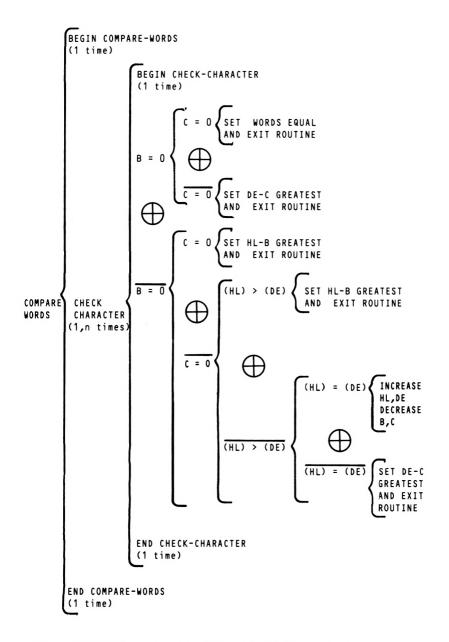

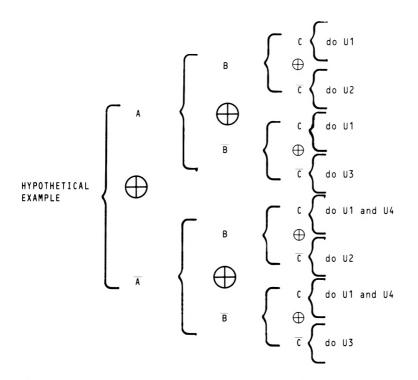

These operations are a more complex example of the mutually exclusive operation sets mentioned earlier. In such cases we cannot use the bar notation since many alternatives exist. Instead we show the options using their respective names and we use the  $\oplus$  sign to indicate that each 'operation subset' is mutually exclusive. Figure 2.8 shows how we represent this in Warnier diagram form.

|                         | C            | . (    |                         |

|-------------------------|--------------|--------|-------------------------|

|                         | ASCII CODE = | 8      | MOVE CURSOR TO LEFT     |

|                         | ASCII CODE = | 16     | MOVE CURSOR TO RIGHT    |

|                         | ASCII CODE = | 10     | PERFORM A LINE FEED     |

| CONTROL                 | ASCII CODE = | 9      | PERFORM A TAB           |

| CHARACTER<br>(0,1 time) | ASCII CODE = | 11     | MOVE CURSOR DOWN        |

|                         | ASCII CODE = | 12     | MOVE CURSOR UP          |

|                         | ASCII CODE = | OTHERS | TAKE NO ACTION - ignore |

#### Figure 2.8: Warnier expansion of the CONTROL CHARACTER statement

Let us now make an alteration to the control character's routine by creating some further assumptions. We suppose that if our hypothetical user presses a control key that serves no apparent purpose then either a simple error has been made (the user has pressed the wrong key) or the user is under the impression that the control key pressed serves some function which it does not, in fact, perform. In either case we may, from a practical point of view, decide to provide some means of informing our user that a 'useless' or 'unsupported' key has been pressed.

We may assume that the VDU screen has one or two lines available for comments and for programs to use when collecting responses such as input from the user. We also must assume that the remainder of the screen contains information that must be preserved, so we cannot simply print a menu of control character options on to the screen. What criteria can we identify?

- We will need space on the screen to display a menu and will therefore need to save the existing contents of the VDU screen somewhere.

- We will need to ascertain whether the 'user' actually needs a menu or whether he or she will quickly realize that a wrong key has been pressed by mistake.

We first consider the new restrictions as a discrete subset of operations, i.e. we concentrate on these new requirements. Once we have created a suitably structured diagram concerning the new constraints we can then superimpose it on the original diagram in figure 2.8.

```

INFORM USER 'KEY HAS NO FUNCTION'

(1 time)

ASK USER

'DO YOU WANT MENU Y/N?'

(1 time)

COLLECT REPLY

SYSTEM INPUT ROUTINE

(1 time)

SAVE CONTENTS OF SCREEN

DISPLAY MENU OF CONTROL OPTIONS

OTHER

USER WANTS MENU

INFORM USER

CHARACTERS

(0.1 time)

'Press any key to continue'

(0,1 time)

COLLECT INPUT CHARACTER

RESTORE CONTENTS OF SCREEN

USER

MENU

SKIP i.e. do nothing

(0,1 time)

```

Figure 2.9: New restraints added to Figure 2.8

WARNIER DIAGRAMS

The diagram in figure 2.9 shows our latest requirements in Warnier diagram form. Convince yourself that we have expressed the known additional details in a suitable manner, then look at figure 2.10 which shows the whole of the control character description including the current additions.

ASCII CODE = 8 MOVE CURSOR TO LEFT ASCII CODE = 16MOVE CURSOR TO RIGHT <del>(t</del> ASCII CODE = 10PERFORM A LINE FEED Æ ASCII CODE = PERFORM A TAB Ð ASCII CODE = 11MOVE CURSOR DOWN ASCII CODE = 12 MOVE CURSOR UP CONTROL CHARACTER (0,1 time INFORM USER 'KEY HAS NO FUNCTION' (1 time) ASK USER 'DO YOU WANT MENU Y/N?' (1 time) COLLECT REPLY SYSTEM INPUT ROUTINE (1 time) SAVE CONTENTS OF SCREEN DISPLAY MENU OF CONTROL OPTIONS USER WANTS MENU INFORM USER (0,1 time) 'Press any key to continue' OTHER ASCII COLLECT INPUT CHARACTER CODES **RESTORE CONTENTS OF SCREEN** USER WANTS MENU SKIP (0,1 time)

Figure 2.10: The final control character diagram

We could continue to expand other statements to provide further detailed analysis of the problem. As we do so we reach a point where it is possible to say 'Yes, the operations we are describing in the lower levels of the diagrams (the right-most levels) are easily capable of being coded directly in the language I have chosen to use!' In practice we reach this point sooner with high level languages than with assembly languages because more complex operations are supported. The relevant point to make is that the general principles are the same – the only difference is that when you analyse problems that will be coded in assembly language you will need to carry the analysis further.

### **FINAL WORD**

The ideas discussed in this chapter have implications not only in the field of programming, but in thinking itself. We have a technique that enables us to draw a picture of the logical structure of a problem. We can successively redefine our thoughts, change the problem, and add or remove restrictions whilst maintaining a diagrammatic version of the current solution which can be translated into any language we choose to use. During the book you will be given the choice of examining the Warnier representations of various problems and we hope you will, as we have done, realize that the work of Warnier goes far beyond the realms of programming and system design, he has in fact given us the techniques for analysing our thoughts and organizing the contents of our minds in a way that enables us to document those thoughts whilst we examine problems. We can illustrate our progress diagrammatically and use the diagrams produced to successively refine our ideas. In short the techniques actually help us think about the problems we examine.

Reference 1:

Warnier, Jean Dominique – Logical Construction of Programs (3rd Edition, translated by B.M. Flanagan) New York: Van Nostrand Reinhold Co. 1976

Reference 2: Warnier, Jean Dominique – Logical Construction of Systems New York: Van Nostrand Reinhold Co. 1981. ISBN 0-442-22556-3

Reference 3: Orr, Kenneth. T. – Structured Requirements Definition United States: Ken Orr and Associates, Inc. 1981. ISBN 0-9605884-0-X

Reference 4: Orr, Kenneth. T. – Structured Systems Development United States: Yourdon Inc. 1977. ISBN 0-917072-06-5

# 3 ASSEMBLY LANGUAGE

For many computer hobbyists, being able to write programs in an 'assembler language' is an ultimate goal. The mystique of writing such programs is reinforced by the frequent publication of listings written in strange and wonderful symbols reminiscent of ancient Babylonian . . .

Many writers try to explain the concepts behind these languages in a manner that subsequently reinforces the idea that assembly language programming is different, complex, and difficult to understand. The result is of course a foregone conclusion -a lot of people rapidly decide that assembly language programming is going to be far too difficult for them to learn.

We want to show you that a knowledge of assembler can be a very real asset to your repertoire of computing skills and that it can be learnt without having to throw away all those principles of good programming that you developed while using higher level languages such as BASIC OF PASCAL.

# WHAT IS AN ASSEMBLY LANGUAGE?

Is an assembly language the same as 'machine code'? Is it the language that the microprocessor understands? Are all assembly languages similar to each other? Let us take things right from the start and discuss exactly what an assembly language is.

A microprocessor is a sophisticated logic device able to perform a substantial number of predefined functions. These functions are determined by the design of the 'chip' itself. On their own these individual functions are neither complicated, nor in fact particularly useful, but when combined in an appropriate order then the microprocessor becomes an exceedingly powerful and versatile tool.

There are many different processors available and the *architectures* of the various chips (their internal design) vary quite considerably. Certain generalizations can however be made to enable you to appreciate the essential similarities from an overall point of view.

As well as the set of operations that it can perform, a microprocessor also has available a set of *internal registers*, places where it may store data and other regularly needed items. It will have some registers

#### ASSEMBLY LANGUAGE

assigned for specific functions and others of a more general nature. Instruction sets are designed not only to utilize the internal facilities that the chip itself provides, but also to allow the use of additional memory chips. In this way the microprocessor is able to transmit and receive information - it has the ability to *communicate* with other devices.

Unfortunately the language a microprocessor understands – the *machine language* – is that of *binary numbers*, it identifies the various functions that it can perform in relation to predefined patterns of zeros and ones. The Zilog Z-80 processor will interpret the binary number 11000011 as an instruction to perform a jump from its current memory location to a different memory location, whose position or *address* would, in practice, be provided by the two binary numbers immediately following the instruction. It is possible to program a computer using nothing but such codes – and there are even certain occasions when it is necessary!

Such programming is, however, prone to many problems such as transposition errors and the like. To a certain extent the problem can be eased by using a *hexadecimal* or an *octal* numbering system. The above example for the jump instruction of a Z-80 processor changes from 11000011 in binary to a simpler C3 in hex. Not exactly a mind shattering improvement, but it's definitely going in the right direction.

A program written in a hexadecimal form becomes immediately unrecognisable to the processor, so it is always necessary to *convert* any such program into a binary form before it can be recognized as a set of instructions.

Early on in the development of the computer it became apparent that to write even moderate size programs in binary, hexadecimal or octal form was about the best working definition of masochism that you would be likely to find. The concept therefore developed of creating a language that used the same operations but with each of them being given a simple (and comprehensible) name. It was in this manner that assembly language programming was born.

The word used to describe the instructions is *mnemonic* – pronounced nem-mon-ik – literally a *memory jogger* or aid to memory (we have always felt that the individual who selected the word *mnemonic* was having a private joke against the rest of society). The mnemonic for the Z-80 jump instruction used earlier is JP, which you'll surely agree is a useful improvement.

By writing a computer program in such a language, we are attempting to make it more comprehensible to ourselves. We do not however make it any more comprehensible to the poor computer, and so it is necessary to translate our mnemonics into the binary form that the computer will be able to interpret. It can be done by hand or a suitable computer program can do it for you. The name given to a computer program that performs this translation (or most of it) is an *Assembler*.

## **STANDARD MNEMONICS**

The choice of mnemonics to be used with a particular type of processor is in fact an arbitrary one. They are selected and recommended by the manufacturer of the chips themselves as an aid.

In the same way that different software houses write their BASIC interpreters and compilers around various 'standard' facilities but still end up producing versions of BASIC slightly different from each other, so manufacturers of microprocessors also design according to their own ideas and idiosyncrasies. Thus each type of microprocessor will have its own characteristics and methods of implementing the functions it provides. It will also have its own set of mnemonics. Such mnemonics are peculiar to the processor or the series of processors that a manufacturer produces and thus the mnemonics that your computer will require will be dependent on the chip that your computer is designed around.

It would be perfectly possible, if you felt that the manufacturer had chosen their mnemonics unwisely, to devise your own set. You would however pay for such a privilege by having to either assemble your final programs by hand, or by having to write your own assembler. However, modern day assemblers also do far more for you than simply act as a mnemonic converter and we will look at some facilities provided later on.

## **PREPARING SOURCE CODE**

In general the source code – the text version of the program that you write – would be prepared using some form of text editor. The source code may temporarily be stored on tape, on diskette or it may simply remain in memory. If it is stored at all it is usually as a simple ASCII text file.

Some assemblers have a 'resident' editor present as part of the assembler package itself. One such example of this arrangement is the ZX.ASZMIC ROM which actually replaces the Sinclair ZX-81 operating system to provide a quite useful Z-80 assembly language programming environment. You use an editor part to prepare your program in source code form, then assemble the program afterwards.

Other assemblers are completely separate. With these, usually on larger computer systems, you use a separate text editor or word processor to produce your source code. In these cases the assembler is used quite separately to operate on the ASCII files created by the text editor.

# SYNTAX

Each assembler will have its own rules or *syntax* requirements, just as say BASIC and PASCAL have their own requirements. You need to be aware of what your assembler can cope with and to what extent, if any, you can deviate from those requirements.

Nowadays the average assembler will flag errors in much the same way as a BASIC interpreter does. Syntax and other common errors are checked for and identified. Most assemblers are, however, quite easily led astray. This being so, it is usually important to look at the first error that is shown very carefully since this one will often cause the assembler to mis-interpret succeeding statements, even though they are correct when considered in isolation.

#### Lines of an assembler listing

A line in an assembly language program can be divided into three regions or *fields*:

- A label field

- An instruction field

- A comments field

The first and last fields are optional. Your assembler will have fixed rules for identifying the individual fields and you will find these in the documentation provided with your assembler.

Here is an isolated line from an assembly language program:

| CHECK\$CHARACTER:         | CP CARRIAGE\$RETURN  | ;end of input?                             |

|---------------------------|----------------------|--------------------------------------------|

| Label field<br>(Optional) | Instruction<br>Field | T<br>Remark or comment field<br>(Optional) |

#### Inclusion of comments within the program

It is possible to include comments within an assembly language program to make it more understandable. In BASIC you will be familar with the use of REM statements. With these you can add remarks that are effectively ignored by the BASIC interpreter. Assemblers vary in how they identify a 'Remark', the standard assembler provided by most CP/M systems will ignore any line that starts with an asterisk '\*'. It will also ignore comments placed after a specified ';' delimiter character. Most BASICs have similar facilities for 'end of line' remarks. With a high level language you can often work out what a program does even if it has not been reasonably documented – the same is not true of assembly language. One of the fundamental problems with writing assembly language is that it *is* difficult to analyse. It is difficult because any inherent structure present in the routines is often not obvious unless you wrote the code and know what to look for.

Because of this you may often have problems when you examine other people's programs. If you start right from the very beginning by making the maximum use of internal remarks you will at least avoid creating additional problems for yourself. You may think that you fully understand a program at the time you write it. You probably will at the time but will you next week, next month, next year? Make the most of a lesson that most of us have learnt the hard way and don't take chances – document to the maximum extent that time (and your assembler) will permit.

• The importance of placing understandable comments within an assembly language program cannot be over-emphasised.

#### Labels

Most assemblers allow you to use long meaningful names for specific locations in memory. This means that instead of having to remember that location  $0A3F_{hex}$  is the start of some subroutine that checks characters collected from a keyboard, you can use a label CHECK\$CHARACTER in the label field of the first instruction of that subroutine. The assembler will add the label to its internal symbol table and you will then be able to use the label to reference that particular routine. (Some assemblers require that you place a delimiter character, often a colon, immediately after a label definition so that the assembler can distinguish it from the instruction field, as in CHECK:).

#### The EQUate Directive

Another facility provided by modern day assemblers is that of the equate directive. This enables names to be assigned to numeric values. The use of such labels does not affect the code that the assembler will finally produce, and since it is a function of the assembler, *not* of the processor, the equate directive is known as a *pseudo operation*. It is especially useful for defining many of the common ASCII characters.

By placing the following statements at the start of your assembly language program you cause the assembler to include these 'definitions' to its internal symbol table.

| CARRIAGE\$RETURN | EQU | 13 |

|------------------|-----|----|

| SPACE            | EQU | 32 |

By using such definitions you will make your programs more readable to yourself and to others.

#### Other pseudo-ops

In addition to the above aids, the assembler will provide pseudooperations that enable you to define specific areas of memory as reserved space, and to place certain constant values into the assembled program for you. You can, using a pseudo-op usually called an ORG directive (short for ORiGin), select whereabouts in memory your program is to start.

It is unwise to list and explain all the facilities available – for several reasons: firstly many functions will not make much sense until you have written some assembly language programs and, secondly, many of the functions are just icing on the cake and in the early stages their explanation simply causes undue confusion. We have given you the basic idea of what an assembly language is, of what an assembler actually *does* and of the type of help that modern assemblers can provide. We will add to this basic knowledge when it is appropriate.

# **OPERATING SYSTEMS**

Before a microprocessor can perform any useful function, it needs a means of getting its data, it needs somewhere to send the output it produces, it needs additional memory, and it needs some means of co-ordinating all these various items, so that things happen at the right time and at the right place.

Unfortunately these very essential needs turn out to be the most complicated and time consuming to program. It is necessary to be familiar with the computer hardware used (and its idiosyncrasies), and with the technical details of the computer's design.

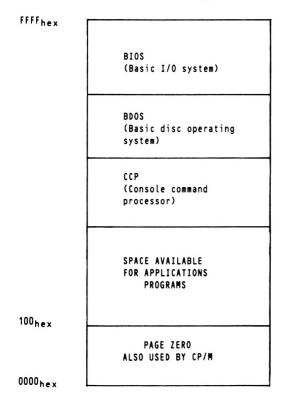

Routines which perform such functions are collectively known as the computer's *operating system*. It is neither necessary nor advisable for each manufacturer to design their own operating system and many micro manufacturers have realized the benefits of using widely available operating systems such as CP/M. These provide a quasi-standard environment within which to work. The object of such systems is to attempt to isolate you from the hardware-dependent nasties that present themselves when you start trying to get information to and from various devices. An operating system is to a large extent judged by its ability to isolate the problems of Input and Output (I/O) from a user.

There are unfortunately many different operating systems available. This is especially true of the smaller cassette-based home computers. With larger diskette based machines, CP/M provides a very welcome anchor point which isolates you from the worst of its insides through a protocol-based function *interface*.

Smaller machines, in general, do not achieve this type of isolation. They nevertheless usually provide accessible routines which may be used by your programs to simplify many operations. It is not possible to be familiar with all of the different operating systems that are available. We will therefore try, as much as possible, to avoid reference to specific computers. This means that you will, when the time arrives, have to delve into your own computer's manuals for certain of the details you will need. By the time we get to this stage though we will hopefully have given you sufficient grounding in the general principles for you to know what you will be looking for.

#### NOTES

# THE Z-80 PROCESSOR

The purpose of this chapter is to acquaint you with the various details about the Z-80 in order to help you build a mental picture of the processor. We can do this without having to delve into the world of electronics by using a simplified *logical model*. Many of the concepts we will discuss in this chapter are in fact applicable to many such models of other microprocessors.

We define a *register* as a place within a processor that can hold binary information. With 8-bit processors we talk of an 8-bit 'word length' and this is called a *byte*. The 8-bit registers in our processors can therefore hold one byte of information.

For our purposes a microprocessor can be regarded simply as a device that has a set of internal registers, some having specific uses, and a set of available instructions. The instructions enable data to be manipulated both within the processor and between it and the external memory.

Before a microprocessor can operate it is necessary for it to be able to access program instructions and data from either random access memory (RAM) or from read only memory (ROM). From a conceptual viewpoint we can regard this additional memory as a collection of 8-bit *memory locations*, each of which is identifiable by a specified unique *address*. With the 8-bit processors that we are using, we identify a particular memory location by specifying a 16-bit address so *two* bytes are required to specify a given location in the 0-64K range. Certain memory addressing instructions enable less than the full address to be given and this can have advantages in terms of speed of operation.

The descriptions that follow show, in a schematic form, the registers available in the Z-80 processor. The specific functions will be dealt with as we start to examine the instruction set and the facilities offered by the microprocessor. Since most processors have certain facilities and characteristics that are almost universal, it is useful to point these out while we look at our 'models' so that the overall general theme is apparent:

• All processors have a specialized register, called an Accumulator, used for arithmetic/Boolean functions.

#### THE Z-80 PROCESSOR

- All processors have a *Program Counter* register that tells the microprocessor from which memory location the next instruction should be retrieved.

- It is necessary for a processor to be able to store items such as subroutine return addresses and the Z-80 processor uses a very common software method based on a selected area in RAM memory. This area is called a *Stack* because items are added to it and taken from it in the same way as you would for example, take cards from and add them to the top of a pack of playing cards (on a last in-first out principle). Most processors have a *Stack Pointer* register that determines the memory location that is the current 'top' of the stack. Instructions that place items onto the stack is also available for storage of other items such as the temporary saving of the microprocessors internal registers (through inbuilt instructions). It is common practice to talk of the placing of data on the stack as '*pushing*' onto the stack, when items are removed the terms '*popping*' or '*pulling*' are used.

- A selected set of bits within the processor are affected by certain conditions that can occur. These bits, called *Flags*, are frequently grouped together for storage on the stack etc. and are often collectively termed a '*status word*' or 'program status word'. As an example, any arithmetic operation that results in zero being present in the accumulator, will set the zero flag to 1 (remember a bit can only take values of 0 or 1 and, by convention, 1 is chosen to represent the 'true' condition).

- Eight-bit processors usually provide some means of combining certain of their 8-bit registers so that a 16-bit (i.e.two bytes) *memory address* can be specified.

- As well as the above registers a microprocessor will provide others, some for specific purposes such as indexed addressing and interrupt handling. Others, sometimes called 'secondary registers' are of a more general nature and can be used as desired.

# LAYOUT OF THE Z-80 MICROPROCESSOR

The Z-80 processor is conceptually similar to an older microprocessor, the *Intel* 8080, but has much improved facilities. Twin sets of the main processing registers are available. Two 16-bit index registers are also present together with two specialized registers that will not concern us at present. A schematic description of the processor is shown in figure 4.1.

| Si<br>Fl             |                              |  | ero<br>lag |   | Half<br>Fl | Car<br>ag | ry            | Parity/Overflow<br>Flag | Subtract<br>Flag             | Carry<br>Flag |

|----------------------|------------------------------|--|------------|---|------------|-----------|---------------|-------------------------|------------------------------|---------------|

| flags as shown above |                              |  |            |   |            | bov       | <b>)</b><br>e |                         | ubtract flag<br>he processor |               |

| S                    | SZ * H * P/V N C ACCUMULATOR |  |            |   |            |           |               |                         |                              |               |

| В                    |                              |  |            |   |            | С         |               |                         |                              |               |

| D                    |                              |  |            |   |            | E         |               |                         |                              |               |

| Н                    |                              |  |            | L |            |           |               |                         |                              |               |

|                      |                              |  |            |   |            |           |               |                         |                              |               |

| Alternate Flag Set | ACCUMULATOR' |

|--------------------|--------------|

| в'                 | C '          |

| D '                | Ε'           |

| н'                 | L'           |

Alternate set is usually shown as a dash equivalent

| Interrupt Vector | Memory Refresh |

|------------------|----------------|

| IX 16-BIT INDEX  | REGISTER       |

| IY 16-BIT INDE)  | ( REGISTER     |

| SP 16-BIT STAC   | K POINTER      |

| PC 16-BIT PROG   | RAM COUNTER    |

Figure 4.1: Schematic layout of the Z-80 processor

# **HEXADECIMAL NUMBERS**

An 8-bit binary number can take values from 0 to 255 i.e. from  $0000000_{bin}$  to  $1111111_{bin}$ . It is often convenient to be able to express these values in a hexadecimal form which involves a 'base' of 16 rather than the 'base 2' binary form. The use of different bases sometimes causes problems so before you say: 'I was never taught about bases at school', we'll tell you that you are probably already using different bases almost every day of your life, possibly without realizing it. If you still weigh things in pounds and ounces, then you are already working in a hexadecimal based number system – only the notation is different.

With our 'normal' numbering system, base 10, we group by units of ten. When you add numbers together you add the units first, then remove multiples of ten and 'carry' these over to a 'tens' column. You do a similar operation with the 'tens' column and so on. The only reason that 10 is used as the base or 'radix' of our normal numbering system is that it is found convenient: we are, after all, born with ten fingers to count on.

When you have to add 'pounds and ounces' you proceed as follows: You add the ounces and if they come to more than 16 you 'carry' the number of multiples of 16 into the 'pounds' column:

```

2 lbs 14 ounces

+

2 lbs 5 ounces

------ and three units left over

5 lbs 3 ounces

```

If instead of using numbers from 0 to 15 for ounces we used 0, 1, 2, 3, 4, 5, 6, 7, 8, 9, A, B, C, D, E, F then we could write 2lbs 14 ounces as 2E ounces. It is this *extended numbering* system that forms the basis of the hexadecimal notation.

The extension of our basic number symbols (the digits 0 to 9), could have been done by adding any extra symbols, but since we already have an alphabet, the use of letters to represent our extra numbers was an obvious extension. So in just the same way that you learnt what the numbers 0 to 9 symbolize it is necessary to learn that  $A_{hex}$ represents 10 in 'ordinary' base 10 numbers. In computing applications it is common to write 'H' or 'hex' after a hexadecimal number to avoid confusion with decimal numbers.

If you now consider the eight bits of a byte of binary information as two groups of four bits you will appreciate that we can represent each of those two groups by a hexadecimal digit. Consider the binary number 10001111:

1000 Binary = 8 decimal = 8 hex 1111 Binary = 15 decimal = F hex

Thus 1000 1111 binary can be written very compactly as  $8F_{hex}$ . In a similar fashion we can represent two bytes (i.e. 16 bits of information), by using *four* hexadecimal digits.

1111 0000 1000 1111 binary can be split into four groups of four bits and written in hex form as  $F08F_{hex}$ . For specifying addresses – locations in memory – you will find the hexadecimal notation *very* convenient.

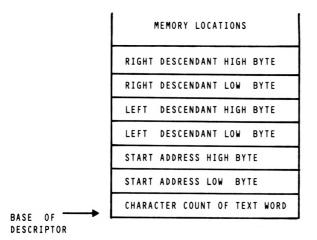

# PAGES OF MEMORY

We have already said that it is possible, with a two byte address, to specify any one memory location out of a total of 64K (i.e.  $64 \times 1024 = 65536$ ) such locations. Such an address can be written in hex form using four hexadecimal digits. An additional concept of dividing available memory into *pages*, each of 256 locations, has also proved useful. The first byte or 'high byte' of such an address is therefore often called the 'page number'. *Page zero* then refers to the initial 256 bytes of memory, whose addresses go from  $0000_{hex}$  to  $00FF_{hex}$ .

# **THE Z-80 INSTRUCTION TYPES**

There is no universal standard by which to group the various instructions that a microprocessor can execute. The following classification is a simplified version of the details commonly available from manufacturers and other sources.

#### Data transfer instructions

On the Z-80 these fall into various categories: 8-bit, 16-bit, block transfers and operations using the Z-80's stack.

#### 8-bit transfers

These are accomplished by the *load* instructions. These instructions are written in Z-80 assembly language as LD destination, source.

For example, to load the accumulator (designated as register A) from register C we use the instruction LD A, C.

Such transfers can be made between any two working registers: A, B, C, D, E, H or L. No direct instructions exist that enable values to be exchanged between the 'active' and the 'alternate' register set; when required, such transfers may be achieved by use of the stack or additional memory.

In order to load any register other than the accumulator from a memory location it is necessary to place the location address into the HL register pair. HL thus points to the location to be used as the source. The notation (HL) signifies that it is the *contents* of the byte addressed by HL that is involved in the transfer. Thus LD C, (HL) will load the C register with the contents of the byte whose address is contained in HL.

Similarly to store the contents of register C at the location whose address in in HL we would use the instruction LD (HL), C.

The accumulator is the only register that can store data directly to, and load data directly from, a memory location. LD A, (OFFFH) will

#### THE Z-80 PROCESSOR

load the accumulator with the contents of the byte whose address is  $OFFF_{hex}$ . Similarly LD (OFFFH), A will transfer the contents of the accumulator directly to the specified memory location.

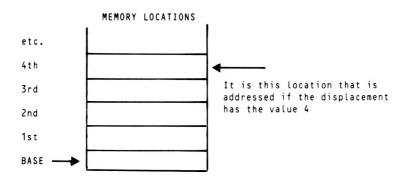

Data can also be loaded from a byte that follows the op code byte. eg. LD B, 0FH will load the B register with the value 15, i.e. 0F hex. This is termed immediate addressing and is explained later.

Other possibilities including loading using indexed addressing are available and the instruction set listing covers these in detail.

#### 16-bit transfers

Any of the register pairs BC, DE, HL, SP, IX or IY may be stored at, or loaded from, a specified pair of memory locations. They may also be loaded with a 16-bit value contained in the two bytes following the instruction. Additionally BC, DE, HL, IX, or IY may also be transferred to, or loaded from, the top of the stack (whose address is kept in the stack pointer or SP register). The accumulator and the flag status are also treated as a 16-bit register that can be transferred to and retrieved from the stack. Miscellaneous other instructions exist that perform 16-bit transfers.

#### EXAMPLES

#### PUSH DE

This decreases the stack pointer then pushes the contents of the D register onto the stack. The stack pointer is again decreased before the contents of the E register are placed on the stack – note that the stack is growing downward in memory as items are added.

#### POP DE

This performs the reverse operations to the PUSH instruction described above.

LD BC, 10FCH This loads the BC register pair with the 16-bit value  $10FC_{hex}$ .

#### **Block transfer instructions**

The Z-80 has some quite powerful, and extremely useful, block transfer instructions. All of these instructions use three sets of registers namely BC, DE and HL. The BC pair are used as a 16-bit counter which specifies the number of bytes involved in the transfer. HL is used to point to the source, and DE used to point to the destination. The instructions have the mnemonics LDD, LDDR, LDI, LDIR and their operation is explained in the instruction set listing.

#### Data processing instructions

Various addition and subtraction instructions exist, both with and without carry. ADD A, B for example will add the contents of the B register to the accumulator. The instruction ADC A, B will also add the contents of the B register to the accumulator but if the carry flag is set this will also be added into the result. In both cases the result is stored into the accumulator and thus overwrites the original accumulator contents.

Several logical instructions, AND, OR and XOR (eXclusive OR) are available together with instructions that enable 8-bit data values to be compared, rotated and shifted in various ways. Details are provided within the instruction set listing and examples of their use will be found in the text.

#### **Conditional test instructions**

Many of the instructions available on the Z-80 will use particular flag conditions as a criteria for execution. These include the *conditional jump*, *conditional branch* and the *conditional call* instructions. As an example the instruction CALL Z, INPUT\$ROUTINE will call a subroutine whose address is defined by the label INPUT\$ROUTINE only if the zero flag is set. If the zero flag is not set then the subroutine will not be called.

#### **Miscellaneous instructions**

Numerous other instructions exist that are used for *input and output*, *interrupt* servicing, forcing particular *flag* conditions, switching between *alternative register sets*, and so on. Certain instructions have been deliberately excluded from our simplified listing and in such cases you are referred to the manufacturers data or other sources.

No Z-80 book would be complete without a mention of the extensive 'bit manipulation' instructions that are available. The three instructions BIT, RES (RESet bit), and SET enable individual bits of a register, an indirectly addressed byte, or an indexed addressed byte to be tested, reset or set as required. We have avoided using such instructions because they are not generally available on other microprocessors; you should, however, be aware that they do exist and are often useful.

# EXAMPLES

BIT 4, A Test bit 4 of the accumulator and set zero flag accordingly. SET 2, (IX+d)Set bit 2 of the indexed addressed byte (IX+d). RES 5, (HL)Reset bit 5 of the indirectly addressed byte (HL).

We have not attempted to cover the uses of all of the Z-80 instructions that exist. The main area not covered relates to those instructions used in operating system programming, these include the use of interrupts (which are essentially hardware generated subroutine calls) and the port input/output instructions. Such material is not particularly relevant for our purposes and in the early stages can be quite easily remain 'hidden' behind the operating system that your computer uses.

# **INSTRUCTION FORMAT**

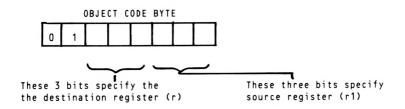

Instructions on the Z-80 can consist of between one and four bytes. In general the instructions with the shortest length execute the most quickly.

#### Single byte instructions

One example is the load instruction LD A, C. As mentioned above this will load the contents of the C register into the accumulator. When assembled, a single byte is produced, which has the value  $79_{hex}$ . This byte of 'object code' that is produced is the numerical equivalent of this particular assembly language instruction. It is called the *op-code* for the instruction.

#### Two byte instructions

A typical example is the instruction LD C, 0FH which will load the C register with the value  $0F_{hex}$ . When assembled two bytes of object code are produced. The first byte is  $0E_{hex}$ , which is the op-code for the instruction, the second byte contains the value 0F hex, the value specified in the instruction.

#### Three byte instructions

The 16-bit equivalent of the load instruction shown above is LD BC, 1F20H which loads the BC pair with the 16-bit value shown. Assembly of this instruction produces one op-code byte followed by two bytes that hold the value  $1F20_{hex}$ . Other examples include instructions that involve specifying 16-bit addresses, eg. LD A, (0F21H) which is assembled to produce the op-code byte, followed by the low order part of the address  $(21_{hex})$  followed by the high order part  $(0F_{hex})$ .

#### Four byte instructions

Some instructions, namely those involving the indexed registers or indexing, can require four bytes. One example is the instruction LD (IX+d), n which loads the byte whose address is found from the contents of the index register IX plus a displacement 'd' with the value specified by the letter n. Once assembled the instruction produces the following object code bytes:

- A two byte op-code, DD<sub>hex</sub> and 36<sub>hex</sub>

- A single byte containing the value of the displacement

- The specified data value 'n'

#### **THE Z-80 INSTRUCTION SET**

Appendix A lists the Z-80 instruction set in mnemonic form, giving a description of each operation together with details of its effect on the flags, a listing of the object codes generated and miscellaneous other information.

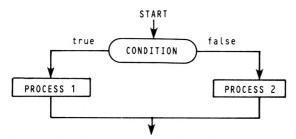

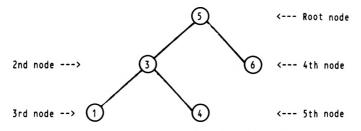

One of the observations that led to the concept of structured programming was the discovery that virtually all problems may be solved by using a combination of the three basic structures: *Sequence*, *Repetition* and *Alternation*.

The term *sequence* simply means doing things in a serial order. We can illustrate this in a flowchart form as shown in figure 5.1:

# Figure 5.1: Sequence in flowchart form

The equivalent Warnier diagram is shown in figure 5.2:

```

operation 1

operation 2

operation 3

```

#### Figure 5.2: Sequence in Warnier diagram form

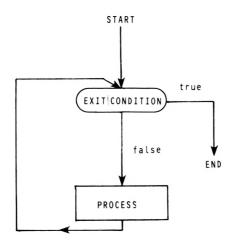

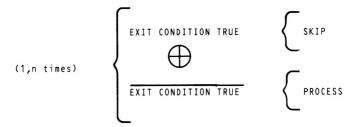

Repetition concerns itself with performing a set of actions a given number of times. Program *loops* such as BASIC'S 'FOR .. NEXT', 'DO .. UNTIL' and 'WHILE .. WEND' are typical examples of this type of structure. Two forms are possible, depending on whether we are testing the exit condition *before* (pre-test) or *after* (post-test) performing the required processing. Figures 5.3 and 5.4 show how we can use flowchart and Warnier representations to illustrate repetition.

Figure 5.3: Pre-test Repetition Flowchart form

#### Figure 5.4: Pre-test Repetition Warnier diagram form

The description of alternation will be left until the next chapter when we shall examine it in detail.

#### **REPETITION – An example program**

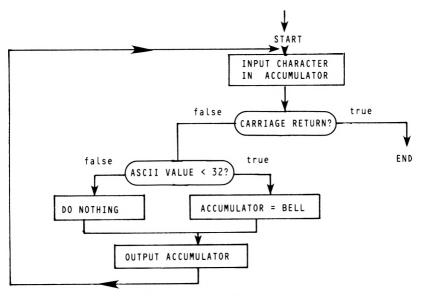

As an illustration of repetition, we have chosen a simple program to collect characters directly from the keyboard, and to print them on the VDU screen. There are many ways such a program could be written using BASIC. We have chosen one particular representation that will let us compare the assembly language equivalents very easily.

The BASIC program can be divided into three parts. An initial or 'Setup' block, whose main task is to define a variable called CARRIAGE.RETURNS as the string equivalent of the ASCII 13 'Carriage Return' code. An 'end' block, which in our example is nothing more than a single END BASIC statement. The bulk of the program is labelled the 'main' block and performs the following functions: We collect a character, using the INPUTS() function; we then check to see if it is a carriage return character, if it is we jump to the end of the program, otherwise we print the character and jump back to the input statement in line 30 for the next character. Here is the BASIC form:

| * =====      | ===== |                                                        |  |  |

|--------------|-------|--------------------------------------------------------|--|--|

| SETUP        | 10    | CLEAR                                                  |  |  |

| BLOCK        | 20    | CARRIAGE.RETURN\$=CHR\$(13)                            |  |  |

|              | 30    | X\$=INPUT\$(1) 'collect character in X\$               |  |  |

| MAIN         | 40    | IF X\$=CARRIAGE.RETURN\$ THEN 70 'end of input if true |  |  |

| BLOCK        | 50    | PRINT X\$;: 'output character to VDU                   |  |  |

|              | 60    | GOTO 30 'get next character                            |  |  |

| END<br>Block | 70    | END                                                    |  |  |

| *            |       |                                                        |  |  |

When we write an equivalent program in assembly language we use the same type of program structure. The 'Setup' block will, however, vary according to your assembler, and your operating system. We give a typical example of the type of coding that could be expected.

#### **Z-80 mnemonics for SETUP BLOCK**

| CARRIAGE\$RETURN | EQU | 13       |

|------------------|-----|----------|

|                  | ORG | 100H     |

|                  | JP  | STACK    |

|                  | ORG | 150H     |

| STACK:           | LD  | SP, \$-2 |

|                  |     |          |

# **OPERATIONS USED**

- Define CARRIAGE\$RETURN so that the assembler will recognize this term as meaning the number 13.

- Define whereabouts in memory your program is to start. Our assemblers use ORG (short for ORiGin) and in the above example the program starts at 100<sub>hex</sub>.

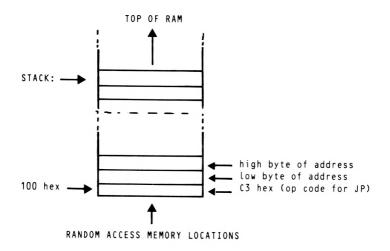

- We perform an *unconditional jump* to an address that is labelled STACK. This is the first real assembly language instruction we have encountered. This type of jump is called an *unconditional* jump because it is performed irrespective of any processor flag conditions. The mnemonic JP represents the start of a three byte instruction. The first byte is the 'op code', i.e. the numerical representation of the mnemonic, the second and third bytes are

#### SEQUENCE and REPETITION

the required jump address. A schematic description is shown in figure 5.5.

# Figure 5.5: Schematic representation of a 'Jump' instruction

• The microprocessor performs this jump by placing the address following the op code into the program counter register. The program counter is called the destination register for the information transfer. The information source is the two bytes that immediately follow the op code.

In general the term 'addressing' refers to the specification, within an instruction, of the location of the 'operand' – the byte(s) upon which the instruction will operate.

Since the operand for the JP instruction is the two immediate data bytes that follow the op code the addressing mode being used to execute the instruction JP is called 'immediate'.