# Amstrad CPC 464

Melbourne House

# The Ins & Outs of the

Don Thomasson

# **Don Thomasson**

# MELBOURNE HOUSE PUBLISHERS

#### © 1984 Don Thomasson

All rights reserved. This book is copyright and no part may be copied or stored by electromagnetic, electronic, photographic, mechanical or any other means whatsoever except as provided by national law. All enquiries should be addressed to the publishers:

IN THE UNITED KINGDOM — Melbourne House (Publishers) Ltd Castle Yard House Castle Yard Richmond, TW10 6TF

IN THE UNITED STATES OF AMERICA — Melbourne House Software Inc. 347 Reedwood Drive Nashville TN 37217

IN AUSTRALIA — Melbourne House (Australia) Pty Ltd 2nd Floor, 70 Park Street South Melbourne, Victoria 3205

#### ISBN 0 86161 190 X

Edition: 7 6 5 4 3 2 1 Printing: F E D C B A 9 8 7 6 5 4 3 2 1 Year: 90 89 88 87 86 85 84

# CONTENTS

Introduction . . . VII

The Ins . . . IX

System Overview ... 1 The Memory System ... 4 The Inner Peripherals ... 11 The I/O Address Map ... 11 The Video Gate Array ... 13 The CRT Controller ... 14 The Parallel Peripheral Interface ... 18 The Printer Port ... 21 The Outer Peripherals ... 23 The Programmable Sound Generator ... 23 The Keyboard ... 26 The Cassette Recorder ... 27

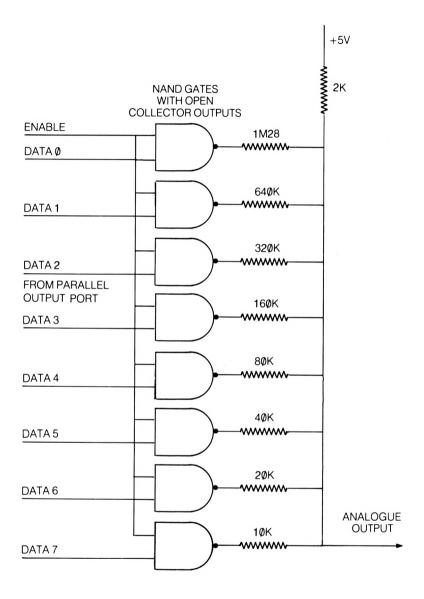

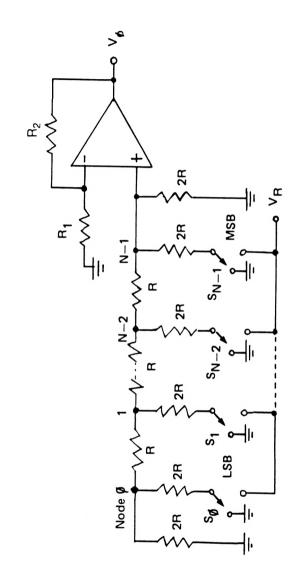

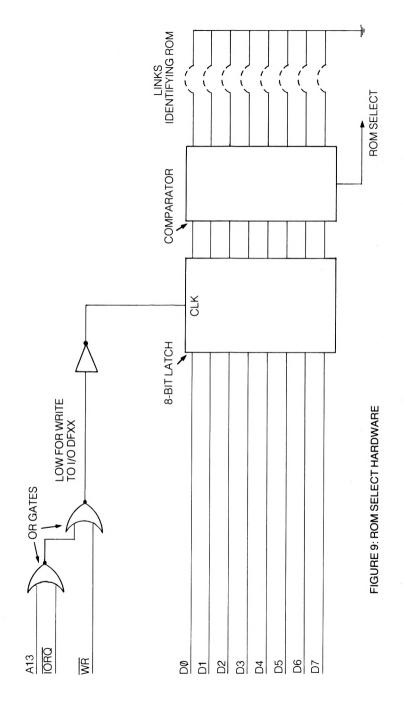

The Operating System . . . 29 The RST Area ... 31 Jumpblock Entries . . . 34 Interrupts and Events . . . 34 Operating System Calls . . . 37 The Interface . . . 85 The Outs . . . 89 General Principles . . . 91 Parallel Interfaces . . . 93 Interface Rules . . . 93 Alternative Printer Port . . . 96 Software Support . . . 98 Communicating Computers ... 101 Serial Interfaces . . . 103 Analogue Interfaces . . . 105 Sideways ROMs . . . 108 ROM Types and Formats . . . 109 Applications ... 112 External ROM Hardware . . . 113 A Second Processor ... 113

Overview . . . 116

# INTRODUCTION

The greater part of an iceberg lies hidden, accessible only to those who have suitable equipment. Much the same could be said of the capabilities of the AMSTRAD CPC464. Superficially it may appear to be just another games-playing machine. However there is a lot more to it than that. As with the iceberg, special equipment is needed to explore the system capabilities in full, and the object of this book is to provide such equipment.

Even at first glance, it is clear that the CPC464 is a little out of the ordinary. That it has a built-in cassette recorder is by no means unique, although the provision of a monochrome or colour monitor, incorporating the system power supply, is a welcome change, and other features are useful, if less obviously so.

For those who confine themselves to BASIC, the friendliness of the machine will be sufficient to recommend it, but for the 'hacker', the user who wants to delve deeper into the mysteries of the system, there is much to be explored. Here we are mainly concerned with the way in which the CPC464 will work with external equipment. To deal with that effectively, we must first study and understand the internal system, for that determines how add-on bits and pieces can be controlled.

The book is therefore divided into two main parts, the 'Ins' dealing with the internal system, and the 'Outs' dealing with external additions.

It is inevitable that frequent reference will have to be made to machine code routines. Those who need additional data on this subject will find **Programming the Z80** a useful aid. It is listed in the Bibliography at the end of the book.

It should be said that the book is based on the cassette system version of the CPC464, and some points may be modified in the disc system version.

# The Ins

# THE INS

## **System Overview**

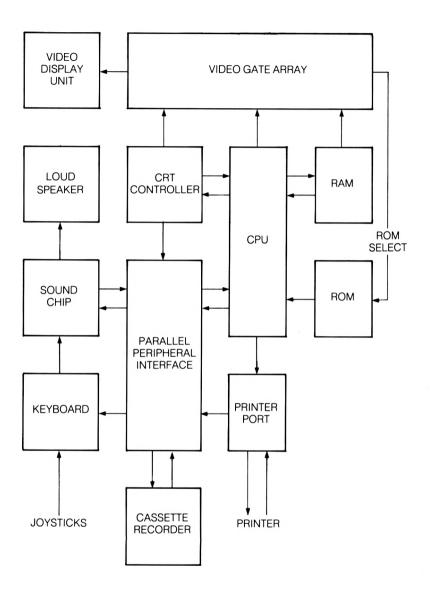

The general arrangement of the internal hardware of the CPC464 is shown in Fig. 1. Note the directional arrows indicating the flow of data or control information. They are important.

The Z80 sits at the centre of the system, and it controls directly or indirectly — everything that the system does. It communicates on a two-way basis with 64K of RAM, and on a readonly basis with 32K of ROM, which is addressed in two 16K blocks. Selection of ROM or RAM, at an address where both exist, is controlled by signals from the Video Gate Array.

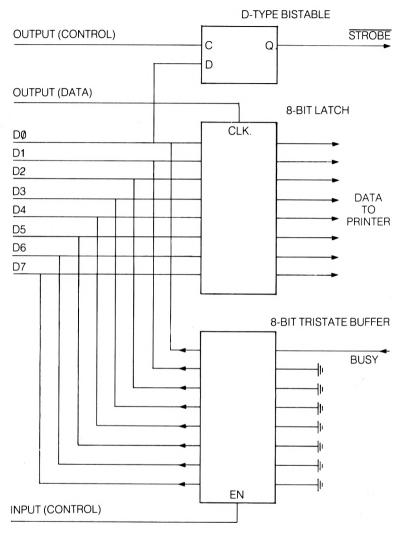

Through its I/O interface, the CPU communicates directly with the CRT Controller, which works with the Video Gate Array to maintain the display; with the PPI (Parallel Peripheral Interface); and with the Printer Port. This is the primary peripheral area.

#### FIGURE 1: INTERNAL HARDWARE SYSTEM

Outside that, in system terms, lies the secondary peripheral area. This has no direct contact with the CPU, but communicates with the primary peripheral area. The elements in this outer area include the cassette recorder, which communicates with the PPI, the keyboard, and the sound chip. The latter contains a pair of data ports, one of which is used to communicate with the keyboard output.

The Z80 CPU is driven by a 4 MHz clock, but in order to interlace the memory accesses for the processor and display system it is necessary to delay processor accesses, effectively reducing the clock to 3.3 MHz.

The overall system is remarkably economical, in hardware terms, and you may wonder how it can compete in performance with systems that have three times as many components. The answer lies largely in the system firmware, which is more thoroughly organised than usual, and which displays some interesting ingenuities. True, the bigger system can do things that the CPC464 cannot, but many of these can be added as externals, which means that you only pay for the ones you want. Many users will see such facilities as unnecessary frills, while wanting features beyond the scope of either machine.

The system programs are divided into nine groups:

#### a. Key Manager

Scans the keyboard, generates characters, implements the function key expansions, tests for break, scans joysticks.

#### b. Text VDU

Puts characters on the screen, handles the cursor, and responds to control codes.

#### c. Graphics VDU

Plots and tests points, draws lines.

#### d. Screen Pack

Interfaces b. and c. to the screen hardware and executes common screen functions.

#### e. Sound Manager

Deals with sound generation.

#### f. Cassette Manager

Deals with cassette functions.

#### g. Kernel

The heart of the operating system, handling interrupts, events, ROM selection and program execution.

#### h. Machine Pack

Handles printer and general hardware control.

#### i. Jumper

Controls access to routines via jumpblocks.

This covers the operating system, mainly held in the lower ROM. The BASIC interpreter, if used, is held in the upper ROM, but can be replaced by alternative programs in external ROMs.

Access to the system routines should be via the nominated 'jumpblocks', which are tables of jumps giving access to the various entry points. These tables will remain unaltered in any future version of the system, but the direct access points may change.

# **The Memory System**

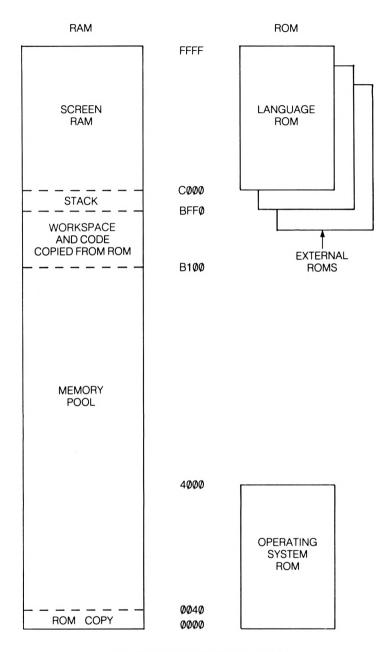

Fig 2 shows the memory map in outline, but there is a lot of fine detail which cannot be shown in that way. (Note that all memory addresses are given in hexadecimal form.)

The overlap of ROM and RAM in the top and bottom quarters of the map is a salient feature. Since bank-switching schemes have run into problems in the past, the implications of this must be examined carefully.

All memory writes go to RAM. It's no use writing to ROM. It doesn't answer . . .

If a ROM is disabled, a memory read draws on the RAM in that area. Either or both of the ROM blocks can be enabled independently, in which case they supply the data for appropriate read addresses.

The two ROM areas are in fact implemented by a single component, a 32K ROM, the address lines of which are fiddled as follows:

If address lines A14 and A15 are both false, address bit A14 to the ROM is false, and the lower ROM (0000-3FFF) is addressed if it is enabled.

If address lines A14 and A15 are both true, address bit A14 to the ROM is true, and the upper ROM (C000-FFFF) is addressed if it is enabled.

If the states of address lines A14 and A15 differ, ROM is inactive.

The ROM enable lines come from the Video Gate Array, which must be able to gain access to the screen memory between CPU memory accesses. The relevant data is output to the Video Gate Array directly, in bits 2 (lower ROM) and 3 (upper ROM) of a control word. However, it will be seen that direct access is both unwise and unnecessary. The other bits of the control word have important meanings, and must be maintained in the correct state.

The RAM is implemented by eight  $64K \times 1$  components.

Turning to fine detail of memory use, the ØØØØ-ØØ3F area holds the same data in ROM and RAM, the latter copied from ROM during the initialisation process. This is necessary as the Z80 RST instructions jump into this area, and must find code available, whether the lower ROM is enabled or not. A number of other short routines are packed into the same region, and they must also be available in both ROM and RAM. We will see later that certain of the RAM locations in this area can be changed by the user for particular purposes, but this must be done with care, adhering to strict rules.

From ØØ4Ø upwards, ROM and RAM diverge, the ROM containing operating system routines, while the RAM holds workspace data. BASIC sets its stored program from Ø17Ø upwards, for example.

The cental area of RAM is known as the Memory Pool. Only that part from 4000 to C000 can be guaranteed to be available for immediate access. It would be foolish, for example, to position the machine stack outside that area. It normally sits very comfortably from BFFF downwards.

The upper part of the central area contains system variables and more program that must always be accessible. In the extreme, the block from A400 up to the stack may be occupied, if SYMBOL AFTER Ø has been called to copy all character patterns to RAM. If the 'soft' patterns remain at the standard level (From &FØ to &FF), AB40 is the first location occupied.

Much of the area above AB40 is taken up by 'jumpblocks', which provide standard entries to many important routines. The entry addresses to the routines may change, but the jumpblock allocations will remain unaltered. This is important: It is wise to make use of the jumpblock path, even when the actual access point is known, because programs will then work with later marks of operating system.

From CØØØ upwards, the RAM serves the screen, and ROM implements the BASIC interpreter (Though some interpreter routines are in the lower ROM). External ROMs may replace the BASIC ROM, providing other 'language' implementations.

This rapid tour of the memory should have revealed the general pattern. No doubt it has encouraged thoughts of a more detailed examination, in which case you may feel that the following program would serve your purpose:

```

100 CLS

110 INPUT "Start Address"; A

120 A=A-65536*(A<0)

130 N%=A-8*INT(A/8)

140 PRINT HEX$(A,4);

150 B=PEEK(A)

160 PRINT TAB(6+3*N%);HEX$(E,2)

170 A = A + 1

180 N%=N%+1

190 IF N% < 8 THEN 150

200 N%=0

210 PRINT

220 GOTO 140</pre>

```

Line 120 is needed because input of a hexadecimal address above 7FFF makes A negative, and in that event 65536 must be added to give a positive value, or subsequent calculations will give trouble. The variable N% puts the dumped values in the correct column of the display, and starts a new line as appropriate.

But the results of running this program are disappointing. Acres of zeroes are seen, with a limited amount of code here and there. We are looking at RAM, because PEEK and POKE only access RAM, ignoring ROM. Oh, dear! We need a different approach.

Scanning the bulky Firmware Manual, we discover the following calls, which will solve our problem:

B900: Enable upper ROM B903: Disable upper ROM B906: Enable lower ROM

B909: Disable lower ROM

For these four calls there are no entry conditions, but the previous ROM status is returned in the A register. Flags are cor-

rupt, but other registers are unaltered. The value returned in A can be used to restore the Previous ROM state by use of:

B9ØC: Restore ROM state defined by contents of A register. The return is with AF corrupt, but other registers are unaltered.

Conscience compels an admission that the statement that other registers are unaltered is not entirely correct. Alternative register C' is changed, because it holds the updated state of the data sent to the Video Gate Array. However, you are required not to use the alternative registers, since they hold vital information that may be needed at any moment.

Leave the program above set up, and overwrite it with the following entries:

```

90 GOSUB 400

150 GOSUB 300

300 Q=INT(A/256)

310 POKE &7019.Q

320 POKE &7018. (A-256*Q)

330 CALL '& 7000

340 B=PEEK(&7020)

350 RETURN

400 FOR X=&7000 TO &7012

410 READ Y

420 POKE X.Y

430 NEXT

440 RETURN

450 DATA &2A,&18,&70,&CD,&00,&B9,&F5

460 DATA &CD,&06,&B9,&7E,&32,&20,&70

470 DATA &F1,&CD,&OC,&B9,&C9

```

With these changes, the program will dump ROM, upper and lower. To see why, we must consider the machine code routine set up by lines 400-470:

| 7000 | 2A 18 | 7Ø | LD   | HL, (7Ø18) | ;Get byte address  |

|------|-------|----|------|------------|--------------------|

| 7003 | CD ØØ | B9 | CALL | B9ØØ       | ;Enable upper ROM  |

| 7ØØ6 | F5    |    | PUSH | AF         | ;Save previous ROM |

|      |       |    |      |            | state              |

| 7ØØ7 | CD Ø6 | B9 | CALL | B9Ø6       | ;Enable lower ROM  |

|      |       |    |      |            |                    |

| 7ØØA |       |    | LD   | A,(HL)   | ;Read byte        |

|------|-------|----|------|----------|-------------------|

|      | 32 20 | 7Ø | LD   | (7020),A | ;Store byte       |

| 7ØØE | F1    |    | POP  | AF       | ;Recover previous |

|      |       |    |      |          | ROM state         |

| 700F | CD ØC | В9 | CALL | B9ØC     | ;Restore previous |

|      |       |    |      |          | ROM state         |

| 7Ø12 | C9    |    | RET  |          | ;Return to BASIC  |

Lines 300-320 in BASIC set the value of A in 7018/9, lower byte first, as usual. The subroutine in machine code is called, and the value of A is picked up in HL. B900 is called to enable the upper ROM, and the value it returns in the A register is pushed on to the stack out of harms way. B906 enables the lower ROM, and then the byte pointed to by HL is read into the A register and thence into 7020. The previous ROM state is recovered from the stack, and a call to B90C restores the ROMs to their previous state.

Back in BASIC, PEEK(&7020) recovers the byte, and the program then proceeds as the original did.

Simple though this machine code is, purists may object that parameters could be passed by an extension of BASIC line 300, but that is scarcely worth while for such a short routine. The number of parameters (in this case one, the variable A) would be given in the A register, and register IX would point to the parameter value, which would have to be transferred to HL, converting it from floating point form in the process. The facility for passing parameters is useful, but only when it is fully justified.

Putting that aside, you should now have a reasonably clear picture of the memory system in your mind. To make good use of the knowledge you will need to know other things, but even a tyro may be tempted to experiment. There is plenty of room ...

Talking of room, it is interesting to consider the statement that 42K of memory is available to the user. In hexadecimal terms, this is A800, so the claim is not exaggerated. It would almost be true to say 43K . . . However, the exact usage of workspace are not too clear.

## **The Inner Peripherals**

## The I/O Address Map

| Address      | Output               | Input                  |

|--------------|----------------------|------------------------|

| ØØXX to 7EXX | Do not use           | Do not use             |

| 7FXX         | Video Gate Array     | Do not use             |

| 80XX to BBXX | Do not use           | Do not use             |

| BCXX         | CRTC Register Select | Do not use             |

| BDXX         | CRTC Data            | Do not use             |

| BEXX         | Do not use           | Reserved (CRTC Status) |

| BFXX         | Do not use           | CRTC Data              |

| CØXX to DEXX | Do not use           | Do not use             |

| DFXX         | Expansion ROM Select | Do not use             |

| EØXX to EEXX | Do not use           | Do not use             |

| EFXX         | Printer Latch        | Do not use             |

| FØXX to F3XX | Do not use           | Do not use             |

| F4XX         | PPI Port A Data      | PPI Port A Data        |

| F5XX         | PPI Port B Data      | PPI Port B Data        |

| F6XX         | PPI Port C Data      | PPI Port C Data        |

| F7XX         | PPI Control          | Undefined              |

| F8XX         | Expansion Bus        | Expansion Bus          |

| F9XX         | Expansion Bus        | Expansion Bus          |

| FAXX         | Expansion Bus        | Expansion Bus          |

| FBXX         | Expansion Bus        | Expansion Bus          |

| FCXX to FEXX | Do not use           | Do not use             |

| FFXX         | Not used             | Not used               |

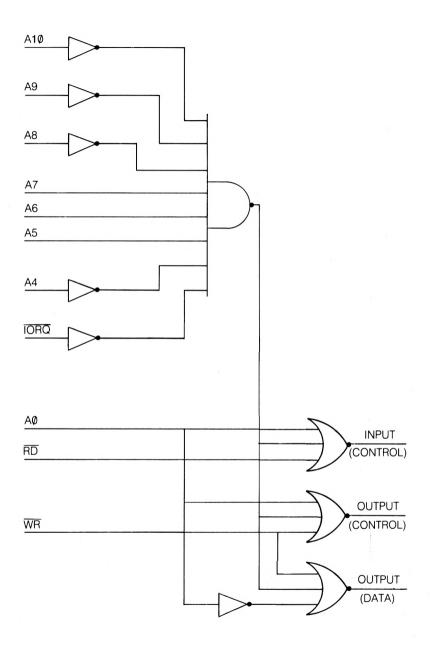

The arrangement of I/O addresses, summarised in the table given here, appears even more complex than the memory map, but the hardware decoding is relatively simple.

\*If address bit A15 is low, the Video Gate Array is selected.

\*If address bit A14 is low, the CRT Controller is selected.

\*If address bit A13 is low, the expansion ROM number must be set.

\*If address bit A12 is low, the printer latch is selected.

\*If address bit A11 is low, the PPI is selected.

\*If address bit A1Ø is low, an expansion channel is implied.

Not more than one of bits A10 to A15 may be low in a given address, which accounts for the large number of 'do not use' restrictions. It is especially important that this rule is observed for inputs, since physical damage could otherwise occur.

In the case of the CRT Controller and the PPI, bits A8 and A9 select a particular function of the device.

Since all the address bits used as above are in the upper byte of the address, the Z80 instruction OUT (N),A must not be used. It defines the upper address byte from the contents of the A register, which must also hold data. IN A,(N) might be used, if the required upper byte is first defined in the A register, but its use is not encouraged.

The correct form of I/O instruction is OUT (C),r or IN  $r_{r}(C)$ , where r is an eight-bit register. In this case, the I/O address is defined by the contents of the BC register. The 'repeating' instructions INIR, INDR, OTIR, OTDR must not be used, as they employ the B register as a counter, and would generate changing addresses.

There is a further limitation for user peripherals, arising from the way the lower byte of the address is used.

\*If address bit 7 is low, the disc system is selected.

\*If address bit 6 is low, a reserved function is selected.

\*If address bit 5 is low, a communications channel is selected.

For user peripherals, all these bits must be high, but a low byte of &FF also has a special meaning, F8FF calling for all expansion devices to be reset. The addresses available to the user are thus:

F8EØ — F8FE F9EØ — F9FF FAEØ — FAFF FBEØ — FBFF

This provides for free use of bits Ø, 1, 2, 3, 8 and 9, giving plenty of scope, providing simplified decoding is not used. If all these bits, plus bit 10 low, are taken into account, 64 I/O channels

can be defined. If each bit were related to a particular channel, no more than six channels could be used.

It is worth re-emphasising that the use of illegal I/O addresses could cause damage in input operations, since more than one data source could attempt to drive the highway.

## The Video Gate Array

The Video Gate Array, on address 7FXX, has three types of data, distinguished by the state of bits 6 and 7 of the data. The bit allocations are as follows:

| 76543210                           | Mode & ROM setting.                                             |

|------------------------------------|-----------------------------------------------------------------|

| 1 Ø X X X X X X                    | MODE Control: ØØ Mode Ø<br>Ø1 Mode 1<br>10 Mode 2<br>11 Illegal |

|                                    | Lower ROM: Ø enable<br>1 disable                                |

|                                    | Upper ROM: Ø enable<br>1 disable                                |

|                                    | Clear raster 52 divider if 1                                    |

|                                    | Reserved. Must be Ø.                                            |

| 76543210                           | Palette Pointer Register.                                       |

| 0 0 0 X X X X X                    | Palette pointer number.                                         |

| 7 6 5 4 3 2 1 Ø<br>Ø 1 Ø X X X X X | Palette Memory.                                                 |

| 76543210                           | Colour number                                                   |

| 1 1 X X X X X X                    | Reserved.                                                       |

For mode and ROM setting, it is essential to supply all the active bits in the correct state, and this calls for a copy of the last

output byte to be maintained. Such a copy is held in alternative register C' of the Z80. However, reference to that copy is automatic when the standard jumpblock entries are used to make changes, so there should be no need to refer directly to the register contents.

For colour setting, the palette pointer determines the ink to be set, and the output to the palette memory determines the colour, which is thereafter used to interpret data read from screen memory.

The main function of the Video Gate Array is to obtain data from the screen memory, on the basis of addresses supplied by the CRT Controller, and rearrange it into a suitable form for transmission to the Video Display Unit.

The need for user access to the Video Gate Array is limited, since the system takes care of all necessary actions, but there could be special circumstances in which extremely fast response was needed that could only be implemented by direct access.

#### The CRT Controller

The HD6845S CRT Controller is a standard component of considerable complexity, and it can only be described here in relatively superficial terms. It can be set up to control screen displays of varying sizes and characteristics, generating the screen reference addresses, the sync pulses, and putting up a synthesised cursor character on demand.

The action of the chip is controlled by the contents of a number of registers, eighteen in all, of which the present system accesses sixteen. To set up these registers, it is necessary to output the relevant register number on address BCXX, then the data on BDXX. The standard settings are as follows:

#### RØ Horizontal Total:

This determines the horizontal scan period as 64 character periods, which are in turn determined by the clock frequency, in this case 8 MHz, giving one character width per microsecond.

63

#### R1 Horizontal Displayed:

character periods.

This determines that 40 characters per line will be displayed, the flyback blanking occupying

#### **R**2 H Sync Position: 46

The horizontal sync pulse is generated 6 character periods after the end of displayed characters.

#### R3 Sync Width: 142

This is a compound number, determining the width of the vertical and horizontal sync pulses. The vertical sync pulse is given as having a duration of 8 scan lines, while the horizontal sync pulse has a duration of 14 character periods. (8\*16+14=142)

#### R4 Vertical Total U.K. 38. U.S.A. 31

The total number of character lines (minus 1) has to be different for 50 and 60 Hz scans. Each character line uses 8 scan lines, so the precise figures would be 39.0625 and 32.8125, remembering that only one frame is used, not two in interlace. The adjustment necessary is made by R5.

#### R5 Vertical Total Adjust: UKØUSA6

This adds six scan lines to the vertical total in the 60 Hz case. The 50 Hz total is 39, while the 60 Hz total is 32.75. These are acceptably close for practical purposes.

#### **R**6 Vertical Displayed: 25

Twenty-five character lines are specified.

#### **R**7 Vertical Sync Position: U.K. 30, U.S.A. 27

Here again, there are two different standards. For 50 Hz, the vertical sync begins 5 character line periods after the displayed area, whereas only two character lines delay can be allowed in the 60 Hz case. In the 50 Hz case the vertical sync ends after 38 scan lines.

#### 40

24

while in the 60 Hz case it ends at the full 32 character. line count, and is cut from 8 to 7 character line periods.

#### **R**8 Interlace Mode and Skew: Ø

A zero entry calls for no interlace, no skew.

#### R9 Maximum Scan Line:

This determines the number of scan lines per character line, less one. There will be eight scan lines per character.

7

**R10** Cursor Start: Ø

No cursor is generated, because:

R11 Cursor End: Ø

The cursor synthesised by the chip has zero height.

- R12 Start Address (H): 48

- R13 Start Address (L): Ø

This determines the start address for screen memory scan as 48 \* 256 = 12288 (3000 hex). The address is modified by the Video Gate Array.

- R14 Cursor Register (H): 192 R15

- Cursor Register (L): Ø

This sets up the cursor address as &CØØØ.

It need scarcely be said that these register values are so closely interlinked that any change will destroy the display. Any changes need to be carefully worked out in advance, taking into account the fact that the Video Gate Array will modify the results in some instances. For Mode 2, only one bit is needed to define a pixel, only one byte is needed to define a row of a character pattern. Eighty bytes must be read to define a screen line. For Mode 1, twice as many bytes are needed, but there are half as many characters per line, so the total number of bytes read per scan line is still 80, though they are processed in a different way. This can be repeated for Mode Ø.

The addresses provided by the CRT Controller therefore have to be processed before use. Only 4Ø addresses are provided by the CRTC per scan line, but 8Ø bytes have to be read. The necessary conversion is simple enough, but needs to be remembered by anyone indulging in screen adventures. In general, such activities are best forgotten. The CRT Controller can usually be regarded as a fixed-performance device, though changes to the start address may have uses.

One function remains to be mentioned, and that concerns the Light Pen. This uses a pin connected to the expansion interface. A low to high transition on this pin causes the current screen address to be copied into R16 (high byte) and R17 (low byte) whence it may be read. The correct interpretation of this address is best obtained by experiment, owing to the action of the Video Gate Array in modifying addresses. The following outline of the screen RAM layout will assist in this respect.

In all modes, the screen memory occupies 16K of RAM, normally from CØØØ upwards. By use of the call SCR SET BASE the screen can be moved to 4000 upwards, but other positions are unacceptable.

The screen memory is divided into eight 2K blocks. Each scan line of the display uses 8Ø consecutive bytes, but the first scan line draws data from block Ø, the second draws data from block 1, and so on. Hence the first character in the top left corner is defined by bytes at addresses CØØØ, C8ØØ, DØØØ, D8ØØ, EØØØ, E8ØØ, FØØØ, F8ØØ, each giving one row of the character pattern or, in Modes Ø and 1, part of the information for such a row. Mode 2 needs only one byte to define a character row, Mode 1 needs two, and Mode Ø needs four.

For Mode 2, the pixels in a character pattern row are defined by the bits of the byte read from screen memory.

For Mode 1, the pixels from left to right are determined by bits 3 and 7, 2 and 6, 1 and 5, Ø and 4, and then the same bits of the next byte continue the pattern row.

For Mode Ø, the first pixel is defined by bits 1, 5, 3 and 7 of the first byte, the next by bits Ø, 4, 2 and 6, then by the corresponding bits of the three subsequent bytes.

None of this need worry you in the ordinary way, since the firmware takes care of all the necessary conversions and interpretations, but it will at least explain the odd byte patterns which you get if you dump screen RAM.

As a final complication, an offset is used, controllable by the call SCR SET OFFSET (See the tabulation of operating system calls given later). Changing the offset by &50 rolls the screen up or down by one line. Now, this is an area where a great deal of experiment is justified, but be wary. Remember that the rules for each mode are different, so there will be different consequences if you make small changes in the offset. Mode 2 will respond to unit changes, but Mode 1 must have changes which are a multiple of two, and Mode Ø requires a multiple of four.

Approached with suitable caution, the screen offers a number of interesting possibilities, but rash fiddling will create chaos. Look through the list of operating system calls, and use them after careful thought.

### The Parallel Peripheral Interface

The Parallel Peripheral Interface is another standard component. It implements three ports, which can be set up for input or output. Each port has its own address, and the control register, which determines port action, has a fourth address.

In the CPC464, the standard configuration is:

- Port A: Input or output as necessary. Bidirectional communication with the data lines of the sound generator chip. Output is used to set up sound: Input senses keyboard output.

- Port B: Input only, with the following allocations:

Bit Ø: Frame flyback pulse Bit 1: Ø if link LK1 fitted These links determine Bit 2: Ø if link LK2 fitted the name which the Bit 3: Ø if link LK3 fitted CPC464 gives itself! Bit 4: Ø if link LK4 fitted (60 Hz frame scan) Bit 5: Ø if expansion port active Bit 6: 1 if printer busy Bit 7: Cassette data Port C: Output only, with the following allocations:

- Bit Ø: Keyboard input Ø

- Bit 1: Keyboard input 1

- Bit 2: Keyboard input 2

- Bit 3: Keyboard input 3

- Bit 4: Cassette motor control

- Bit 5: Cassette data

- Bit 6: BC1 to sound chip

- Bit 7: BDIR to sound chip

These allocations are essential, but as a matter of interest the chip configuration is set up by sending a control word to I/O address F7XX. This word has two formats, one setting up the chip mode, the other setting or resetting bits of Port C, of no great interest in this context.

The format for mode setting is:

7 6 5 4 3 2 1 Ø 1 X X X X X X X Port C low Port B Mode for above Port C high

Port A

Mode for above

Mode Ø is basic input/output, mode 1 is strobed input/output, mode 2 is bi-directional bus. If a port bit is set to Ø, the port works in output mode, if the bit is set to 1 the port works in input mode. The byte sent by the CPC464 control system is &82, setting mode Ø, Port B input, Ports A and C output. (Port C is implemented in two halves, which can be set up independently.)

Being deeply embedded in the hardware system, the PPI offers little scope for experimentation or change.

| STROBE                                   | 1                                 | 19                                           | GROUND                                               |

|------------------------------------------|-----------------------------------|----------------------------------------------|------------------------------------------------------|

| DØ                                       | 2                                 | 20                                           | GROUND                                               |

| D1                                       | 3                                 | 21                                           | GROUND                                               |

| D2                                       | 4                                 | 22                                           | GROUND                                               |

| D3<br>D4<br>D5<br>D6<br>D7<br>NC<br>BUSY | 5<br>6<br>7<br>8<br>9<br>10<br>11 | 23<br>24<br>25<br>26<br>27<br>28<br>29<br>20 | GROUND<br>GROUND<br>GROUND<br>GROUND<br>GROUND<br>NC |

| NC                                       | 12                                | 3Ø                                           | NC                                                   |

| NC                                       | 13                                | 31                                           | NC                                                   |

| GROUND                                   | 14                                | 32                                           | NC                                                   |

| NC                                       | 15                                | 33                                           | GROUND                                               |

| GROUND                                   | 16                                | 34                                           | NC                                                   |

| NC                                       | 17                                | 35                                           | NC                                                   |

Note: A 34-way connector is used, but the numbering is adapted to suit the 36-way printer connector, on which pins 18 and 36 are unused.

#### FIGURE 3: PRINTER CONNECTOR

## **The Printer Port**

The 'Centronics Latch', addressed by EFXX, is quite simple, in fact a little too simple for some users, since it carries only seven data bits, plus a strobe. There are a number of printers which will find their performance limited, though only by a loss of the block graphics of the type associated with Tandy systems. The upper control codes, beginning at &80, are also lost, but while that could be an embarrassment on some machines, due to conflict of the lower control codes with VDU codes, the separation of VDU and printer data into different streams makes the loss less important.

Note, however, that bit 7 of any codes in the upper half of the ASCII range will be lost, which may on occasion produce unexpected results.

If an attempt is made to drive the printer directly, the following rules must be applied:

The data bits must be firm at least 1  $\mu$ S before the start of the strobe pulse, and must remain firm until at least 1  $\mu$ S after the end of the strobe pulse.

The duration of the strobe pulse must be 1 to 500  $\mu$ S.

The strobe pulse must not be transmitted when the Busy signal from the printer is true. This bit can be sensed by reading bit 6 of the input to Port B of the PPI.

The need to consider these rules can be avoided by using facilities provided by the operating system:

#### CALL BDF1: MC WAIT PRINTER

The character code to be sent is in the A register on entry. If the character was sent correctly, the routine returns with carry true, but carry false indicates that the port timed out. Registers A and BC are corrupt on return, other registers unaltered.

It is possible to divert this call to user code, in which case other related calls are of interest.

#### CALL BD28: MC RESET PRINTER

The normal indirection of BDF1 is restored. There are no entry conditions, but AF, BC, DE and HL are corrupt on return.

#### CALL BD2B: MC PRINT CHAR

This calls MC WAIT PRINTER, even if the indirection has been changed.

The arrangement of these calls allows the user to get the codes being passed to the printer and apply conditional changes.

The timeout period is approximately Ø.4 sec.

Other related calls are:

#### CALL BD2E: MC BUSY PRINTER

No entry conditions. The return is with carry true if the printer is busy (or not fitted), false if the printer is idle. Flags are corrupt, but registers are preserved.

#### CALL BD31: MC SEND PRINTER

The character in the A register is passed to the printer. The return is with carry true, A corrupt, and other registers preserved. This call may only be used if the printer is not Busy.

These are examples of the facilities which lie in wait in the operating system for those who are able to use them. They need to be called via machine code, since parameters have to be set or flags sensed, but the routines required are simple enough for a tyro to attempt.

There is one other point to watch. The CPC464 outputs both CR and LF codes, but it also earths printer line 14, which makes some printers add another LF action. To obtain single-spaced text, it is necessary to disconnect line 14, which over-rides the setting of the internal DIL-switches. The problem does not arise with the AMSTRAD DMP1 printer, which has a slightly different interface.

# **The Outer Peripherals**

## The Programmable Sound Generator

The AY-3-8912 Programmable Sound Generator is an interesting device. It has three independent sound outputs, which can be set up to generate square-wave tones or pink noise. The volume level on each channel can be set to sixteen values, from silent to maximum, and there is a relatively simple form of internal envelope control. There are also two I/O ports, of which the CPC464 uses one.

A fully comprehensive description of this component would take up a disproportionate amount of space, but the following notes will cover the aspects special to the CPC464 system.

The PSG has sixteen control registers, and the method of accessing them is similar to that used with the CRTC: A register is selected first, and data can then be read from or written to it. The transfer modes are selected by three control lines, BDIR, BC1 and BC2. In the CPC464 BC2 is tied high, while BC1 and BDIR are controlled by bits 6 and 7, respectively, of Port C of the PPI. This gives the following modes:

BDIR BC1

- Ø Ø Inactive

- Ø 1 Read from PSG

- 1 Ø Write to PSG

- 1 1 Latch address. (Select register)

The registers may be summarised thus:

RØ-R5: Taken in pairs, determine the tone on channels A, B and C respectively. Even-numbered registers contain low 8 bits of tone data, odd-numbered registers contain upper four bits of tone data, giving 12-bit data in all.

R6. Noise Period. Five bits.

R7. Enable control. A 1 state disables, Bits Ø-2 control tone for the three channels, Bits 3-5 control noise for the three

channels, bits 6 and 7 control the two ports. (1 for output,  $\emptyset$  for input.)

R8-R1Ø. Channel amplitude. Five bits. Values Ø to &F give fixed levels. &1X gives envelope control.

R11-12. Envelope period. 16-bit word.

R13 Envelope type. Sixteen options.

R14-R15. I/O channels.

The tone period data set in the first three pairs of registers is defined by:

Period data = 125000/Required frequency.

The clock fed to the said generator is at 1MHz.

Access to the chip is simplified by the use of a call:

#### MC SOUND REGISTER: CALL BD34

A must hold register number.

C must hold data to be sent.

On exit, AF and BC are corrupt.

Use of this direct access may prove to be more convenient than control of the chip by the complex BASIC commands. The full envelope control and automatic tone envelope control are not available, but the envelope control within the chip is quite versatile. The options are chosen by a four-bit word as follows:

| Ø | to 3 | 3: | Loud | attack, | fading | to | silence. |

|---|------|----|------|---------|--------|----|----------|

|---|------|----|------|---------|--------|----|----------|

- 4 to 7: Build-up to full, then silence.

- 8: As Ø-3, but repeated.

- 9: As Ø-3.

- 10: Starts loud, fades, rises, and repeats.

- 11: Loud attack, fade to silence, then full.

- 12: Soft attack, builds to maximum, repeats.

13: Soft attack, builds to maximum, holds.

14: As 10 inverted.

15: As 4.

The contents of registers R11-R12 determine the time scales of envelope action.

The simplest way to experiment with the sound chip is to use a BASIC routine to set up the parameters and then call the following short block of machine code:

| 7000 | C5       | PUSH  | BC               |                            |

|------|----------|-------|------------------|----------------------------|

| 7001 | E5       | PUSH  | HL               | ;Save registers            |

| 7ØØ2 | F5       | PUSH  | AF               |                            |

| 7ØØ3 | 21 10 70 | LD    | HL,7 <b>Ø1</b> Ø | ;Set HL as pointer         |

| 7ØØ6 | 7E       | LD    | A,(HL)           | ;Read register number      |

| 7ØØ7 | 23       | INC   | HL               | ;Advance pointer           |

| 7ØØ8 | 4E       | LD    | C,(HL)           | ;Read data                 |

| 7ØØ9 | CD 34 BE | DCALL | BD34             | ;Call MC SOUND<br>REGISTER |

| 7ØØC | F1       | POP   | AF               |                            |

| 7ØØD | E1       | POP   | HL               | ;Restore registers         |

| 7ØØE | C1       | POP   | BC               |                            |

| 7ØØF | C9       | RET   |                  | ;Return to BASIC           |

The BASIC program must set up the above code, as was demonstrated in the dump program earlier, and poke the register number into &7010, the data into &7011. In some instances it will be necessary to set two registers to cover the complete data, and since individual ideas on the nature of the BASIC program are bound to differ it will not be given in full. Working out what is wanted will be a good exercise for a beginner, and will not trouble the more experienced.

The sound output of the three channels is combined to feed the internal loudspeaker, but split on the stereo output, channel B feeding both sides, channels A and C one side each.

The square-wave tone is broadly characteristic of the clarinet, but two or more tones of this type do not always blend well. It is worth experimenting with low-pass filters in the stereo output lines to obtain a more rounded tone.

Considerably more could be said about this interesting chip, but enough data has been provided to allow and encourage experiment.

# The Keyboard

The keyboard is of the usual matrix-connected type, using ten input rows and eight output columns. The rows are driven by bits Ø-3 of channel C, and the columns are sensed via the PSG port and Port A of the PPI.

The key number allocated to a given key is given by adding the column number to eight times the row number. Thus the key connected to the third row wire and the second column wire is number 17, the wires being numbered from Ø.

The keyboard is checked fifty times a second, and if any key is depressed its number is entered in a buffer, and an entry is made in a 'bit map'. The key remains marked as depressed until it has been released for two successive scans, this being a protection against contact bounce. However, the system is vulnerable to the simultaneous depression of three keys at the corners of a rectangle of the matrix, the key at the fourth appearing to be depressed as well. This does not seem to create problems in practice.

It is only when a key number is removed from the keyboard buffer that it is translated into a code, by reference to three tables that define the key/code relationship for different shift states. The shift state is also determined by buffer contents, so there is no risk of translation error arising because the shift state has changed since the key was pressed.

In addition to the Caps Lock state, toggled into and out of use by the Caps Lock key, there is also a Shift Lock state, which can be toggled on and off by pressing the Caps Lock key with the Control key pressed, but direct transition from Shift Lock to Caps Lock and vice versa is not possible. The normal state must intervene.

For certain code values, expansion into strings is possible, and the system is arranged so that either the code value or the expansion can be obtained, according to which operating system call is used.

The joystick connector links directly into the keyboard matrix, and is sensed by the same mechanism.

### The Cassette Recorder

The cassette recorder has a three-wire interface with the rest of the system, the input and output data paths and the motor control. It is a welcome fact that fast forward wind and rewind are not affected by motor control, and can be used at any time.

The recording method used employs square-wave cycles, those for a high bit having twice the duration of those for low bits. The mean frequency can be varied between 700 and 2500 baud, though 1000 and 2000 baud are regarded as standard. During playback, the system deduces the recording speed used by examination of the leader tone, which consists of a long sequence of high-state cycles.

The overall format of a record is:

A leader.

N segments.

A trailer.

The leader consists of a pre-record gap, 2 Ø48 high-state bits, a zero bit, and a sync byte. The sync byte is &2C for a header record, &16 for a data record.

Each segment consists of 256 data bytes and two CRC (Cyclic redundancy check) bytes. The CRC polynomial used is:

$x^{15} + x^{12} + x^5 + 1$

The initial seed is &FFFF. The first CRC byte is the high byte.

The trailer consists of 32 high-state bits.

The complete file begins with a header record containing 64 bytes which determine the way in which the remaining records in the file are read and interpreted. The make-up of the header is shown in the following table.

#### HEADER BLOCK FORMAT FOR CASSETTE RECORDING

- Bytes 0/15: Filename, padded out with null codes.

- Byte 16: Block number.

- Byte 17: Non-zero if last block.

- Byte 18: File type:

- Bit 0: True for protection.

Bits 1-3: 0: Internal BASIC

- 1: Binary

- 2: Screen Image

- 3: ASCII

- 4-7: Unallocated

Bits 4-7: Version (1 for ASCII, else 0)

- Bytes 19/20: Data length. (Of record)

- Bytes 21/22: Data location. (Start address when recorded)

- Byte 23: Non-zero if first block.

User fields:

- Bytes 24/25: Number of bytes in file.

- Bytes 26/27: Execution address for machine code.

- Bytes 28/63: Unallocated.

The operating system calls associated with the cassette recorder are somewhat more comprehensive than those available in BASIC. CAS NOISY will disable prompt messages, CAS RE-TURN puts a character back into the read buffer, so that it can be examined but read again later, CAS OUT ABANDON allows an output file to be discarded, while CAS CHECK compares a record on tape with the contents of store, giving a Verify facility. These calls will be found listed in the tabulation of operating system calls. In general, the normal cassette handling facilities will suffice for most purposes, but it is useful to know that there are other possible modes of working. These, however, are likely to be purely local, and would not produce tapes that could be used on other CPC464 machines, and that is a deterrent.

An important point to note is that normal interrupt service is suspended while the cassette recorder is in use, since interrupt handling could ruin the signal timings. The elapsed time clock does not advance, and other interrupt-controlled functions are left to their own devices.

However, at whatever level it is used, the cassette system has its advantages. There is one mystery about it which has not been solved, though. After text data has been recorded or recovered, there is sometimes a long wait for the prompt messages. It is suspected that a 'garbage disposal' session is involved, the time being about right . . .

# The Operating System

Having examined the internal hardware of the CPC464, we must now look at the firmware. This is not a simple matter. There are more than 200 entry points, and all are in RAM, so that they can be altered if you wish, accessing your own code instead of — or in addition to — the normal routines.

For each entry point there is a function to be performed, there are entry conditions, there are exit conditions, and there is a list of the registers and flags that will have been corrupted. All this is tabulated at the end of this section, in concise form to minimise the space consumed.

Some of the routines, which have no entry conditions and which return no data, are accessible from BASIC, but as we have already seen there is usually a need to pass parameters from BASIC to machine code and back.

The standard method of passing parameters is effective but a little complex. Anyone using it is immediately confronted by the complications of the different ways in which data is stored by BASIC: Integers are held in pairs of bytes as straight binary, low byte first.

Strings involve a string descriptor and a string body. The string descriptor uses three bytes, the first to define the length of the string, then the address of the actual string. Only the descriptor need be passed as a parameter.

Real numbers are stored in five-byte floating point, the mantissa first (lowest byte first), and the exponent byte last. Converting that to integer form, or attempting to perform calculations with it would be far from easy.

Fortunately, the parameters of a CALL are passed in simplified form. The integer is passed as a signed two-byte word, effectively unchanged. A real number is forced into unsigned integer form. A variable is passed as its address, and the address of a string descriptor is given.

Each parameter is therefore passed as a two-byte word, and the words are stored in a block to which the IX register points, while the number of parameters is set in A. To complicate matters, IX initially points to the last parameter.

So, suppose you want to call GRA LINE ABSOLUTE, which draws a line to a point defined by the contents of DE and HL, as the X and Y coordinates of the end point. You cannot call the entry address, BBF6, directly, because DE and HL must be set up first. What you will have to work from is:

A = 2 (Two parameters)

(IX + 2) = Parameter 1 (X)

(IX) = Parameter 2 (Y)

You need a routine which will copy (IX) to HL, and (IX+2) to DE. That is fairly simple:

7000 DD 6E 00

LD

L,(IX)

7003 DD 66 01

LD

H,(IX+1)

7006 DD 5E 02

LD

E,(IX+2)

7009 DD 56 03

LD

D,(IX+3)

Then you can call BBF6, following it by a return code (C9).

Notice that the count of parameters in A was not used. We assumed that it was correct.

Perhaps you can see now why it was considered easier to pass parameters in the earlier BASIC/machine-code routines by poking them into store locations. Not as neat on the BASIC side, perhaps, but easier overall. It would be possible to create a general routine for picking up parameters, in which case the eventual call, if any, would be one of the parameters, but poking and peeking are usually simpler.

No, it is not an easy matter to make use of operating system routines by BASIC alone. To get the most out of the CPC464, you must tangle with machine code.

As noted earlier, there are a few operating system entries which can be used from BASIC without trouble. Many of these, however, are already accessible via BASIC commands. Scan through the tabulation, and you will soon pick out those that are usable but not already covered.

One final point on this theme: BASIC seems able to recover after a CALL without difficulty, but it may sometimes be useful to save the main registers on the stack before calling an operating system routine and restore them afterwards, just in case . . .

# The RST Area

Mention has been made of the routines packed into the 'RST Area', and you will need to know about these if you are to take full advantage of the facilities offered. The available entries are:

- 0000 Startup entry, also accessed by op-code &C7. Complete reinitialisation follows use of this entry.

- ØØØ8 Accessed by &CF, which has been converted into a pseudo op-code. The two bytes following &CF are picked up as data, using the standard low-byte-first convention. Bits Ø to 13 define an address in the bottom quarter of memory. Bit 14 controls lower ROM, a 1 state disabling, and bit 15 similarly controls the upper ROM. It is therefore possible to switch banks and jump in response to a single call, the actions appearing simultaneous. For example, CF F2 87 will

jump to 07F2 with the lower ROM enabled and the upper ROM disabled.

- 000B Similar to 0008, but the two-byte definition is in HL.

- ØØØE Jump to an address defined in BC.

- ØØ1Ø Accessed by &D7. This is known as SIDE CALL. The defining bytes follow &D7. Bits Ø-12 are added to CØØØ to define an address in upper ROM, while bits 13-15 define a 'sideways ROM in terms of an offset from the ROM select address of the main foreground ROM. This allows direct access to a point in a given sideways ROM.

- 0013 Known as SIDE PCHL. As 0010, but the two defining bytes are in HL.

- 0016 Known as PCDE. Jump to an address defined in DE.

- ØØ18 Accessed by &DF. Known as FAR CALL. The two bytes which follow &DF are the address of a threebyte definition, in which the first two bytes give the required memory address, the third byte YY selecting a sideways ROM on the following basis:

- YY = Ø to &FB: Select ROM YY: Enable upper, disable lower.

- YY = &FC No ROM change: Enable upper, enable lower.

- YY = &FD No ROM change: Enable upper, disable lower.

- YY = &FE No ROM change: Disable upper, enable lower.

- YY = &FF No ROM change: Disable upper, disable lower.

- ØØ1B FAR PCHL. As ØØ18, but address in HL, YY in C.

- ØØ1E PCHL: Jump to address defined in HL.

- ØØ2Ø RAM LAM. Equivalent to LD A,(HL), but always accesses RAM, whatever the ROM state. Accessed by &E7.

- 0023 FAR ICALL. HL holds the address of a three-byte definition, of which the first two bytes define an address, and the third has the significance of YY as listed above.

- ØØ28 FIRM JUMP. Accessed by &EF. The two bytes following &EF define a location in lower ROM or central RAM. Note that this is a jump, not a call, and a return address must be supplied on top of the stack.

All the above are copied from ROM into RAM during initialisation, and must not be altered. We now reach a point where 'patching' is permissible.

0030 If this point is entered (by &F7) with the lower ROM enabled, the following actions are executed:

Disable interrupt

Copy current ROM state to ØØ2B

Disable lower ROM

Enable interrupt

Go to ØØ3Ø (In RAM)

It is therefore possible to patch user code in the ØØ3Ø-ØØ37 area with the assurance that it will be executed if ØØ3Ø is entered, whether the lower ROM is enabled or not. Location ØØ3Ø in RAM is initialised to &C7 to cover a situation where no patching is carried out. The standard operating system does not call ØØ3Ø.

The Z80 is set for operation in interrupt mode 1, so it responds to an interrupt signal by calling an entry to ØØ38. Since either ROM or RAM may be active when interrupt occurs, both store banks must hold a jump to the interrupt handler. If the handler fails to recognise the source of the interrupt, it calls ØØ3B, which usually holds a return op-code in both ROM and RAM. The call is made with ROM disabled, however, so the user can patch his own code in RAM between ØØ3B and ØØ3F. The code will normally be a jump to a handling routine stored elsewhere.

The entry at ØØ38 could — but must not — be called by opcode &FF. Making full use of these facilities calls for careful thought and a familiarity with the Z80 instruction set. However, the worst consequences of mistakes can be put to right by a system reset.

# **Jumpblock Entries**

At the end of this section, a list of more than two hundred operating system calls is given. These should normally be accessed by way of the 'jumpblock' entries, which are held in RAM and can therefore be modified. This provides a powerful programming tool.

Suppose, for example, that you wish to alter the routine that sends code to the printer. This is accessed at BD2B, the MC PRINT CHAR entry. At BD2B there is the following code:

#### CF F2 Ø7

As noted earlier, this performs a jump to Ø7F2 in lower ROM, where the printer driver routine is stored. However, the link can be patched to give a jump to an entirely different user routine, which is executed in place of the standard routine. Details of this procedure are given in the latter part of the book, in relation to an alternative set of hardware forming an eight-bit printer interface.

Since the revised code will be held in RAM, and preferably in the centre half of the address range, the CF command is not necessary, and a normal &C3 jump code will be adequate.

It will be evident that some operating system calls should not be altered, since the consequences of change would be too extensive, but cautious experiment will always be in order.

### Interrupts and Events

The CPC464 uses four standard timed interrupts:

\*The Fast Ticker, occurring 300 times a second.

\*The Sound Timer, occurring 100 times a second.

\*The Frame Flyback, occurring at vertical scan frequency.

\*The Ticker, occurring 50 times a second.

These are all normal interrupts of the maskable type. No provision is made for dealing with Non-Maskable Interrupts (NMI), which would cause a jump to 0066. That might be in ROM or RAM, so the consequences would be unpredictable.

Events are short routines which may be triggered by interrupts or by permission of the current foreground program. Those triggered by interrupt are called 'asynchronous events', those triggered by program action are called 'synchronous events'. Normally, a queue of event calls is used, with separate queues for the two kinds of event, but 'express events' are serviced as soon as they are called. Express events should be as short as possible, and may not enable interrupt or corrupt the IX and IY registers.

Events are defined by 'event blocks', which are set up by the operating system call KL INIT EVENT on the basis of data supplied. This data includes the address and ROM number of the routine to be executed, and the location of the event block, which is seven bytes long. The class of the event must also be stated, using a byte defined as follows:

Bit  $\emptyset$  is true if the event involves a 'near address', false if a 'far address' applies. (see notes on the RST area.)

Bits 1 to 4 are only relevant to synchronous events, for which they define a priority level.

Bit 5 is always zero.

Bit 6 is set to 1 for an express event.

Bit 7 is set to 1 for an asynchronous event.

KL INIT EVENT sets up an event block of the form:

Bytes Ø,1: Chain Link to next block.

Count of events outstanding Reversed CPC464 documentation. Byte 2: in

Byte 3: Class of event

Bytes 4,5: Address of event routine.

Byte 6: ROM select state required.

Bytes 7 onward may be set by the user to provide parameters.

To allow the event routine to pick these up, it is supplied with the address of the event block.

When an event is 'kicked', the count in byte 3 is incremented, and the count is decremented when the event is serviced. An event can be disabled by setting the count byte to -64. If the count is zero it is not decremented, and if it is &7F it is not incremented.

Operating system calls are available to arm and disarm events. The foreground program must check at regular intervals for outstanding synchronous events.

For asynchronous events, the event block is tagged on to a header block appropriate to the type of interrupt involved. For Ticker interrupts:

Bytes Ø,1: Tick chain link.

Bytes 2,3: Tick count.

Bytes 4,5: Recharge count.

Bytes 6 on: Event block.

The count is set from the recharge count when an event is 'kicked', and is then decremented for each appearance of the Ticker interrupt. When the count reaches zero, the event is again kicked, and the count is set to the recharge value. Thus, if the recharge count is set to 5, the event will be kicked on every fifth Ticker interrupt, or ten times a second.

For Frame Flyback and Fast Ticker interrupts, only the Chain Link is prefixed to the event block.

Note that event and interrupt blocks are set automatically by operating system calls, and should not be modified by the user except where otherwise indicated.

On first acquaintance, the interrupt and event system is of daunting complexity, but its potential is enormous. Using it to display the time of day in a corner of the screen, while a normal program proceeds, is merely scratching the surface of the possibilities. A really inspired user might well fill the entire area of middle RAM with event blocks and their routines, but that could lead to a situation in which the computer was asked to achieve the impossible. There is only one processor, and it can only do a given amount in a given time. Each event pulls it away from its foreground task, using up execution time and perhaps reducing foreground time to nearly zero.

In particular, the Fast Ticker needs to be used with caution. If the events it calls take, say, 330 microseconds to execute, they will absorb a tenth of the processing time, slowing down foreground execution in the same proportion.

All event and interrupt blocks should be held in the centre half of RAM, so that they are always accessible. A 'safe area' can be defined by using the BASIC command MEMORY, which can be used to create a protected area of store. This will be examined in more detail later.

# **Operating System Calls**

The operating system calls identified by AMSOFT are listed here in as concise a manner as possible. Further details can be found in the AMSTRAD CPC464 Firmware book. (See bibliography.)

Each call is identified by a name and the address of its jumpblock entry. Each jumpblock entry defines the address of the actual routine, and that address could be used if speed is vitally important, but the correct ROM state must then be set, whereas the jumpblock entry sets the state required automatically.

It should also be noted that AMSTRAD guarantee the jumpblock entries, but not the direct routine entries, which may change in later versions of the ROM.

For one section of the jumpblock, no call names or functions are described by AMSOFT. Investigation of some of these entries showed a converter from integer variables to floating point and other useful functions. These are used by BASIC, but a full definition of their characteristics is not feasible, since they involve a knowledge of the internals of the BASIC interpreter.

It can be assumed that registers not mentioned under Exit conditions are preserved. However, it should be noted that this does not include the 'alternate' registers, which are not available for the user.

# **Operating System Calls**

#### KM INITIALISE: BBØØ

Initialises Key manager completely, all variables, buffers and special indirections being lost.

No entry conditions.

On exit AF, BC, DE and HL are corrupt.

### KM RESET:

### BBØ3

Resets Key Manager indirections and buffers.

No entry conditions.

On exit AF, BC, DE and HL are corrupt.

### KM WAIT CHAR: BBØ6

Waits for a character from the keyboard buffer or expansion string.

No entry conditions.

On exit the character code is in A and carry is true. Other flags are corrupt.

### KM READ CHAR: BB09

Takes a character from the keyboard buffer or expansion string if one is immediately available. Does not wait.

No entry conditions.

On exit, if a character is available the code is in A and carry is true, else carry is false and A corrupt. Other flags corrupt.

### KM CHAR RETURN: BBØC

A character is re-inserted in the keyboard buffer, so that it can be read again later, allowing the character to be checked without being lost.

Only one character can be 'put back' at a time. The character put back must be read before another is put back.

On entry, A holds code of character to be put back.

On exit, all flags and registers are preserved.

### KM SET EXPAND: BBØF

Sets up an expansion string related to a given token code.

On entry, B holds the expansion token to be used, and C holds the length of the string to be set. HL points to the string.

On exit, carry is true if the setting was successful, else false. A, BC, DE, HL and other flags are corrupt.

Note: The string must lie in RAM, not ROM.

#### KM GET EXPAND: BB12

Read a character from an expansion string. The first character is number  $\emptyset$ .

On entry, A holds the expansion token and L holds the character number.

On exit, if the get was successful carry is set and the character code is in A, else carry is false and A is corrupt. DE is corrupt, and so are flags other than carry.

### KM EXP BUFFER: BB15

A buffer for expansion strings is allocated, and initialised with the default expansion strings.

On entry, DE holds the address of the buffer, HL holds its length.

On exit, carry is true unless the buffer is too short. A, BC, DE, and HL are corrupt, so are flags other than carry.

### KM WAIT KEY:

#### BB18

Waits for a key from the key buffer.

No entry conditions.

On exit, carry is true and A holds the character or expansion token. (Tokens are not expanded.)

### KM READ KEY: BB1B

Takes a key from the key buffer if one is available.

No entry conditions.

On exit, if a key was available carry is true and A holds the character code or expansion token, else carry is false and A is corrupt. Other flags are corrupt.

### KM TEST KEY: BB1E

Tests whether a specified key is pressed.

On entry A holds a key number.

On exit, if the key is pressed the zero flag is false, else true. Carry is always false, C contains the current shift and control state, A, HL and other flags corrupt.

### KM GET STATE: BB21

Checks for Caps and Shift LOCK states.

No entry conditions.

On exit, L holds Shift Lock state, H holds Caps Lock state. If the lock is on, the state is &FF, else Ø. AF is corrupt.

### KM GET JOYSTICK: BB24

Check joystick state.

No entry conditions.

A and H contain state of joystick Ø. L contains state of joystick 1. Flags are corrupt.

The reported bytes have the following form:

Bit Ø UP

- Bit 1 DOWN

- Bit 2 LEFT

- Bit 3 RIGHT

- Bit 4 FIRE 2

- Bit 5 FIRE 1

- Bit 6 Spare Button

- Bit 7 Ø

#### KM SET TRANSLATE: BB27

Set code or token generated by given key.

On entry, A holds key number, B holds code or token.

On exit, AF and HL are corrupt.

The following token values have special use:

80 - 9F Expansion tokens.

EO - FC Edit system codes.

FD Caps Lock.

FE Shift Lock.

FF Ignore. (Key has no meaning.)

#### KM GET TRANSLATE: BB2A

Check translation of key with neither Shift nor Control.

On entry, A holds a key number.

On exit, A holds the translation. HL and flags corrupt.

#### KM SET SHIFT:

BB2D

Set translation of key with Shift, not Control.

On entry, A holds a key number, B holds translation.

On exit, AF and HL are corrupt.

See KM SET TRANSLATE for special code meanings.

#### KM GET SHIFT:

#### BB3Ø

Check translation of key with Shift, not Control.

On entry, A holds a key number.

On exit, A holds the translation. HL and flags are corrupt.

### KM SET CONTROL: BB33

Set translation of a key with Control.

On entry, A holds key number, B holds translation.

On exit, AF and HL are corrupt.

See KM SET TRANSLATE for special code meanings.

# KM GET CONTROL: BB36

Check translation of key with Control.

On entry, A holds a key number.

On exit, A holds the translation, HL and flags are corrupt.

### KM SET REPEAT: BB39

Determine whether a key is allowed to repeat.

On entry, A contains the key number; B contains &FF if the key is to be allowed to repeat, else Ø.

On exit AF, BC and HL are corrupt.

# KM GET REPEAT: BB3C

Check whether a key is allowed to repeat.

On entry, A holds a key number.

On exit, the zero flag is false if the key is allowed to repeat, else true. Carry is false, A, HL and other flags corrupt.

### KM SET DELAY: BB3F

Set key repeat delay and period.

On entry H holds start delay, L holds repeat period. Values are in fiftieths of a second. A zero value counts as 256.

On exit, AF is corrupt.

### KM GET DELAY: BB42

Check key repeat delay and period.

No entry conditions.

On exit, H holds start delay, L holds repeat period. Values are in fiftieths of a second. AF is corrupt.

#### KM ARM BREAKS: BB45

Enable break events.

On entry DE holds the address of the break event routine, C holds the ROM select address for the routine.

On exit AF, BC, DE and HL are corrupt.

#### KM DISARM BREAK: BB48

Disable break events. (This is the default state.)

No entry conditions.

On exit AF and HL are corrupt.

#### KM BREAK EVENT: BB4B

Generate a break if break events enabled. Disable break event.

No entry conditions.

On exit AF and HL are corrupt.

A break event token (&EF) is placed in the key buffer. This generates a break event when read from the buffer.

#### TXT INITIALISE:

#### BB4E

Full initialisation of the Text VDU, including all variables and indirections.

No entry conditions.

On exit AF, BC, DE and HL are corrupt.

#### TXT RESET:

#### BB51

Resets the Text VDU indirections and control table only.

No entry conditions.

On exit AF, BC, DE and HL are corrupt.

### TXT VDU ENABLE: BB54

Allow screen display for currently-selected stream.

No entry conditions.

On exit AF is corrupt.

### TEXT VDU DISABLE: BB57

Bar screen display for currently selected stream (including cursor).

No entry conditions.

On exit, AF is corrupt.

# TXT OUTPUT: BB5A

Output a code to the Text VDU.

On entry A holds the code to be sent.

On exit all flags and registers are preserved.

### TXT WR CHAR:

#### BB5D

Print a character at the cursor position of the current stream. Control codes are printed, not obeyed. VDU must be enabled.

On entry A holds the character code.

On exit AF, BC, DE and HL are corrupt.

### TXT RD CHAR: BB60

Read a character from the screen at the cursor position of the current stream.

No entry conditions.

On exit, if a recognisable character was found; Carry is true and A holds the character code, else carry is false and A holds zero.

Other flags are corrupt.

# TXT SET GRAPHIC: BB63

Enable or disable graphics character option.

On entry, A holds zero to turn on option, non-zero to turn it off.

On exit, AF is corrupt.

#### TXT WIN ENABLE: BB66

Set up window for current stream.

On entry, D and H contain edge columns, the smaller being the left edge. E and L contain edge rows, the smaller being the top.

On exit AF, BC, DE and HL are corrupt.

### TXT GET WINDOW: BB69

Check the boundaries of the window for the current stream.

No entry conditions.

On exit H contains left column, D contains right column, L holds top row, E holds bottom row. Carry is false if the window covers the whole screen.

In the last two calls, column and line positions count from  $\emptyset$ , not from 1, as in BASIC.

### TXT CLEAR WINDOW: BB6C

Set the text window of the current stream to the paper ink for that stream. Cursor to top left corner.

No entry conditions.

On exit AF, BC, DE and HL are corrupt.

#### TXT SET COLUMN: BB6F

Move the cursor for the current stream to a specified column.

On entry A holds the required column number. (1 upwards.)

On exit AF and HL are corrupt.

TXT SET ROW:

#### BB72

Move the cursor for the current stream to a specified row.

On entry A holds the required row number. (1 upwards.)

On exit AF and HL are corrupt.

### TXT SET CURSOR: BB75

Move the cursor for the current stream to a specified row and column.

On entry H holds the column, L holds the row. (1 upwards.)

On exit AF and HL are corrupt.

### TXT GET CURSOR: BB78

Check the location of the cursor for the current stream and the 'roll count'.

No entry conditions.

On exit H contains the column and L the row. A contains the roll count, which is decremented when the window is rolled up, and incremented when the window is rolled down. The cursor position given is not necessarily valid.

### TXT CUR ENABLE: BB7B

Enables the cursor for the current stream.

No entry conditions.

On exit, AF is corrupt.

### TXT CUR DISABLE: BB7E

Disables the cursor for the current stream.

No entry conditions.

On exit, AF is corrupt.

### TXT CUR ON:

### Allows the cursor for the current stream.

No entry conditions.

All flags and registers preserved.

### TXT CUR OFF:

### BB84

**BB81**

Prevents the cursor for the current stream.

No entry conditions.

All flags and registers preserved.

Note: BB7B/E are intended to be used generally. They override BB81/4 in respect of cursor suppression. BB81/4 are for use by system ROMs.

### TXT VALIDATE: BB87

Check if cursor within current window area.

On entry H holds column and L holds row (1 upwards) of position.

On exit: If in window, carry is true and B corrupt. If window would roll up, carry is false and B holds &FF. If window would roll down, carry is false and B holds Ø. In all cases H and L hold the column and row at which the character would appear, A and other flags corrupt.

### TXT PLACE CURSOR: BB8A

Display a cursor for the currently selected stream. This allows multiple cursors. It is unwise to call TXT PLACE CURSOR twice for a given screen position without an intervening TXT REMOVE CURSOR, as one cursor could persist.

No entry conditions.

On exit, AF is corrupt.

### TXT REMOVE CURSOR: BB8D

Remove a multiple cursor from the screen.

No entry conditions.

On exit, AF is corrupt.

### TXT SET PEN:

#### BB9Ø

Define foreground ink for current stream.

On entry A holds ink number.

On exit, AF and HL are corrupt.

#### TXT GET PEN:

# BB93

Check foreground ink for current stream.

No entry conditions.

On exit, A holds the ink number. Flags are corrupt.

#### TXT SET PAPER: BB96

Define background ink for current stream.

On entry A holds ink number.

On exit AF and HL are corrupt.

### TXT GET PAPER: BB99

Check background ink for current stream.

No entry conditions.

On exit A holds the ink number. Flags are corrupt.

### TXT INVERSE:

# BB9C

Exchange foreground and background inks for current stream.

No entry conditions.

On exit, AF and HL are corrupt.

### TXT SET BACK: BB9F

Determine whether background colour is displayed. It is displayed in opaque mode, not in transparent.

On entry, A holds Ø for opaque mode, a non-zero value for transparent mode.

On exit AF and HL are corrupt.

### TXT GET BACK: BBA2

Check whether background colour is being displayed.

No entry conditions.

On exit, A holds Ø if opaque mode applies, else a non-zero value. DE, HL and flags are corrupt.

### TXT GET MATRIX: BBA5

Get the address of a character pattern.

On entry, A holds code for character.

On exit, HL holds the pattern address. If it is in ROM, carry is false. If it is in RAM, carry is true. A and flags corrupt.

#### TXT SET MATRIX: BBA8

Set a character pattern.

On entry, A holds the character code, and HL holds the address of the matrix pattern to be set up.

On exit, carry is true if the character is user-definable, else false. A, BC, DE, HL and flags corrupt.

#### TXT SET M TABLE: BBAB

Set multiple character patterns. (Up to &FF.)

On entry, DE holds first character code, HL contains address of start or pattern source table.

On exit, if there was no user-defined table before, carry is false and A and HL are corrupt. Otherwise carry is true, and A holds the first character for the new patterns, HL holds the address of the old table. BC, DE and flags corrupt.

### TXT GET M TABLE: BBAE

Check the address of the user-defined matrix table and the code for the first character in the table.

No entry conditions.

On exit, if there is no user defined pattern table carry is false and A and HL are corrupt, else carry is true, A holds the first character code in the table, and HL holds the start address of the table. Other flags are corrupt.

### TXT GET CONTROL: BBB1