# **Z-80** REFERENCE GUIDE

# **Z80** Reference Guide

# **Z80 REFERENCE GUIDE**

Alan Tully

MELBOURNE HOUSE PUBLISHERS

### © 1984 Alan Tully

All rights reserved. This book is copyright and no part may be copied or stored by electromagnetic, electronic, photographic, mechanical or any other means whatsoever except as provided by national law. All enquiries should be addressed to the publishers:

IN THE UNITED KINGDOM — Melbourne House (Publishers) Ltd Castle Yard House Castle Yard Richmond, TW10 6TF

IN THE UNITED STATES OF AMERICA — Melbourne House Software Inc. 347 Reedwood Drive Nashville TN 37217

IN AUSTRALIA — Melbourne House (Australia) Pty Ltd Level 2, 70 Park Street South Melbourne, Victoria 3205

Printed by The Whitefriars Press Ltd, Tonbridge, Kent

ISBN 0 86161 162 4

Edition: 7654321 Printing: FEDCBA987654321 Year: 90/898887868584

# CONTENTS

| CHAPTER 1 — Introduction                            | 1  |

|-----------------------------------------------------|----|

| CHAPTER 2 — Registers and Flags                     |    |

| CHAPTER 3 — Timing                                  | 17 |

| CHAPTER 4 — Instruction Groups                      |    |

| CHAPTER 5 — Z80 Machine Code Instructions           | 71 |

| CHAPTER 6 — Hints and Tips                          |    |

| APPENDIX A — ASCII Codes                            |    |

| APPENDIX B — ASCII/Hexadecimal/Decimal Conversion   |    |

| APPENDIX C — Quick Reference to Z80 Instruction Set |    |

# **CHAPTER 1**

# Introduction

This book is intended for users and prospective users of Z8Ø based micro-computers who already have some machine code programming experience and wish to extend their ability to write and modify programs. It is designed to be a convenient reference manual when specifying and coding new programs or debugging and modifying existing systems and programs.

The Zilog Z80 micro-processor was designed to be compatible with the Intel 8080 range of micro-processors. That is programs which run on Intel 8008 or 8080 processors will also run ont he Z80, although, as the Z80 provides additional facilities (instructions, registers, block input/output, etc.) it is extremely unlikely that a program written for the Z80 would run successfully on either the 8008 or 8080.

Chapter 2 describes the various registers provided in the Z8Ø and contains tables showing the effect various groups of transactions have on the Flag Register.

Chapter 3 gives brief details of the timing principles used in the Z80.

Chapter 4 contains a summary of the instructions, identified within a number of groups, each of which is related to specific functions or activities. This chapter is intended for the programmer who knows what is required of the program and needs to select the most appropriate instruction(s).

Chapter 5 gives full details of each individual instruction, together with its effect on the Flag Register, Timing and an example of all except the most simple instructions.

Chapter 6 contains various practical hints and tips based on the experience of a number of individual programmers.

The following tables are provided as appendices for easy reference: Appendix A — ASCII Codes.

- Appendix B ASCII Hexadecimal/Decimal Conversion.

- Appendix C Glossary of Terms and Abbreviations used in this book.

Appendix D — Table of Instructions by Operator Code, indexed.

Appendix E — Table of Instructions by mnemonics, indexed.

# CHAPTER 2 Registers and Flags

Z8Ø Registers can be considered under three different groups:

| Type of Register          | No. |

|---------------------------|-----|

| General Purpose Registers | 14  |

| Flag Register             | 1   |

| Special Purpose Registers | 6   |

## **General Purpose Registers**

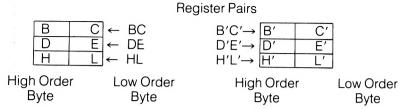

Fourteen 8-Bit General Purpose Registers are provided, in two sets, identified as A, B, C, D, E, H and L plus A', B', C', D', E', H' and L'. Only one set, together with the equivalent Flag Register (F or F') can be in use at any one time. A "set" of registers may consist of either A and F or A' and F' plus either B, C, D, E, H and L or A', B', C', D', E', H' and L', i.e.:

| Set |    | Set |    | Set |    | Set |

|-----|----|-----|----|-----|----|-----|

| А   |    | А   |    | A'  |    | A'  |

| В   |    | B'  |    | В   |    | B'  |

| С   |    | C'  |    | С   |    | C'  |

| D   | or | D'  | or | D   | or | D'  |

| Е   |    | E'  |    | Е   |    | E'  |

| н   |    | H'  |    | н   |    | H'  |

| L   |    | L'  |    | L   |    | L'  |

Special Register Selection instructions provide the facility to switch between the two sets of registers, allowing extra storage in registers, which is much faster than using external memory, particularly if interrupts are likely to occur.

The A Register is the Accumulator and is the most frequently used of all the registers. The result of an Arithmetic or Logical operation, such as ADD, SBC, XOR, etc., is always stored in the Accumulator (Register A).

The remaining six General Purpose Registers in a set can be used to store either data or memory addresses and are frequently referred to as Register Pairs — BC, DE, HL. This enables a Register Pair to be used to store a complete memory address (up to 64K) or to provide double precision arithmetic facilities.

NOTE: The H and L registers were originally designated as such because one held the High (H) byte of a memory address and the other the Low (L) byte of the same memory address.

# Flag Register

Two Flag Registers are provided, one identified as the F Register, which is always associated with Register A, and the other identified as F', which is always associated with Register A'. The Flag (F) Register contains 8 Bits, as do the General Purpose Registers, but each individual Bit is used to identify conditions within the C.P.U. (Central Processing Unit) which exist after an instruction has been obeyed. The purpose of each Bit within the Flag Register is given on the next page.

**Bit Positions**

76543210

| Bit | Flag            | Details                                                                                                                                                                                                                                                                                                                           |

|-----|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | Sign            | SET = 1 if the result of certain operations are negative, RESET = $\emptyset$ if the result is not negative. (See Table 2.1)                                                                                                                                                                                                      |

| 6   | Zero            | SET = 1 if the result of certain operations are zero, RESET = $\emptyset$ if the result is not zero. (See Table 2.1)                                                                                                                                                                                                              |

| 5   | _               | Not used.                                                                                                                                                                                                                                                                                                                         |

| 4   | Half Carry      | Indicates whether there has been a carry from Bit 3 (Add operations), borrow from Bit 4 (Subtract operations) or if the Low Order half byte of the result of an operation has a value greater than 1001, i.e. is invalid for Binary Coded Decimal purposes. (See Table 2.3)                                                       |

| 3   | —               | Not used.                                                                                                                                                                                                                                                                                                                         |

| 2   | Parity/Overflow | A dual-purpose flag. When used to<br>indicate Parity, it is SET = 1, for Even<br>Parity and RESET = $\emptyset$ for Odd Parity.<br>When used to indicate Overflow it is<br>SET = 1 if the result of an arithmetic<br>operation is too large to be contained<br>in 8 Bits (or 16 Bits for Two Byte<br>operations). (See Table 2.4) |

| 1   | Subtract        | SET = 1 if the instruction was a Subtract operation, RESET = $\emptyset$ if the instruction was an Add Operation.                                                                                                                                                                                                                 |

| Ø   | Carry           | Indicates whether there has been a<br>Carry or Borrow during Arithmetic<br>operations and can be SET or RESET<br>by certain Shift and Rotate<br>operations. (See Table 2.5)                                                                                                                                                       |

Table 2.1 — Sign Flag

| Instruction<br>Group<br>(See Ch.4)                     | Instructions                                                                               | Effect                                                                                      |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Single Byte<br>Load Group                              | LD A,I                                                                                     | SET = 1 if the I Register is negative, otherwise RESET = $\emptyset$ .                      |

| Exchange,<br>Block<br>Transfer<br>and Search<br>Group. | CPI<br>CPIR<br>CPD<br>CPDR                                                                 | SET = 1 if the result is negative, otherwise RESET = $\emptyset$ .                          |

| Single Byte<br>Arithmetic<br>Group                     | ADC A,s<br>ADD A,s<br>AND s<br>CP s<br>DEC s<br>INC s<br>OR s<br>SBC A,s<br>SUB s<br>XOR s | SET = 1 if the result is negative, otherwise RESET = $\emptyset$ .                          |

| Two Byte<br>Arithmetic<br>Group.                       | ADC HL,rr<br>SBC HL,rr                                                                     | SET = 1 if the result is negative, otherwise RESET = $\emptyset$ .                          |

| General<br>Purpose<br>Arithmetic<br>and C.P.U.         | DAA                                                                                        | SET = 1 if the most significant bit of the Accumulator = 1, otherwise RESET = $\emptyset$ . |

| Control<br>Group                                       | NEG                                                                                        | SET = 1 if the result is negative, otherwise RESET = $\emptyset$ .                          |

b represents a specified Bit. r represents a specified Register. s represents a specified Operand.

rr represents a specified Register Pair.

| Rotate and<br>Shift<br>Group                   | RL s<br>RR s<br>RLC s<br>RRC s<br>SLA s<br>SRA s<br>SRL s<br>RLD<br>RRD | SET = 1 if the result is negative,<br>otherwise RESET = $\emptyset$ .<br>SET = 1 if the Accumulator is<br>negative after the shift,<br>otherwise RESET = $\emptyset$ . |

|------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Set,<br>Reset and<br>Test (Flag)<br>Group. | BIT b,r                                                                 | Unknown                                                                                                                                                                |

| Input and<br>Output<br>Group                   | IN R,(C)<br>IND<br>INDR<br>INI<br>INIR<br>OTDR<br>OTIR<br>OUTD<br>OUTI  | SET = 1 if the input data is<br>negative, otherwise RESET = $\emptyset$ .<br>Unknown                                                                                   |

NOTES: b represents a specified Bit. r represents a specified Register. s represents a specified Operand. rr represents a specified Register Pair.

Table 2.2 — Zero Flag

| Instruction<br>Group<br>(See Ch. 4)                                | Instructions                                                                      | Effect                                                                                                                               |

|--------------------------------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| Single Byte<br>Load Group                                          | LD A,I                                                                            | SET = 1 if I Register = $\emptyset$ , otherwise<br>RESET = $\emptyset$ .                                                             |

|                                                                    | LD A,R                                                                            | SET = 1 if the R Register = $\emptyset$ , otherwise RESET = $\emptyset$ .                                                            |

| Exchange,<br>Block<br>Transfer<br>and Search<br>Group              | CPD<br>CPI<br>CPDR<br>CPIR                                                        | SET = 1 if the contents of the<br>Accumulator = the contents of the<br>memory location whose address is<br>held in Register Pair HL. |

| Single Byte<br>Arithmetic<br>Group                                 | ADC A,s<br>ADD A,s<br>CP s<br>DEC s<br>INC s<br>OR s<br>SBC A,s<br>SUB s<br>XOR s | SET = 1 if the result = $\emptyset$ ,<br>otherwise RESET = $\emptyset$ .                                                             |

| Two Byte<br>Arithmetic<br>Group                                    | ADC HL,rr<br>SBC HL,rr                                                            | SET = 1 if the result = $\emptyset$ ,<br>otherwise RESET = $\emptyset$ .                                                             |

| General<br>Purpose<br>Arithmetic<br>and C.P.U.<br>Control<br>Group | DAA<br>NEG                                                                        | SET = 1 if the result = $\emptyset$ ,<br>otherwise RESET = $\emptyset$ .                                                             |

b represents a specified Bit. r represents a specified Register. s represents a specified Operand. rr represents a specified Register Pair.

| Rotate and<br>Shift<br>Group                  | RL s<br>RR s<br>RLD<br>RRD<br>RLC s<br>RRC s<br>SLA s<br>SRA s<br>SRL s        | SET = 1 if the result = $\emptyset$ ,<br>otherwise RESET = $\emptyset$ .                                                                                                                                                                                                                             |

|-----------------------------------------------|--------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit Set,<br>Reset and<br>Test (Flag)<br>Group | BIT b,r                                                                        | SET = 1 if the nominated Bit in<br>the specified Register = $\emptyset$ ,<br>otherwise RESET = $\emptyset$ .                                                                                                                                                                                         |

| Input and<br>Output<br>Group                  | IN r,(C)<br>IND<br>INI<br>INDR<br>INIR<br>OTDR<br>OTDR<br>OTIR<br>OUTD<br>OUTI | SET = 1 if the Input Data = $\emptyset$ ,<br>otherwise RESET = $\emptyset$ .<br>SET = 1 if the contents of Register<br>B - 1 = $\emptyset$ , otherwise RESET = $\emptyset$ .<br>SET = 1.<br>SET = 1.<br>SET = 1 if the contents of Register<br>B - 1 = $\emptyset$ , otherwise RESET = $\emptyset$ . |

NOTES: b represents a specified Bit. r represents a specified Register. s represents a specified Operand. rr represents a specified Register Pair.

# Table 2.3 — Half Carry Flag

| Instruction<br>Group                                  | Instructions                                             | Effect                                                                                       |

|-------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------------------------------------------|

| (See Ch. 4)                                           |                                                          |                                                                                              |

| Single Byte<br>Load Group                             | LD A,I<br>LD A,R                                         | RESET = Ø.                                                                                   |

| Exchange,<br>Block<br>Transfer<br>and Search<br>Group | CPD<br>CPI<br>CPDR<br>CPIR<br>LDD<br>LDI<br>LDDR<br>LDIR | SET = 1 if no Borrow from Bit 4,<br>otherwise RESET = $\emptyset$ .<br>RESET = $\emptyset$ . |

| Single Byte<br>Arithmetic<br>Group                    | ADC A,s<br>ADD A,s<br>INC s                              | SET = 1 if Carry from Bit 3, otherwise RESET = $\emptyset$ .                                 |

|                                                       | CP s<br>DEC s<br>SBC A,s<br>SUB s                        | SET = 1 if no Borrow from Bit 4, otherwise RESET = $\emptyset$                               |

|                                                       | AND s<br>OR s<br>XOR s                                   | SET = 1.                                                                                     |

| Two Byte<br>Arithmetic<br>Group                       | ADC HL,rr<br>ADD HL,rr<br>ADD IX,rr<br>ADD IY,rr         | SET = 1 if Carry from Bit 11, otherwise RESET = $\emptyset$ .                                |

|                                                       | SBC HL,rr                                                | SET = 1 if no Borrow from Bit 12, otherwise RESET = $\emptyset$ .                            |

NOTES:

b represents a specified Bit. r represents a specified Register. s represents a specified Operand. rr represents a specified Register Pair.

| General<br>Purpose<br>Arithmetic    | CCF                                                                                                   | Not affected.                                                    |

|-------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

|                                     | CPL                                                                                                   | SET = 1.                                                         |

| and C.P.U.<br>Control               | DAA                                                                                                   | Not known.                                                       |

| Group                               | NEG                                                                                                   | SET = 1 if no borrow from Bit 4, otherwise RESET = $\emptyset$ . |

|                                     | SCF                                                                                                   | RESET = Ø.                                                       |

| Rotate and<br>Shift<br>Group        | RL s<br>RR s<br>RLA<br>RLD<br>RRA<br>RRD<br>RLC s<br>RRC s<br>RLCA<br>RRCA<br>SLA s<br>SRA s<br>SRL s | RESET = Ø.                                                       |

| Bit Set,<br>Reset and<br>Test Group | BIT r,s                                                                                               | SET = 1.                                                         |

| Input and<br>Output<br>Group        | IN r,(C)<br>IND<br>INI<br>INDR<br>INIR<br>OTDR<br>OTIR<br>OUTD<br>OUTI                                | RESET = Ø.<br>Not known.                                         |

b represents a specified Bit. r represents a specified Register. s represents a specified Operand. rr represents a specified Register Pair.

| Instruction<br>Group<br>(See Ch. 4)                   | Instructions                                   | Effect                                                                                                |

|-------------------------------------------------------|------------------------------------------------|-------------------------------------------------------------------------------------------------------|

| Single Byte<br>Load Group                             | LD A,I<br>LD A,R                               | Set equal to the contents of IFF2.                                                                    |

| Exchange,<br>Block<br>Transfer<br>and Search<br>Group | CPD<br>CPI<br>CPDR<br>CPIR<br>LDD<br>LDI       | SET = 1 if the new contents of<br>Register Pair BC = $\emptyset$ , otherwise<br>RESET = $\emptyset$ . |

|                                                       | LDDR<br>LDIR                                   | RESET = Ø.                                                                                            |

| Single Byte<br>Arithmetic<br>Group                    | ADC A,s<br>ADD A,s<br>CP s<br>SBC A,s<br>SUB s | SET = 1 if Overflow, otherwise RESET = $\emptyset$ .                                                  |

|                                                       | AND s<br>OR s<br>XOR s                         | SET = 1 for Parity Even, RESET = $\emptyset$ for Parity Odd.                                          |

|                                                       | DEC s                                          | SET = 1 if operand was $8\emptyset$ (Hex.)<br>before decrement, otherwise<br>RESET = $\emptyset$ .    |

|                                                       | INC s                                          | SET = 1 if Operand was 7F(Hex.)<br>before increment, otherwise<br>RESET = $\emptyset$ .               |

| Two Byte<br>Arithmetic<br>Group                       | ADC HL,rr<br>SBC HL,rr                         | SET = 1 if Overflow, otherwise RESET = $\emptyset$ .                                                  |

# Table 2.4 — Parity/Overflow Flag

#### NOTES:

b represents a specified Bit. r represents a specified Register. s represents a specified Operand. rr represents a specified Register Pair.

| General<br>Purpose<br>Arithmetic<br>and C.P.U.<br>Control<br>Group | DAA<br>NEG                                                              | SET = 1 if the Accumulator is<br>Parity Even, otherwise RESET = $\emptyset$ .<br>SET = 1 if the Accumulator contents<br>= $8\emptyset$ (Hex.) before negate,<br>otherwise RESET = $\emptyset$ . |

|--------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rotate and<br>Shift<br>Group                                       | RL s<br>RR s<br>RLD<br>RRD<br>RLC s<br>RRC s<br>SLA s<br>SRA s<br>SRL s | SET = 1 for Parity Even, RESET<br>= Ø for Parity Odd.                                                                                                                                           |

| Bit Set,<br>Reset and<br>Test Group                                | BIT b,r                                                                 | Not known.                                                                                                                                                                                      |

| Input and<br>Output<br>Group                                       | IN r,(C)<br>IND<br>INI<br>INDR<br>INIR<br>OTDR<br>OTIR<br>OUTD<br>OUTI  | SET = 1 for Parity Even,<br>RESET = Ø for Parity Odd.<br>Not known                                                                                                                              |

represents a specified Bit. r represents a specified Register. s represents a specified Operand. rr represents a specified Register Pair.

|                                                                    | 1                                                                      |                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Instruction<br>Group<br>(See Ch. 4)                                | Instructions                                                           | Effect                                                                                                                                                                                                                                                                                                                                                      |

| Single Byte<br>Arithmetic<br>Group                                 | ADC A s<br>ADD A,s<br>CP s<br>SBC s<br>SUB s<br>AND s<br>OR s<br>XOR s | SET = 1 if Carry from Bit 7,<br>otherwise RESET = $\emptyset$ .<br>SET = 1 if no Borrow,<br>otherwise RESET = $\emptyset$ .<br>RESET = $\emptyset$ .                                                                                                                                                                                                        |

| Two Byte<br>Arithmetic<br>Group                                    | ADC HL,rr<br>ADD HL,rr<br>ADD IX,rr<br>ADD IY,rr<br>SBC HL,rr          | SET = 1 if Carry from Bit 15,<br>otherwise RESET = $\emptyset$ .<br>SET = 1 if no Borrow, otherwise<br>RESET = $\emptyset$ .                                                                                                                                                                                                                                |

| General<br>Purpose<br>Arithmetic<br>and C.P.U.<br>Control<br>Group | CCF<br>DAA<br>NEG<br>SCF                                               | SET = 1 if the C (Carry) Flag<br>= $\emptyset$ before the instruction,<br>otherwise RESET = $\emptyset$ .<br>SET = 1 if Binary Coded Decimal<br>(BCD) carry, otherwise RESET = $\emptyset$ .<br>SET = 1 if the contents of the<br>Accumulator = $\emptyset\emptyset(\text{Hex.})$ before<br>the instruction, otherwise<br>RESET = $\emptyset$ .<br>SET = 1. |

Table 2.5 — Carry Flag

b represents a specified Bit. r represents a specified Register. s represents a specified Operand

s represents a specified Operand. rr represents a specified Register Pair.

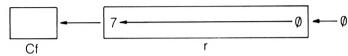

| SI | otate and<br>hift<br>roup | RL s<br>RLC s<br>SLA s          | Set from Bit 7 of the Operand.               |

|----|---------------------------|---------------------------------|----------------------------------------------|

|    |                           | RR s<br>RRC s<br>SRA s<br>SRL s | Set from Bit Ø of the Operand.               |

|    |                           | RLA<br>RLCA                     | Set from Bit 7 of the Accumulator.           |

|    |                           | RRA<br>RRCA                     | Set from Bit $\emptyset$ of the Accumulator. |

b represents a specified Bit. r represents a specified Register. s represents a specified Operand. rr represents a specified Register Pair.

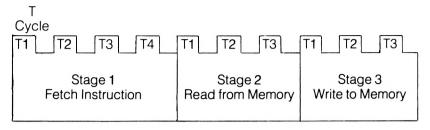

# CHAPTER 3 Timing

The execution of instructions within the Z80 requires time which is measured in cycles. There are two types of cycle - the clock or time cycles, known as T Cycles, and a longer machine cycle, referred to as the M Cycle. T Cycles are always of the same length, and indicate the time taken for the 'clock' which is used to co-ordinate the actions of the Z80 to 'tick' once. They are the fundamental unit of time for the processor. Machine cycles are more abstract, each one representing the time taken for the Z80 to perform one particular action, such as fetching a program instruction, or writing a byte to memory. Because they can represent different actions, M Cycles can take varying amounts of time, from 3 to 6 T states (Note: this is simply another term for a T cycle). To find the actual time taken by an instruction, divide the number of T states taken by the clock rate being used. Thus, if an instruction taken 11 T states, and the Z80 is being run at 2 megahertz, the instruction will take 5.5 microseconds to execute. If a 2 MHz. clock is used to control the Z80 (as is assumed throughout this book), each T cycle will take Ø.5 microseconds to complete.

NOTE: A 4 MHz. clock will reduce the completion time of one T cycle to  $\emptyset.25$  microseconds but will not necessarily halve the time required to execute any given instruction, as it may not be possible to fetch instructions and data from the memory twice as fast as they were previously being fetched.

Since the time required to execute a given instruction, or follow a loop or subroutine, can be crucial to the design and efficient running of a program, full details of the number of M and T cycles, and the processing time in microseconds (assuming a 2 MHz. clock) are given for each individual instruction code in chapter 5. Note that some conditional instructions will not always take the same amount of time to execute. Where two execution times are shown, one is for the case in which the condition is met, and the other is for the case in which the condition is not met. For instance, the instruction JR Z,1000 will take 12 T states if the zero flag is set, and the jump is performed, whereas it will take 7 T states if the zero flag is not set, and the jump is not performed.

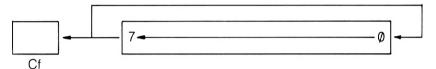

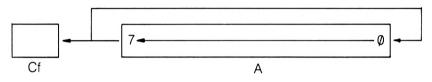

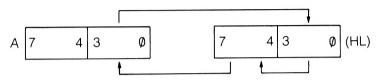

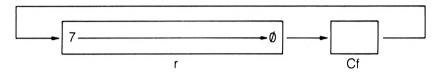

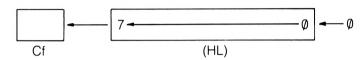

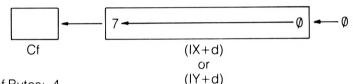

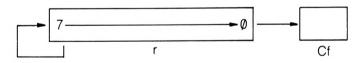

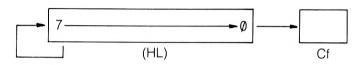

Each instruction can be considered as executing in three stages;

- fetch the instruction

- where appropriate, read from the memory

- where appropriate, write to the memory, e.g.

During stage 1 the instruction will be fetched and decoded, then any necessary processing carried out within the C.P.U. If the instruction requires a memory read, this will take place during stage 2 and, similarly, any memory write activity takes place during stage 3.

# **CHAPTER 4**

# **Instruction Groups**

Full details of each instruction are given in Chapter 5. However, for convenience of programming, these can be considered under a number of separate groups, each related to a specific function or activity. These Groups are:

- 1. Single Byte (8 Bit) Load Group.

- 2. Two Byte (16 Bit) Load Group.

- 3. Exchange, Block Transfer and Search Group.

- 4. Single Byte (8 Bit) Arithmetic Group.

- 5. Two Byte (16 Bit) Arithmetic Group.

- 6. Logical Group.

- 7. General Purpose Arithmetic and C.P.U. Control Group.

- 8. Rotate and Shift Group.

- 9. Bit Set, Reset and Test (Flag) Group.

- 10. Jump, Call (Subroutine) and Return Group.

- 11. Input and Output Group.

The following pages give a brief description of each transaction within each of these groups, each transaction being cross-referenced to full details in Chapter 5.

# 1. Single Byte (8 Bit) Load Group

| SOURCE                                                                                 | OBJECT                                                                               |                                                                                         |        |     | +L/    | AGS         |     |     | NO.<br>OF | M           | TIMING              | μSEC @          |                                                                                                                                                          | CH S                                                 |

|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------|-----|--------|-------------|-----|-----|-----------|-------------|---------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| SOURCE<br>CODE                                                                         | CODE (HEX)                                                                           | DECIMAL                                                                                 | s      | Z   | н      | P/V         | N   | С   |           | CYCLES      | STATES              | 2MHZ            | COMMENTS                                                                                                                                                 | REF                                                  |

| Dir                                                                                    | Dependent on<br>r(Bits 5 4 3) ar<br>01 ← r →← t <sup>1</sup> →<br>(Binary)           | value of<br>dr (B4s2 1.0)                                                               | N      | Ν   | N      | N           | Ν   | N   | 1         | 1           | 4                   | 2               | r and r'<br>represent<br>Registers A.B.<br>C.D.E.H or L.<br>r and r' Bit<br>Patternis<br>A 111<br>B 000<br>C - 001<br>D 010<br>E 011<br>H 100<br>L - 101 | 189<br>189<br>189<br>189<br>189<br>189<br>189        |

| Dr.n<br>r A                                                                            | 3E n                                                                                 | 062 n                                                                                   | N      | N   | N      | N           | N   | N   | 2         | 2           | 7                   | 3.5             |                                                                                                                                                          | 188                                                  |

| r - B<br>r = C<br>r - D<br>r - E<br>r = H<br>r = L                                     | 06 n<br><b>0E n</b><br>16 n<br>1E n<br>26 n<br>2E n                                  | 006 n<br>014 n<br>022 n<br>030 n<br>038 n<br>046 n                                      |        |     |        |             |     |     |           |             |                     |                 |                                                                                                                                                          | 188<br>188<br>188<br>188<br>188                      |

| .Dr. (HL)<br>r = A<br>r = B<br>r = C<br>r = D<br>r = E<br>r = H                        | 7E<br>46<br><b>4E</b><br>56<br>5E<br>66<br>6F                                        | 126<br>070<br>078<br>086<br>094<br>102                                                  | N      | Ν   | N      | N           | Ν   | N   | 1         | 2           | 7                   | 35              |                                                                                                                                                          | 191<br>191<br>191<br>191<br>191<br>191<br>191        |

| r = L<br>.D r, (IX + d)<br>r = A<br>r = B<br>r = C<br>r = D<br>r = E<br>r = H<br>r = L | DD 7E d<br>DD 46 d<br>DD 46 d<br>DD 56 d<br>DD 56 d<br>DD 5E d<br>DD 66 d<br>DD 66 d | 221 126 d<br>221 070 d<br>221 078 d<br>221 086 d<br>221 094 d<br>221 102 d<br>221 110 d | N      | и   | Ν      | Ν           | Ν   | N   | 3         | 5           | 19                  | 9.5             |                                                                                                                                                          | 190<br>190<br>190<br>190<br>190<br>190<br>190        |

| Dr. (IY + d)<br>r = A<br>r = B<br>r = C<br>r = D<br>r = E<br>r = H<br>r = L            | FD 7E d<br>FD 46 d<br>FD 4E d<br>FD 56 d<br>FD 5E d<br>FD 66 d<br>FD 6E d            | 253 126 d<br>253 070 d<br>253 078 d<br>253 086 d<br>253 094 d<br>253 102 d<br>253 110 d | Ν      | z   | N      | N           | Ν   | N   | 3         | 5           | 19                  | 95              |                                                                                                                                                          | 190<br>190<br>190<br>190<br>190<br>190<br>190        |

| D(HL).r<br>r = A<br>r = B<br>r = C<br>r = D<br>r = E<br>r = H<br>r = L                 | 77<br>70<br>71<br>72<br>73<br>74<br>75                                               | 119<br>112<br>113<br>114<br>115<br>116<br>117                                           | N      | N   | N      | N           | N   | N   | 1         | 2           | 7                   | 3.5             |                                                                                                                                                          | 212<br>212<br>212<br>212<br>212<br>212<br>212<br>212 |

| D (IX + d), r<br>r = A<br>r = B<br>r = C<br>r = D<br>r = E<br>r = H<br>r = L           | DD 77 d<br>DD 70 d<br>DD 71 d<br>DD 72 d<br>DD 73 d<br>DD 74 d<br>DD 75 d            | 221 119 d<br>221 112 d<br>221 113 d<br>221 114 d<br>221 115 d<br>221 116 d<br>221 117 d | N      | 2   | N      | N           | Ν   | N   | 3         | 5           | 19                  | 9.5             |                                                                                                                                                          | 215<br>215<br>215<br>215<br>215<br>215<br>215<br>215 |

| LD (IY + d), r<br>r = A<br>r = B<br>r = C<br>r = D<br>r = E<br>r = H<br>r = L          | FD 77 d<br>FD 70 d<br>FD 71 d<br>FD 72 d<br>FD 73 d<br>FD 74 d<br>FD 75 d            | 253 119 d<br>253 112 d<br>253 113 d<br>253 114 d<br>253 115 d<br>253 116 d<br>253 117 d | N      | N   | N      | N           | N   | N   | 3         | 5           | 19                  | 95              |                                                                                                                                                          | 215<br>215<br>215<br>215<br>215<br>215<br>215        |

| LD (HL), n<br>LD (IX + d), n<br>LD (IY + d), n                                         | 36 n<br>DD 36 d n<br>FD 36 d n                                                       | 054 n<br>221 054 d n<br>253 054 d n                                                     | N N N  | ZZZ | N N N  | N<br>N<br>N | NNN | ZZZ | 2 4 4     | 3<br>5<br>5 | 10<br>19<br>19<br>7 | 5<br>9.5<br>9.5 |                                                                                                                                                          | 21<br>21<br>21<br>18                                 |

| LD A. (BC)<br>LD A. (DE)                                                               | 0A<br>1A                                                                             | 010<br>026                                                                              | N<br>N | NN  | N<br>N | N<br>N      | N   | N   | 1         | 2           | 7                   | 3.5<br>3.5      |                                                                                                                                                          | 18                                                   |

#### SINGLE BYTE (8 BIT) LOAD GROUP TABLE (cont.)

|                |                      | FLAGS    |   |   |   |     |   | NO. | TIMING      |             |             |                |          |              |

|----------------|----------------------|----------|---|---|---|-----|---|-----|-------------|-------------|-------------|----------------|----------|--------------|

| SOURCE<br>CODE | OBJECT<br>CODE (HEX) | DECIMAL  | s | z | н | PIV | N | с   | OF<br>BYTES | M<br>CYCLES | T<br>STATES | µSEC @<br>2MHZ | COMMENTS | CH.5<br>REF. |

| LDA, (nn)      | 3Ann                 | 050 n n  | N | N | N | N   | N | N   | 3           | 4           | 13          | 6.5            |          | 185          |

| LD (BC), A     | 02                   | 002      | N | N | N | N   | N | N   | 1           | 2           | 7           | 3.5            |          | 210          |

| LD (DE), A     | 12                   | 018      | N | N | N | N   | N | N   | 1           | 2           | 7           | 3.5            |          | 210          |

| LD (nn), A     | 32 n n               | 050 n n  | N | N | N | N   | N | N   | 3           | 4           | 13          | 6.5            |          | 205          |

| LDA.I          | ED 57                | 237 087  | • | • | 0 | IFF | Ø | N   | 2           | 2           | 9           | 4.5            |          | 183          |

| LDA, R         | ED 5F                | 237 095  | • | • | 0 | IFF | 0 | N   | 2           | 2           | 9           | 4.5            |          | 184          |

| LDI, A         | ED47                 | 237 07 1 | N | N | N | N   | N | N   | 2           | 2           | 9           | 4.5            |          | 195          |

| LDR, A         | ED4F                 | 237 079  | N | N | N | N   | N | N   | 2           | 2           | 9           | 4.5            |          | 196          |

FLAG KEY: N - Not affected

0 - RESET = 0. 1 - SET = 1.

- Unknown.

- Affected according to the result

IFF - Content of Interrupt Flip Flop 2 copied into flag.

LD r.r'

Where:

Chapter 5, Page 189

r and r' represent any of the C.P.U. registers A, B, C, D, E, H or L.

This instruction simply loads the contents of the r' register into the r register, leaving the contents of the r' register untouched.

LD r,n

Chapter 5, Page 188

Chapter 5, Page 191

Where:

r represents any of the C.P.U. registers A, B, C, D, E, H or L. n is an 8-bit value, specified in the instruction.

This instruction loads the 8-bit value n into the register r.

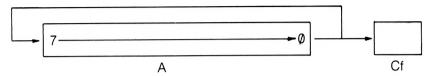

LD r,(HL)

Where:

r represents any of the C.P.U. registers A, B, C, D, E, H or L.

This loads the contents of a memory location, identified by the contents of register pair HL, into the register r, leaving the contents of both the memory location and register pair HL untouched.

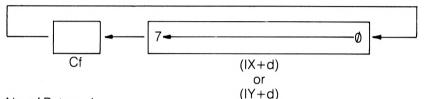

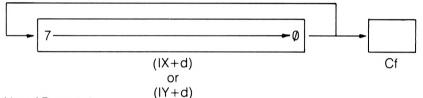

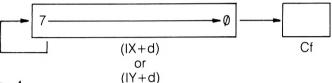

LD r,(IX + d)Where:

Chapter 5, Page 193

r represents any of the C.P.U. registers A, B, C, D, E, H or L. d is the displacement, in Bytes, from the location identified by the contents of Index Register IX.

This loads the contents of a memory location, identified by the contents of Index Register IX (modified by displacement d, which is specified in the instruction), into the register r, leaving the contents of both the memory location and Index Register IX untouched.

LD r, (IY + d)

Chapter 5, Page 193

Where:

r represents any of the C.P.U. registers, A, B, C, D, E, H or L.

d is the displacement, in Bytes, from the location indentified by the contents of the Index Register IY.

This loads the contents of a memory location, identified by the contents of Index Register IY (modified by displacement d, which is specified in the instruction), into the register r, leaving the contents of both the memory location and Index Register IY untouched.

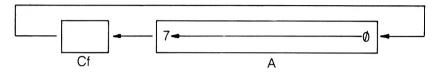

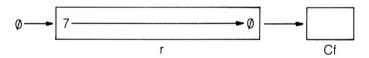

LD (HL), r

Chapter 5, Page 212

Where:

r represents any of the C.P.U. registers, A, B, C, D, E, H or L.

This loads the contents of register r into a memory location which is identified by the contents of Register Pair HL. The contents of Register Pair HL remain untouched.

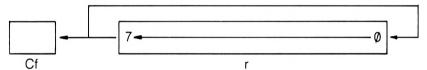

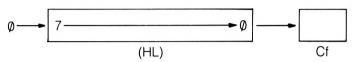

LD(IX + d),rWhere: Chapter 5, Page 215

r represents any of the C.P.U. registers A, B, C, D, E, H or L. d is the displacement, in Bytes, from the location identified by the contents of Index Register IX.

This loads the contents of register r into a memory location, which is identified by the contents of Index Register IX (modified by displacement d, which is specified in the instruction). The contents of Index Register IX remain unaltered.

LD (IY + d),r Where: Chapter 5, Page 215

r represents any of the C.P.U. registers A, B, C, D, E, H or L. d is the displacement, in Bytes, from the location identified by the contents of Index Register IY.

This loads the contents of register r into a memory location, which is identified by the contents of Index Register IY (modified by displacement d, which is specified in the instruction). The contents of Index Register IY remain unaltered.

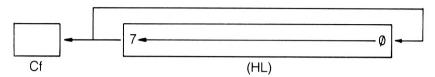

LD (HL),n

Chapter 5, Page 211

Where:

n is an 8-bit value, specified in the instruction.

Loads the value n into a memory location identified by the contents of Register Pair HL.

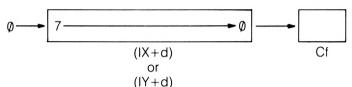

LD(IX + d),n

Where:

n is an 8-bit value, specified in the instruction.

d is the displacement, in Bytes, from the location identified by the contents of Index Register IX.

Loads the value n into a memory location, identified by the contents of Index Register IX (modified by displacement d, which is specified in the instruction).

LD(IY + d),n

Chapter 5, Page 214

Where:

n is an 8-bit value, specified in the instruction.

d is the displacement, in Bytes, from the location identified by the contents of Index Register IY.

Loads the value n into a memory location, identified by the contents of Index Register IY (modified by displacement d, which is specified in the instruction).

LD A, (BC)

Chapter 5, Page 186

Loads the contents of a memory location, specified by the contents of Register Pair BC, into the Accumulator, leaving the contents of the memory location untouched.

LD A, (DE)

Chapter 5, Page 187

Loads the contents of a memory location, identified by the contents of Register Pair DE, into the Accumulator, leaving the contents of the memory location unaltered.

LD A, (nn)

Chapter 5, Page 185

Where:

nn is a spcific memory location, identified in two bytes of the instruction.

Loads the contents of the specified memory location, nn, into the Accumulator, leaving the contents of location nn unaltered.

# LD (BC), A

Chapter 5, Page 210

Loads the contents of the Accumulator into a memory location identified by the contents of Register Pair BC. The contents of the Accumulator remain unchanged.

# LD (DE),A

Chapter 5, Page 210

Loads the contents of the Accumulator into a memory location identified by the contents of Register Pair DE, leaving the contents of the Accumulator unchanged.

LD (nn),A

Chapter 5, Page 205

Where:

nn is a specific memory location, identified by two bytes of the instruction.

Loads the contents of the Accumulator into the memory location specified in the instruction, leaving the contents of the Accumulator unaltered.

## LD A,I

Chapter 5, Page 183

Loads the contents of the Interrupt Register I into the Accumulator, leaving the contents of Interrupt Register I untouched.

LD A,R Chapter 5, Page 184 Loads the contents of the Refresh Register 'R' into the Accumulator, leaving the contents of Refresh Register R unchanged.

LD I, A Chapter 5, Page 195 Loads the contents of the Accumulator into the Interrupt Register I, leaving the contents of the Accumulator unchanged.

LD R, A Chapter 5, Page 196 Loads the contents of the Accumulator into the Refresher Register R, leaving the contents of the Accumulator unaltered.

# 2. Two Byte (16 Bit) Load Group

| SOURCE<br>CODE                                                                                                                                         | OBJECT<br>CODE (HEX)                         |                                                          |   |   | FL | AGS |   |     | NO.         |             | TIMING      |                |          |                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------|---|---|----|-----|---|-----|-------------|-------------|-------------|----------------|----------|---------------------------------|

|                                                                                                                                                        |                                              | ) DECIMAL                                                | s | z | н  | P/V | N | с   | OF<br>BYTES | M<br>CYCLES | T<br>STATES | μSEC @<br>2MHZ | COMMENTS | CH.<br>REF                      |

| $ \begin{array}{l} \text{LD, dd, nn} \\ \text{dd} = \text{BC} \\ \text{dd} = \text{DE} \\ \text{dd} = \text{HL} \\ \text{dd} = \text{SP} \end{array} $ | 01 nn<br>11 nn<br>21 nn<br>31                | 001<br>017<br>033<br>049                                 | N | N | N  | N   | N | N   | 3           | 3           | 10          | 5              |          | 197<br>197<br>197<br>197        |

| LDIX, nn                                                                                                                                               | DD21nn                                       | 221033nn                                                 | N | N | N  | N   | N | N   | 4           | 4           | 14          | 7              |          | 198                             |

| LDIY, nn                                                                                                                                               | FD21nn                                       | 253 033 n n                                              | N | N | N  | N   | N | N   | 4           | 4           | 14          | 7              |          | 198                             |

| LD dd, (nn)<br>dd = BC<br>dd = DE<br>dd = HL<br>dd = SP                                                                                                | ED 4B nn<br>ED 5B nn<br>ED 6B nn<br>ED 7B nn | 237 075<br>237 091<br>237 107<br>237 123                 | N | И | N  | N   | N | Ν   | 4           | 6           | 20          | 10             |          | 199<br>199<br>199<br>199        |

| LDIX (nn)                                                                                                                                              | DD2Ann                                       | 221042nn                                                 | Ν | N | N  | N   | N | N   | 4           | 6           | 20          | 10             |          | 201                             |

| LDIY, (nn)                                                                                                                                             | FD2Ann                                       | 253042nn                                                 | N | N | N  | N   | N | N   | 4           | 6           | 20          | 10             |          | 201                             |

| LD (nn), dd $dd = BC$ $dd = DE$ $dd = HL$ $dd = SP$                                                                                                    | ED43nn<br>ED53nn<br>ED63nn<br>ED73nn         | 237 067 n n<br>237 083 n n<br>237 099 n n<br>237 115 n n | Ν | И | N  | N   | И | N   | 4           | 6           | 20          | 10             |          | 206<br>206<br>206<br>206        |

| LD (nn), IX                                                                                                                                            | DD 22 nn                                     | 221034nn                                                 | Ν | N | N  | N   | N | N   | 4           | 6           | 20          | 10             |          | 208                             |

| LD (nn), IY                                                                                                                                            | FD22nn                                       | 253 034 n n                                              | N | N | N  | N   | N | N   | 4           | 6           | 20          | 10             |          | 208                             |

| LD SP, HL                                                                                                                                              | F9                                           | 249                                                      | N | N | N  | N   | N | . N | 1           | 1           | 6           | 3              |          | 203                             |

| LD, SP, IX                                                                                                                                             | DD F9                                        | 221249                                                   | Ν | N | N  | N   | N | N   | 2           | 2           | 10          | 5              |          | 204                             |

| LD SP, IY                                                                                                                                              | FDF9                                         | 253249                                                   | N | N | N  | N   | N | N   | 2           | 2           | 10          | 5              |          | 204                             |

| PUSH rr<br>rr = AF<br>rr = BC<br>rr = DE<br>rr = HL                                                                                                    | F5<br>C5<br>D5<br>E5                         | 245<br>197<br>213<br>229                                 | Ν | N | N  | N   | N | N   | 1           | 3           | 11          | 5.5            |          | 246<br>246<br>246<br>246        |

| PUSHIX                                                                                                                                                 | DDE5                                         | 221 229                                                  | N | N | N  | N   | N | N   | 2           | 4           | 15          | 7.5            |          | 248                             |

| PUSHIY                                                                                                                                                 | FDE5                                         | 253 229                                                  | N | N | N  | N   | N | N   | 2           | .4          | 15          | 7.5            |          | 248                             |

| POP rr<br>rr = AF<br>rr = BC<br>rr = DE<br>rr = HL                                                                                                     | F1<br>C1<br>D1<br>E1                         | 241<br>193<br>209<br>225                                 | N | И | N  | N   | И | N   | 1           | 3           | 10          | 5              |          | 242<br>242<br>242<br>242<br>242 |

| POPIX                                                                                                                                                  | DDE1                                         | 221 225                                                  | N | N | N  | N   | N | N   | 2           | 4           | 14          | 7              |          | 244                             |

| POPIY                                                                                                                                                  | FDE1                                         | 253 225                                                  | N | N | N  | N   | N | N   | 2           | 4           | 14          | 7              |          | 244                             |

FLAG KEY N - Not affected. Ø - Reset = Ø. 1 - Set = 1.

Unknown

- Affected according to the result.

IFF - Content of Interrupt Flip Flop copied into flag

LD dd.nn

Where:

Chapter 5, Page 197

dd is any of the register pairs BC, DE, HL or SP. nn is a specific memory location.

Loads the memory location nn into the Register Pair dd.

LD IX.nn

Where:

nn is a specific memory location.

Loads the contents of memory location nn, specified in the instruction, into the Low Order byte of Index Register IX and the contents of memory location nn+1 into the High Order byte of Index Register IX.

Chapter 5, Page 198

Chapter 5, Page 198

Chapter 5, Page 199

nn is a specific memory location.

Loads the contents of the memory location nn, specified in the instruction, into the Low Order byte of Index Register IY and the contents of memory location nn+1 into the High Order byte of Index Register IY.

LD dd.(nn) Where:

> dd is any of the register pairs BC, DE, HL or SP. nn is a specific memory location.

Loads the contents of memory location nn (specified in the instruction) into the Low Order byte of the specified Register Pair and the contents of memory location nn+1 into the High Order byte of the same Register Pair. The contents of both memory locations remain unchanged.

LD IX.(nn)

Chapter 5, Page 201

Where:

nn is a specific memory location.

Loads the contents of memory location nn, which is specified in the instruction, into the Low Order byte of Index Register IX and the contents of memory location nn+1 into the High Order byte of the same register. The contents of both memory locations remain unchanged.

LD IY,(nn) Where:

Chapter 5, Page 201

Chapter 5, Page 206

nn is a specific memory location.

Loads the contents of memory location nn, specified in the instruction, into the Low Order byte of Index Register IY and the contents of memory location nn+1 into the High Order byte of that register, leaving the contents of both memory locations unaltered.

LD (nn).dd

Where:

nn is a specific memory location. dd is any one of the Register Pairs BC, DE, HL or SP.

IDIY.nn

Where:

Loads the contents of the Low Order byte of the nominated Register Pair into memory location nn, and the contents of the High Order byte of the same Register Pair into memory location nn+1. The contents of the Register Pair are not affected.

LD (nn),IX

Chapter 5, Page 208

Where:

nn is a specified memory location.

Loads the contents of the Low Order byte of Index Register IX into memory location nn and the contents of the High Order byte of the same register into memory location nn+1. The contents of Index Register IX remain unchanged.

LD (nn),IY

Chapter 5, Page 208

Where:

nn is a specified memory location.

Loads the contents of the Low Order byte of Index Register IY into memory location nn and the contents of the High Order byte of the same register into memory location nn+1. The Index Register contents are not changed.

LD SP,HL Chapter 5, Page 203 Loads the Stack Pointer with the contents of Register Pair HL, but does not change the contents of Register Pair HL.

LD SP,IX

Chapter 5, Page 204

Loads the Stack Pointer with the contents of Index Register IX, leaving the contents of that register unchanged.

LD SP,IY

Chapter 5, Page 204

Loads the Stack Pointer with the contents of Index register IY, leaving the contents of that register unaltered.

## PUSH rr

Chapter 5, Page 246

Where:

rr is any of the Register Pairs AF, BC, DE or HL.

Pushes the contents of the nominated Register Pair on to the memory stack. The Stack Pointer (SP), which contains the address of the top of the memory stack, is decremented and the High Order byte of the Register Pair is pushed out to that location. The Stack Pointer is again decremented and the Low Order byte of the Register Pair is pushed out to this new location. The contents of the Register Pair are not changed.

# PUSH IX

# Chapter 5, Page 248

Pushes the contents of the Index Register IX on to the memory stack. The Stack Pointer (SP), which contains the address of the top of the memory stack, is decremented and the High Order byte of register IX is pushed out to that location. The Stack Pointer is again decremented and the Low Order byte of Index Register IX is pushed out to the new location. The contents of Index Register IX are not affected.

PUSH IYChapter 5, Page 248Pushes the contents of the Index Register IY on to the memorystack. The Stack Pointer (SP), which contains the address of the top ofthe memory stack, is decremented and the High Order byte of IndexRegister IY is pushed out to that location. The Stack Pointer is againdecremented and the Low Order byte of Index Register IY pushed out tothat new location. The contents of Index Register IY remain unaltered

#### POP rr

#### Chapter 5, Page 242

Where:

#### rr is any of the register pairs AF, BC, DE or HL.

Loads the contents of the memory location identified by the Stack Pointer into the Low Order byte of the nominated Register Pair. The Stack Pointer is then incremented and the contents of the location now identified by the Stack Pointer is loaded into the High Order byte of the same Register Pair. Finally, the Stack Pointer is again incremented.

#### POP IX

## Chapter 5, Page 244

Loads the contents of the memory location identified by the Stack Pointer into the Low Order byte of Index Register IX. The Stack Pointer is then incremented and the contents of this new location loaded into the High Order byte of the IX Index Register. The Stack Pointer is once again incremented.

## POP IY

#### Chapter 5, Page 244

Loads the contents of the memory location identified by the Stack Pointer into the Low Order byte of Index Register IY. The Stack Pointer is then incremented and the contents of that location loaded into the High Order byte of Index Register IY. The Stack Pointer is then incremented once more.

# 3. Exchange, Block Transfer and Search Group

This group of instructions allows the exchange of 16 bit data blocks between register pairs in the same set of registers AND between the two sets of registers. It also includes instructions which transfer data from one block of memory to another and those which search a specified block of memory.

|                |                      |         |   |   | FL | AGS |   |   | NO.         |             | TIMING      |                |                          |              |

|----------------|----------------------|---------|---|---|----|-----|---|---|-------------|-------------|-------------|----------------|--------------------------|--------------|

| SOURCE<br>CODE | OBJECT<br>CODE (HEX) | DECIMAL | s | z | н  | P/V | N | с | OF<br>BYTES | M<br>CYCLES | T<br>STATES | µSEC @<br>2MHZ | COMMENTS                 | CH.5<br>REF. |

| EXDE, HL       | EB                   | 235     | N | N | N  | N   | N | N | 1           | 1           | 4           | 2              |                          | 149          |

| EX AF, AF      | 08                   | 008     | N | N | N  | N   | N | N | 1           | 1           | 4           | 2              |                          | 148          |

| EXX            | D9                   | 217     | N | N | N  | N   | N | N | 1           | 1           | 4           | 2              |                          | 154          |

| EX (SP), HL    | E3                   | 227     | N | N | N  | N   | N | N | 1           | 5           | 19          | 9.5            |                          | 150          |

| EX (SP), IX    | DD E3                | 221 227 | N | N | N  | N   | N | N | 2           | 6           | 23          | 11.5           |                          | 152          |

| EX (SP), IY    | FD E3                | 253 227 | N | N | N  | N   | N | N | 2           | 6           | 23          | 11.5           |                          | 152          |

| LDD            | ED A8                | 237 168 | N | N | 0  |     | 0 | N | 2           | 4           | 16          | 8              |                          | 217          |

| LDDR           | ED B8                | 237 184 | N | N | 0  | 0   | 0 | N | 2           | 5           | 21          | 11.5           | If BC ≠ Ø                | 219          |

|                |                      |         |   |   |    |     |   |   |             | 4           | 16          | 8              | If BC = Ø                |              |

| LDI            | ED A0                | 237 160 | Ν | N | Ø  | •   | 0 | N | 2           | 4           | 16          | 8              |                          | 221          |

| LDIR           | ED B0                | 237 176 | N | N | ø  | ø   | ø | N | 2           | 5           | 21          | 11.5           | If BC ≠ Ø                | 223          |

|                |                      |         |   |   | -  | -   | - |   | -           | 4           | 16          | 8              | If BC = Ø                |              |

| CPD            | ED A9                | 237 169 | • | • | •  | •   | 1 | N | 2           | 4           | 16          | 8              |                          | 129          |

| CPDR           | ED B9                | 237 185 | • | • | •  | •   | 1 | N | 2           | 5           | 21          | 10.5           | If BC ≠ Øand<br>A ≠ (HL) | 130          |

|                |                      |         |   |   |    |     |   |   |             | 4           | 16          | 8              | If BC = Ø or A<br>= (HL) |              |

| CPI            | ED A1                | 237 161 | • | • | •  | •   | 1 | N | 2           | 4           | 16          | 8              |                          | 132          |

| CPIR           | ED B1                | 237 177 | · | • | •  | •   | 1 | N | 2           | 5           | 21          | 10.5           | If BC ≠ Øand<br>A ≠ (HL) | 133          |

|                |                      |         |   |   |    |     |   |   |             | 4           | 16          | 8              | If BC = Ø or A<br>= (HL) |              |

FLAG KEY: N - Not affected. Ø - RESET = Ø. 1 - SET = 1. ? - Unknown.

- Affected according to the result

IFF - Content of Interrupt Flip Flop copied into flag.

### A. Exchange Instructions

FX DE,HL

Chapter 5, Page 149

Exchanges the contents of the DE and HL Register Pairs.

EX AF.AF'

Chapter 5, Page 148

Exchanges the contents of Register Pair AF with Register Pair AF'.

FXX

Chapter 5, Page 154

The contents of Register Pairs BC, DE and HL are exchanged with the contents of Register Pairs BC', DE', and HL' respectively.

# EX (SP),HL

Chapter 5, Page 150

The Low Order byte of Register Pair HL (i.e. the contents of Register L) is exchanged with the contents of the memory location whose address is contained in the Stack Pointer (SP). The High Order byte of Register Pair HL is exchanged with the contents of the next sequential memory location. The contents of the Stack Pointer are not changed.

## EX (SP),IX

Exchanges the Low Order byte of Index Register IX with the memory location whose address is contained in the Stack Pointer (SP) and the High Order byte of that register is exchanged with the next memory location. The contents of the Stack Pointer are not altered.

## EX (SP),IY

Chapter 5, Page 152

Chapter 5, Page 152

The contents of the Low Order byte of Index Register IY are exchanged with the memory location whose address is contained in the Stack Pointer (SP) and the High order byte of the register is exchanged with the next sequential memory location. The contents of the Stack Pointer are not changed.

## B. Transfer Instructions

LDD

Chapter 5, Page 217

Transfers one byte of date from the memory location whose address is held in register Pair HL to the memory location whose address is held in Register Pair DE. Register Pair BC is used as a byte counter. All three register pairs (BC, DE and HL) are then decremented.

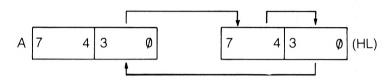

## LDDR

Chapter 5, Page 219

Transfers one byte of data from the memory location whose address is held in Register Pair HL to the memory location whose address is held in Register Pair DE. Register Pair BC is used as a byte counter. The three Register Pairs are then decremented. If Register Pair BC becomes zero, then the instruction is terminated, otherwise the Program Counter is decremented by 2 and the instruction is repeated.

WARNING: If Register Pair BC is initially set to zero, the instruction will loop through all 64K of memory.

LDI

## Chapter 5, Page 221

Transfers one byte of data from the memory location whose address is held in Register Pair HL to the memory location whose address is held in Register Pair DE. Register Pair BC is used as a byte counter. Register Pairs DE and HL are then incremented while Register Pair BC is decremented.

## LDIR

## Chapter 5, Page 223

Transfers one byte of data from the memory location whose address is held in Register Pair HL to the memory location whose address is held in Register Pair DE. Register Pair BC is used as a byte counter. Register Pairs DE and HL are then incremented while Register Pair BC is decremented. If Register Pair BC becomes zero then the instruction is terminated, otherwise the Program Counter (PC) is decremented by 2 and the instruction is repeated.

WARNING: If Register Pair BC is initially set to zero, the instruction will loop through 64K of memory.

## 6. Search Instructions

## CPD

Chapter 5, Page 129 Compares the contents of the Accumulator with the contents of the memory location whose address is contained in Register Pair HL. If the contents match Condition Flag Z is set, otherwise it is reset. The contents of Register Pair HL are decremented as are the contents of Register Pair BC (used as a byte counter).

## CPDR

Chapter 5, Page 130 Compares the contents of the Accumulator with the contents of the memory location whose address is contained in Register Pair HL. If the contents match Condition Flag Z is set, otherwise it is reset. The contents of both Register Pair HL and Register Pair BC (used as a byte counter) are decremented. If either a match has been achieved, or the new value of Register Pair BC is zero, the instruction is terminated. If neither of these conditions are met the Program Counter (PC) is decremented by 2 and the instruction is repeated.

NOTE: Execution of this instruction increments the Program Counter (PC) by 2, therefore failure of the tests returns the Program Counter to the start of the CPDR instruction.

WARNING: If Register Pair BC is initialised to zero, this instruction will loop until either a match is found or it has cycled through all 64K of memory. It can therefore be used to test all 64K of memory.

### CPI

Chapter 5, Page 132

Compares the contents of the Accumulator with the contents of the memory location whose address is contained in Register Pair HL. If the conditons match Condition Flag Z is set, otherwise it is reset. The contents of Register Pair HL are incremented while the contents of Register Pair BC (used as a byte counter) are decremented.

### CPIR

Chapter 5, Page 133

Compares the contents of the Accumulator with the contents of the memory location whose address is contained in Register Pair HL. If the contents match, then Condition Flag Z is set, otherwise it is reset. The contents of Register Pair HL are incremented while the contents of Register Pair BC (used as a byte counter) are decremented. If either a match has been achieved, or the new value of Register Pair BC is zero. the instruction is terminated. If neither of these conditions are met the Program Counter (PC) is decremented by 2 and the instruction is repeated.

NOTE: Execution of this instruction increments the Program Counter (PC) by 2, therefore failure of both tests returns the Program Counter to the start of the CPIR instruction.

WARNING: If Register Pair BC is initialised to zero, this instruction will loop through until either a match is found or it has cycled through all 64K of memory. It can be used to test the entire memory.

# 4. Single Byte (8 Bit) Arithmetic Group

SINGLE BYTE (8 BIT) ARITHMETIC GROUP TABLE

| 000000               | 00/507               |                    |   | 1 | FL/ | AGS |     |     | NO.         |             | TIMING | USEC C         | 1                  | CF  |

|----------------------|----------------------|--------------------|---|---|-----|-----|-----|-----|-------------|-------------|--------|----------------|--------------------|-----|

| SOURCE<br>CODE       | OBJECT<br>CODE (HEX) | DECIMAL            | S | z | н   | P/V | N   | с   | OF<br>BYTES | M<br>CYCLES |        | µSEC @<br>2MHZ | COMMENTS           | RE  |

| NDC A, n             | CEn                  | 206                | • | • | •   | V   | 0   | •   | 2           | 2           | 7      | 3.5            | Adds with<br>Carry | 7   |

| DC A, r              |                      |                    |   |   | •   | v   | 0   |     | 1           | 1           | 4      | 2              | Adds with          |     |

| r = A                | 8F                   | 143                |   |   |     |     |     |     |             |             |        |                | Carry              | 7   |

| r = B                | 88                   | 136                |   |   |     |     |     |     |             |             |        |                |                    | 7   |

| r = C                | 89                   | 137                |   |   |     |     |     |     |             |             |        |                |                    | 7   |

| r = D                | 8A                   | 138                |   |   |     |     | 1   |     |             |             |        |                |                    | 7   |

| r = E                | 8B                   | 139                |   |   |     |     |     |     |             |             |        |                |                    | 7   |

| r = H                | 8C                   | 140                |   |   |     |     |     |     |             |             |        |                |                    | 7   |

| r = L                | 8D                   | 141                |   |   |     |     |     |     |             |             |        |                |                    | 7   |

| DCA, (HL)            | 8E                   | 142                | • |   | •   | V   | 0   | · · | 1           | 2           | 7      | 3.5            |                    | 7   |

| DC A, $(IX + d)$     | DD 8E d              | 221 142 d          |   |   | •   | V   | 0   |     | 3           | 5           | 19     | 9.5            |                    | 7   |

| DC A, (IY + d)       | FD 8E d              | 253 142 d          |   |   |     | v   | 0   |     | 3           | 5           | 19     | 9.5            |                    | 7   |

| DDA, n               | C6n                  | 198 n              |   |   |     | v   | ø   | 1 . | 2           | 2           | 7      | 3.5            |                    | 8   |

|                      | Con                  | 19611              |   |   |     |     | -   |     | -           |             | 4      | 2              |                    |     |

| DD A.r               | 07                   | 105                |   | 1 |     | V   | 0   |     | 1           | 1           | 4      | 2              |                    | 8   |

| r = A<br>r = B       | 87<br>80             | 135<br>128         |   |   |     |     |     |     |             |             |        |                |                    | 8   |

| r = C                | 81                   | 120                |   |   |     |     |     |     |             |             |        |                |                    | 8   |