# MACHINE CODE FOR BEGINNERS ON THE AMSTRAD

Steve Kramer

## Machine Code for Beginners on the Amstrad

# Machine Code for Beginners on the Amstrad

**Steve Kramer**

First published in 1984 in the United Kingdom by Micro Press Castle House 27 London Road Tunbridge Wells, Kent

Reprinted 1985 (twice)

© Steve Kramer 1984

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, recording or otherwise, for commercial gain, without the prior permission of the publishers.

ISBN 0 7447 0025 6

Amstrad and CPC 464 are trademarks of Amstrad Consumer Electronics PLC

Printed and bound in Great Britain by MACKAYS OF CHATHAM LTD

## Contents

| Chapter 1  | Introduction                                                                                                                 | 1   |

|------------|------------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 2  | What is Machine Code and Why Use It?                                                                                         | 3   |

| Chapter 3  | First Concepts<br>Hex Binary Assemblers and Mnemonics                                                                        | 8   |

| Chapter 4  | Flow Charts                                                                                                                  | 15  |

| Chapter 5  | Simple Machine Code Instructions<br>LD, CALL, RET, JP, JR                                                                    | 18  |

| Chapter 6  | Simple Maths<br>ADD, ADC, SUB, SBC, DEC, INC                                                                                 | 44  |

| Chapter 7  | Flags, Conditions and Decision Making<br>CP, Z, NZ, C, NC, M, P, PE, PO, CCF,<br>SCF, DJNZ                                   | 68  |

| Chapter 8  | Logical Operations<br>AND, OR, XOR, CPL, NEG                                                                                 | 83  |

| Chapter 9  | Using the Machine Stack<br>PUSH, POP and instructions with SP                                                                | 92  |

| Chapter 10 | Using Instructions that Work on a Single Bit<br>SET, RES, BIT                                                                | 102 |

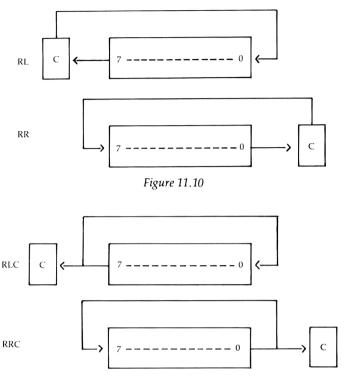

| Chapter 11 | Rotates and Shifts, Multiplication and<br>Division<br>RL, RLA, RLC, RLCA, RLD, SLA, SLL<br>RR, RRA, RRC, RRCA, RRD, SRA, SRL | 109 |

| Chapter 12 | Automated Moves and Searches<br>LDD, LDDR, CPD, CPDR<br>LDI, LDIR, CPI, CPIR                                           | 129 |

|------------|------------------------------------------------------------------------------------------------------------------------|-----|

| Chapter 13 | Communicating with the Outside World<br>IN and OUT                                                                     | 141 |

| Chapter 14 | Other Instructions, Indexed Addressing<br>with the IX and IY Registers                                                 | 145 |

| Chapter 15 | Programming Hints, and Using the Firmware<br>(How to Use Some of the More Useful<br>Functions of the Operating System) | 159 |

| Appendices | A The Z80 Instruction Set Courtesy ZILOG                                                                               |     |

|            | Inc.                                                                                                                   | 164 |

|            | B Hex Loader                                                                                                           | 172 |

|            | C Hex to Decimal Conversions MSB                                                                                       | 174 |

|            | D Hex to Decimal Conversions LSB                                                                                       |     |

|            | and Binary Nibbles                                                                                                     | 175 |

|            | E Twos Complement Conversions                                                                                          | 176 |

|            | F Screen Map and Bit Map for Pixels                                                                                    | 178 |

|            | G Useful Call Addresses                                                                                                | 181 |

### Acknowledgements

With thanks to Bob and Carol for their pertinent questions, and to Marcia for the cup of coffee.

Steve Kramer, 1984

Since this book was written before the disk drive and its associated interface were available, for some of the listings to operate correctly, it may be necessary for the disk interface to be either disconnected or the disk drive not to have been turned on.

#### Chapter One

## Introduction

The Amstrad CPC 464 is perhaps the most exciting new computer to appear since the Sinclair Spectrum. It offers many advanced features from Basic which could previously only be accomplished by vastly more expensive machines, as well as a capacity for expansion at reasonable cost equal to that of almost any other home computer.

The real breakthrough for the programmer, however, is Amstrad's decision to document and release details of the operating system. This is a hitherto unprecedented addition to the documentation available for a home computer from the manufacturer, and it offers a real opportunity for the user to learn machine code programming the easy way, and get results almost immediately, by the use of calls to the operating system.

No longer is there the chicken-and-egg situation, that if you do not understand machine code you cannot use it, and if you cannot use it you cannot find out how to understand it on your computer, because you don't know how to make the computer respond.

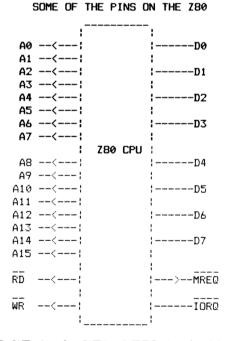

This book is intended for the beginner wishing to learn how to use Machine Code on the Amstrad CPC 464. It will progress from the concepts of programming in machine code, explaining the instructions that the Z80 Central Processing Unit – or CPU for short (the silicone chip that does all the work in the computer) – understands, and how to use them, as well as introducing some of the routines in the operating system at various stages through the text.

Two complete machine code novices have assisted in the writing of this book, and their questions and problems form the basis for its structure. They have also helped to ensure that no information or detail which is so obvious to those in the know that it is almost second nature, and fundamental to being able to perform some function in programming, has been omitted. This

is so often the failing which can leave a novice stranded, like directing someone to a place by telling them that it is on the corner of the High Street by Woolworth's. If they don't know which High Street or where the High Street is, it doesn't help much.

Short listings are given to help in entering machine code programs and to inspect and alter or move the contents of part of the memory. It is strongly suggested however, that you buy the Amstrad Assembler/Disassembler program. This will allow you to enter the code as mnemonics (a sort of shorthand for the names of the instructions the CPU understands) instead of by numbers. It will also allow editing and is much nearer to BASIC in the way that programs are entered.

Whilst it is obviously possible to sit down and read this book from cover to cover, machine code is such a potentially confusing subject, and so many new concepts are likely to be introduced, that it is suggested you sit down in front of your computer and enter and execute (preferably not by hanging) programs when they appear in a chapter. Only once you are sure that you follow what is happening should you progress.

Extensive use is made of the machine operating system, in order to allow results from programs to be seen immediately. The ability to do this is thanks to the Amstrad Firmware Specification (Soft 158) which, although it would probably be almost totally meaningless at this stage, will be a valuable addition to your library once you have finished this book and understand the concepts explained.

The Z80 CPU is one of the most widely used CPUs in the home computer market and, until very recently, was often the main CPU in many business machines. It offers access to the widest variety of software in the world through the medium of CP/M (short for Control Program for Microcomputers), and Amstrad are providing CP/M with their disk drives. The Z80 is also starting to appear as a second processor in business machines, as well as being available as an add-on for the BBC model B, the Commodore 64 and the Apple and its look-alikes. The skills that you will learn from this book are therefore likely to be of use if you have occasion to program other computers in machine code.

#### Chapter Two

## What is Machine Code and Why Use it?

The CPU in your Amstrad computer is basically a very stupid creature, it runs all your BASIC programs very well and does its job excellently but it is stupid none the less. What makes it seem so clever is the firmware, the programs that are running all the time the computer is switched on. In its unmodified version the Amstrad is running an Operating System and the BASIC interpreter.

The operating system deals with such tasks as looking to see if any keys are being pressed, loading from the cassette or putting a character on the screen. You could imagine it as being in charge of all communications, and if it were not present you would have no way of knowing whether your computer was dead or alive, because you could not give it any information and it could not tell you anything.

The BASIC interpreter is literally that, it translates BASIC into the language the CPU understands. Imagine for a moment that someone tells you to turn to page 35. No problem, you just turn to page 35, but what if you were told 赖. Now you are in trouble, not only do you not know what to do, you probably don't even recognise the form of the instruction.

This is like putting yourself into the position of the CPU and giving it a BASIC command to execute. The CPU has no knowledge at all of BASIC, but it goes even further than that. The Chinese above uses one symbol to represent something that when transferred into English takes several symbols, it says Tsung. Still not much help is it even though you can read it? Translated it means 'to sow seed without first ploughing the ground'. This is similar to the difficulty the CPU would experience if asked to deal directly with BASIC. One BASIC instruction often represents many machine code instructions and worse, the characters used by BASIC cannot be understood by the CPU, which only recognises two states, 'on' and 'off'.

Fortunately the 'on's and 'off's are grouped into sets of eight, which gives 256 different combinations. It is these combinations that are used in machine code. You could think of them as the Chinese characters shown earlier.

The problems do not end there however; since one character represents a complete word and there are only 256 possible combinations, the CPU would seem to be limited to a vocabulary of only 256 words. This is nearly correct but, as in English, some words are made up of more than one smaller word.

Key board, for example, would be likely to conjure up a picture of a board in an hotel for hanging keys on, whereas a keyboard is what you will find on your computer. Here the two words have completely different meanings when together and when separate. Some words however can have their meaning subtly altered by the addition of a prefix, able, enable, and unable, or justice and injustice, for example. In each case the latter part has the same meaning but its direction is altered by the first part. The Z80 CPU has some word structures which use these types of construction. The problem of a limited vocabulary however remains.

This limitation does not constrain the concepts that it is possible to convey, but just means that more words are needed to say what you want to say in some cases. The start of this paragraph, for example, could have been written: This not having many words does not put an end to being able to put over all the ideas that can be put over when there are many words . . . same meaning but more words, rather repetitive and not very good English.

Machine code therefore tends to require a lot of simple words, or instructions to do the equivalent of one BASIC keyword, but there is no limit to the ways in which machine code instructions can be put together, and sometimes this means that machine code requires less instructions than BASIC.

With BASIC every time you run a program the interpreter checks each command and makes sure that it is valid, then it translates it into a series of machine code instructions which the CPU then executes, any results are then checked to make sure they are what was expected and saved for further use. All this takes time. With machine code however there is no error checking, no time taken translating, and nothing is saved unless you tell the CPU to save it.

To demonstrate the time saved, enter the BASIC program below. First though, if your computer is already switched on, turn it off and back on again to make sure everything is 'virgin'.

```

10 MM = 43903

20 MEMORY 43799

30 FOR N = 43800 TO 43809 : READ D : POKE N,D : A = A + D: NEXT

40 IF A <> 1338 THEN CLS : PEN 3 : ? "DATA ERROR" : PEN 1 : EDIT

90

50 INPUT "PRESS ENTER TO START";A : B = 255

60 ? "A";: B = B - 1 : IF B <> 0 THEN 60

70 ?

80 CALL 43800

90 DATA 6,255,62,65,205,90,187,16,251,201

100 END

```

Note that ? is used instead of PRINT to save time.

Once you have entered the program type RUN and press the enter key. If all is well you will be asked to "PRESS ENTER TO START", otherwise you will be presented with line 90 in 'edit' mode, because you have made a mistake in typing in the DATA.

When the enter key is pressed 255 'A's will be printed by the BASIC in line 60, hotly pursued by a further 255 'A's printed by the machine code routine you have 'POKED' into memory with line 30, and CALLed with line 80.

Whilst this is not a very exciting program it does show the speed of machine code.

If you count the number of characters used by the machine code routine (remembering that each item in the data statement is one machine code character) you will find that there are ten, of which the last, the 201, is only there to tell the program to return to BASIC. The BASIC program however uses thirty-seven characters if you include the spaces and not the line number. Even if it had been written without any unnecessary spaces it would have taken the equivalent of twenty-five machine code characters' worth of space.

You can check this for yourself if you wish by adding the following lines to your program:

```

110 PEN 3: FOR N = 520 TO 630 : A = PEEK (N)

120 ? A;: IF A = 32 THEN 150

130 IF A > 32 AND A < 129 AND B <> 1 THEN PEN 2: ?: ?N

140 IF A > 32 AND A < 129THEN PEN 1: ? CHR$ (A);: PEN 3: B = 0

150 NEXT

160 PEN 1

170 END</pre>

```

When run this will display the values held in the memory locations where the BASIC program is held in red. If there is a valid character represented by the number it will be displayed in yellow. You will be able to identify the start of line 60 by looking for the "PRESS ENTER TO START"; in line 50, following on until you come to 0 60 in red < in yellow and 0 in red. The 60 0 are the line number and the number before the first 0 is the number of characters in the line. The number in light blue at the start of each line on the screen is the number of the first memory location in the screen line.

The first thing you will notice is that the only characters that have been stored in the same way as you put them in are "A"; all the remainder have been reduced to a sort of code that the interpreter finds easier to handle. Every time you type LIST it is the interpreter that translates these numbers back into what you entered.

The upshot of all this is that the machine code program was not only quicker, but also more economical in terms of memory used, and these are the two main advantages of writing programs in machine code. In fact a program in BASIC can run up to about a hundred times slower than its machine code equivalent.

The main disadvantages however are that programs are almost totally incomprehensible and therefore difficult to debug, and that they tend to be long in terms of the number of instructions required, relative to BASIC or another high-level language. The comprehensibility of machine code is greatly aided by the use of assembler and disassembler programs, and these are discussed in the next chapter, and while normally there is no way to overcome the problem of the large number of instructions required, with the Amstrad CPC 464, use can be made of subroutines in the operating system. Thanks to Amstrad's forethought in making the details available, you have already been able to do this if you entered the program earlier, and the major proportion of the instructions for most programs have already been written for you, by Locomotive Software, when they wrote the operating system. Chapter Three

## **First Concepts**

Before embarking on the world of machine code, there are some concepts that may be new to you and, as it is important that you have at least a rudimentary understanding of these, they will be briefly explained here.

### Hex and Binary

Hex and Binary are different forms of counting, binary to base 2 and Hex to base 16. You have probably come across binary before at school and no doubt thought it was a pretty dumb way to count. For the computer however it is the only way, as you have no doubt realised by now. Due to the CPU only recognising the two states OFF and ON the only way it *can* count is with binary, ON corresponding to 1 and OFF to 0.

Each Binary Digit, or bit for short, has a fixed value according to its position. The decimal system uses the same convention. The right-most digit is the number of units, the next to the left, the number of tens, the next is hundreds and so on. In binary, since there can only be one or none, the values for the positions have to be tailored, so any number can be given. If the same position values were used as with decimal you would count one, ten, eleven, one hundred, one hundred and one and so on.

Your Amstrad computer stores its information in sets of 8 bits, called a byte, and it can also manipulate pairs of bytes (16 bits, known also as a Word) as if they were representing a single number, so the values assigned to each of 16 bit positions are shown below.

#### BIT NUMBER

| 15    | 14    | 13   | 12   | 11   | 10   | 9   | 8   | 7   | 6  | 5  | 4  | 3 | 2 | 1 | 0 |

|-------|-------|------|------|------|------|-----|-----|-----|----|----|----|---|---|---|---|

| 32768 | 16384 | 8192 | 4096 | 2048 | 1024 | 512 | 256 | 128 | 64 | 32 | 16 | 8 | 4 | 2 | 1 |

VALUE

With this combination it is possible to represent any number from 0 to 65535 by a combination of 0s and 1s. Note that the least significant bit is known as bit 0.

Sometimes it is wished to represent a negative value, and a convention has been assigned to this. If you start with 0, which is the same in any number base, and take 1 away you will get -1. Do this with a binary number and you will change every bit, for as far as you can go, to a 1, look at the example below which uses a 4 bit number.

0000

$\begin{array}{cccc} -1 & 0 & -1 & = 1 & borrow & 1 \\ -1 & 0 & -1 & = 1 & borrow & 1 \\ -1 & 0 & -1 & = 1 & borrow & 1 \\ \hline \\ -1 & 0 & -1 & = 1 & borrow & 1 \\ \hline \\ 1111 & \end{array}$

And the answer, because the subtraction is limited to 4 bits, is 1111 binary, or 15 decimal. The same will happen if you do the subtraction with 8 bits, or 16 bits, the decimal answer will be 255 and 32767 respectively.

If you take another number away instead of 1 the same borrow is made, and the left (most significant) bit will always be set (1) whenever the result is a negative number. It is this last fact which gives the clue as to how to represent negative numbers.

If negative numbers are to be used, or may result from a subtraction, it is the convention to use the most significant bit to indicate the sign of a number. Set (1) when the number is negative, and reset (0) for positive. This changes the range of numbers which can be represented by a given number of bits. 16 bits can now show -32768 to +32767, and 8 bits from -128 to +127. This technique for showing signed numbers in binary is called two's complement, if you complement (change 1s to 0s and *vice versa*) a binary number, and add 1, you will change the sign.

It will be up to you whether you use two's complement notation for numbers in programs, or normal unsigned binary, you can even use a mix of the two. The suggested representation for use with a particular instruction, will be shown used in the text of the remainder of the book, and where either method can be employed according to what end result is required, this will be mentioned. The GENS assembler lets you use binary numbers in a program, if you prefix the binary number with a % sign.

But what of HEX? For the computer there is no problem thinking in terms of ONs and OFFs 0s and 1s but try counting yourself in binary or writing it down and checking it. You will find it unbelievably awkward! Most of the time decimal will be the easiest numbering system to use, but occasionally there will be times when it is easier to think in terms of binary. For example, when you are wanting to put a number into one byte in a special way. If you needed to have the number 9 (decimal) in each half of a byte it would mean reverting to binary to work out how. 1001 binary is 9 decimal, (1\*8+0\*4+0\*2+1\*1=9) so you will need to have 1001 1001 to make each half of the byte holding 9 decimal. The decimal value for this is:

1 \* 128 + 0 \* 64 + 0 \* 32 + 1 \* 16 + 1 \* 8 + 0 \* 4 + 0 \* 2 + 1 \* 1

which equals 153 decimal. Convoluted, isn't it?

It is possible to have any value from 0 to 15 held in each half of a byte, giving 16 different values for each set of four bits. So, to make it easy to operate on binary numbers in bytes a new numbering system which uses base 16 is needed. If this was available you could have just said 99 instead of going through the rigours of discovering the decimal equivalent of what you wanted. This base 16 numbering system is called HEXadecimal, but as that is such a mouthful everybody just says HEX.

The first problem you will encounter is that whilst there are already numbers to count from 0 to 9, what do you do with 10 to 15. Rather than learn new symbols for these values, the first six capital letters of the alphabet are used. 10 decimal therefore becomes A, 11 becomes B and so on to 15 which is F. The other problem is that anybody else will think that you are using the decimal system, so some way of signalling that a number is to base 16 (a HEX number), is essential.

Unfortunately there is no set convention for this, your Amstrad uses the & sign to signify that the number following is HEX, the Firmware Specification Manual uses  $\pounds$  and the GENS assembler uses # and many other assemblers (probably including the Picturesque offering) use either a lower or upper case h following a number to show that a number is HEX. This is all downright confusing, but suffice it to say that if a number has anything except a number in its make-up, it is likely to be HEX. In this book all HEX numbers are suffixed by a lower case h, except in listings from the GENS assembler, where they are prefixed by #.

## ASCII

ASCII is short for the American Standard Code for Information Interchange. This is really just a glorified name for numbers representing letters, and operations. Appendix III of the Amstrad User Instructions gives the full list of ASCII codes.

### Address

Address is the term used to describe a memory location. Each memory location has a unique address, starting from 0, for the first location and going up to 65535 (FFFFh). It is often given as a HEX number rather than a decimal number, and most assemblers give the address of a. instruction in the first columns of the printout, when they assemble a program.

### Assembler

Reference is made above to something called an assembler, but what is an assembler?

An assembler is a program which allows you to program machine code in a more recognisable form than numbers, in mnemonics. (Take note! This is a good word for crossword addicts and Scrabble fanatics alike.) Mnemonics are a sort of shorthand way of writing the description of what a machine code operation does, mnemonic means 'an aid to memory', and this is what they are, because you wouldn't have a snowball's chance in hell of remembering all the numeric forms of instructions (unless you are an Icelander, or from northern Scandinavia, they believe Hell is freezing cold and not hot). The assembler lets you write in this shorthand description form, and then when you have finished, it will translate (assemble) this into the 0s and 1s that the computer understands. Most assemblers also have an integral Editor, to allow the program to be written and modified easily. Without this facility, if you had written a long program and you then found that the *n*th instruction was wrong, you would have to rewrite everything from there to the end again.

The program which you write, using the assembler, is called the source code, and this can be saved to tape for later editing if required, but is not needed to run a program once it has been assembled by the assembler. The actual program which can be run, or executed as it should really be called, is the object code.

This object code can also be saved to the tape, using the O command from the GENS assembler or by saving it from BASIC. When saving from BASIC the form of the command is:

SAVE "filename", B, start address, length, entry point

The entry point is the address at which execution is to start, if the program is loaded by the RUN" command, and if not specified the Amstrad will do a system reset when the program is loaded by RUN".

An assembler will allow you to use what are known as 'labels' instead of addresses when you are writing a machine code program. This is an incredibly helpful, and almost Pascal-like facility. (Pascal is a high-level language like BASIC but designed to be assembled like assembly language, the machine code that is created will not run anywhere near as fast as that created by assembly language, and it will also take up more room, but is still a lot faster than BASIC.)

With Pascal instead of using GOSUB followed by a line number, you give a name to a subroutine, and just place the name in the program, when this name is met, the routine associated with its name is executed. The assembler allows labels (short names ended with a colon [:]) to be placed in the listing beside an instruction, and when that label is referred to the address of the instruction which it is beside, will be used instead. This is like being able to give a subroutine a name, and thereafter you would no longer need to know the line number where it started, but could just write GOSUB and the name of the routine.

The assembler also allows *Pseudo Operations*, or *Pseudo Mnemonics* as they are sometimes called. (Quite why one cannot guess, because they are real mnemonics, but just don't become machine code when assembled.) These are used to tell the

assembler to do something with the number which follows, and the main ones are:

Which tells the assembler that everything following it is a comment, and should be ignored. Just like a REM in BASIC.

- EQU EQUate, or EQUals. This allows you to use a label to represent any number you chose. The label to be EQUated should be put to the left of the EQU Pseudo Op, terminated with a colon as always, and the number you wish the label to equate to should be put to the right. For example, LABEL: EQU #1234 will make the label LABEL represent 1234h (4660 decimal) whenever it is used.

- DEFB DEFine Byte. The byte at the address will be made to hold the value which follows. For example, DEFB #20 will make the byte at the address of the DEFB mnemonic hold 20h (HEX) when the program is assembled.

- DEFW DEFine Word. This is the same as the mnemonic above, but it will put a 16 bit number into two memory bytes. The byte of the instruction, and the following byte.

- DEFM DEFine Message. This allows letters to be placed after the mnemonic, between inverted commas, which will have their ASCII codes put into successive locations when assembled.

- DEFS DEFine Space. The number of memory locations given by the number following the DEFS mnemonic will be skipped by the assembler, when assembling the program.

- ORG ORiGinate. The number following the ORG mnemonic will be the address of the next instruction when the program is assembled.

- ENT ENTry. The address at which execution should start, in response to the assembler's J command.

The ORG mnemonic in a listing will give the start address for a section of program, required by the HEX Loader program, and the ENT mnemonic will be followed by the address which should be CALLed from BASIC to run a machine code program.

An OPCODE is a machine instruction which tells the computer what to do and this is sometimes followed by an OPERAND which gives the information upon which the instruction is to be executed.

### **Assembler Listings**

Listings of machine code programs normally have five columns, sometimes six if comments (preceded by a ; remember?) are used. The first column gives the address of the start of the instruction, normally in HEX.

The second gives the HEX version of the machine code instruction, and it is this that should be entered if you are using a HEX Loader, such as the one given in the Appendix, in pairs of numbers.

The third is a line number, and of no use except when writing the program.

The fourth is occupied by any labels, next to the instruction which occupies the address referred to by the label, but the colon which must terminate the label is not shown. This must be entered if you are copying a program from a listing.

The fifth is the mnemonic form of the instruction, as entered by the programmer, and what you enter if you are using an assembler, after any labels in column four that are on the same line.

The sixth column may be taken up by a comment.

Armed with this information you should be ready to proceed!

## **Flow Charts**

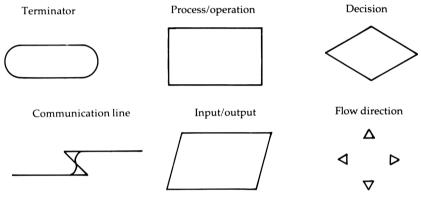

A flow chart is often used in the program design and development stage; this is simply a symbolic representation of the flow of the program under development. There is a standard set of symbols used for drawing flow charts and those that you are most likely to employ are shown in Fig. 4.1 with their uses.

Figure 4.1

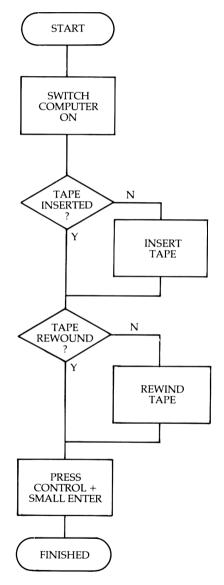

There are a number of further symbols, but they are not often used. The purpose of a flow chart is to make clear the processes that are being carried out by a program. Consider a very simple example, a flow chart to load a program from tape into your Amstrad computer.

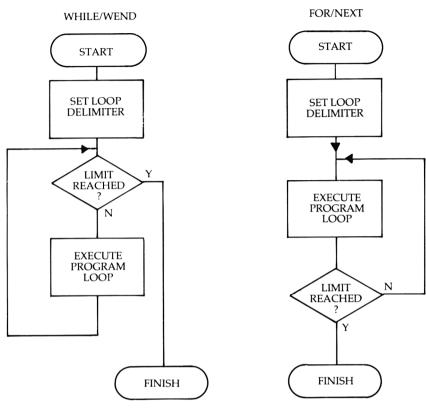

This covers the essential operations, without going into too much detail, as a flow chart should. There are many applications where the flow chart is almost essential for analysing the actions carried out, or necessary to be carried out, by a program. Often they will enable you to find faults before they occur, as a glance at a flow chart will let you see the overall principles of the program under investigation. Look at the example in Fig. 4.3, which shows the difference between a BASIC WHILE loop and a BASIC FOR NEXT loop. It should be immediately apparent what the main difference is.

Figure 4.2

Figure 4.3

Chapter Five

## Simple Machine Code Instructions

## LD CALL RET JP JR

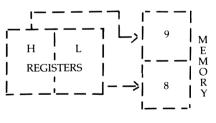

The CPU has fourteen registers, each of which can be thought of as being similar to a BASIC integer variable. They are shown below with their functions. Don't worry if this makes no sense yet, all is about to be revealed.

Z 80 CPU REGISTERS

Figure 5.1

There are six general-purpose registers, and it is these that will be considered in this chapter, along with the special-purpose 'A' or accumulator register and the PC or program counter register.

Each of the general purpose registers B, C, D, E, H and L has the capability of holding a number between 0 and 255, each being made up of eight bits, and they can each be loaded in three basic ways. To continue the analogy to a BASIC variable and help explain each of the ways that a register can be loaded enter the short BASIC program shown in Fig. 5.2. There is no need to delete the first program if it is still there.

```

180 CLS

190 WINDOW#1, 1, 40, 1, 10

200 WINDOW#2, 1, 40, 13, 23

210 WINDOW#3, 1, 40, 12, 12

220 PEN#3, 2: PRINT#3,

DECIMAL

BINA

RY

HEX"

230 INPUT#1, "ENTER A NUMBER ";A

240 IF A > 255 THEN PRINT#1, "INVALID IN

PUT, IT MUST BE BELOW 256": GOTO 230

250 A = INT (A)

260 PRINT#2.USING "#######"; A; : PRINT#2

"; BIN$ (A.8);

"; HEX$ (A,2)

11

270 PRINT#1 : PRINT#2

280 GOTO 230

```

```

Figure 5.2

```

When you have typed the program in run it by typing RUN 180, and you will be asked to enter a number. The basic variable 'A' in the program represents the 'A' register in the CPU. When you enter a number if it is between 0 and 255 it will be printed in Decimal, as you entered it; Binary as the computer handles it, and in Hex.

Each number you enter is loaded into BASIC variable A, and this is then used to provide the number for other duties in the program. If you were to type in 77 you would load A,77 when you pressed enter.

Surprisingly the machine code instruction for this would be spoken of as Load A,77. Easy, isn't it!

Unfortunately, however, the CPU does not understand this, what it requires is 0011110 followed by 01001101. Or 3Eh followed by 4Dh, 62 and 77 decimal. Now things are getting difficult again and this is where the assembler program comes in. You can tell the assembler that the instruction is LD A,77. When the assembler assembles the instruction it will do the translation for you. Note that load has been shortened to LD, which saves your fingers when typing machine code programs and is the standard Z80 assembler convention.

If you now turn back to the program in Chapter 2 and look at line 90, you will see that the third DATA item was 62. This will give you a clue about one of the instructions in the program, and if you were to look up the ASCII code for a capital A (of which an awful lot were printed by the program) you would find that it was 65. Things are probably beginning to dawn about now, and when you find out that the code for instruction to load the B register with a number is 00000110 in binary or 6 in decimal (and Hex for that matter), and you remember that 255 As were printed you will very likely be deafened by the morning chorus.

Who said machine code was difficult? The first two instructions of the program, in assembler, are therefore:

LD B,255 LD A,65

Knowing this you can now change the number of times the character is printed, and which character is printed. Turn first to Appendix III in the Amstrad User Instruction book that came with your computer. Page 1 will show you the codes for each of the ASCII characters and the following pages the characters created by all the codes from 32 up to 255.

Now remove line 40, which checked that you had entered the DATA correctly when you wrote the program. The checksum will be wrong since you are going to change items in the DATA line.

All you need to do now is change the 255 for the number of times the character is to be printed, the 65 for the code of the character you want printed, and then RUN the program from the start to see the result. Don't use any values below 32 for the code, or you may get peculiar results.

If you replace the 255 with 0 you will find that the character in

the A register is printed 256 times. Remembering that each register can only hold 8 bits and looking at the BASIC in line 40, can you work out why this should be?

Think of the sequence of operations, A = 0 or 00000000b. 0 - 1= -1 but 00000000b - 00000001b = 11111111b which is 255 in binary.

You can check this by asking your computer. Type in ? BIN\$ (-1) and you will get the answer 111111111111111. As the left-most eight digits are all that a single register or memory location can hold, this means that -1 decimal is equal to 255 when transferred through an 8 bit register. Confused? Then turn back to Chapter 3 in this book and Appendix II page 2 on, in the Amstrad Computer User's Instructions.

Each of the general purpose registers can be loaded in the same way as the A and B registers. The code for each is as follows:

| ASSEMBLER | DECIMAL | HEX       | BINARY       |

|-----------|---------|-----------|--------------|

|           |         |           |              |

| LD B,n    | 06 n    | 06 n      | 00 000 110 n |

| LD C,n    | 14 n    | 0E n      | 00 001 110 n |

| LD D,n    | 22 n    | 16 n      | 00 010 110 n |

| LD E,n    | 30 n    | 1E n      | 00 011 110 n |

| LD H,n    | 38 n    | 26 n      | 00 100 110 n |

| LD L,n    | 46 n    | 2E n      | 00 101 110 n |

|           |         |           |              |

| LD A,n    | 62 n    | 3E n      | 00 111 110 n |

|           | Fi      | igure 5.3 |              |

In each case the n represents any number, between 0 and 255 decimal (FFh or 11111111b) which is to be loaded into the chosen register.

If you look closely at the binary codes for each instruction there are two things that you may notice.

First, the two ends of the instruction are the same in all cases. It is these two sections that tell the CPU that it is a load instruction involving a number being put into a register. Second, the register is determined by bits 5, 4 and 3, and one possible combination is missing. The three bits which decide which register is to be used are always the same for each register. Whenever an instruction can be performed on any of the general purpose registers three bits are used to tell the CPU which register is to be used.

B is always 000 C is always 001 D is always 010 E is always 010 H is always 100 L is always 101 A is always 111 Figure 5.4

The missing combination, 110, is used for a special purpose and this will be explained later in this chapter.

As well as being able to load a register direct with a number from the following location in memory it is possible to load a register with the contents of another register or from memory.

Think of the BASIC statement A = B. What this is doing is telling the computer that you want the variable 'A' to be equal to the variable 'B'.

If you enter the following lines into your computer and execute them by typing RUN 300 you will find that after line 320 B was loaded with the same value as A, but A was not changed.

```

300 B = 10

310 ? "BEFORE :A=";A;" B=";B

320 A = B

330 ? "AFTER :A=";A;" B=";B

Figure 5.5

```

Having learnt that the machine code mnemonic equivalent to line 300 is LD B,10 what do you think is the equivalent to line 320?

It's pretty obvious isn't it? LD A,B and the same applies to all the other registers.

The actual instructions are made up in the same way as that for loading a register with a number except that bits 7 and 6 are changed from 00 to 01, and the bottom three bits, instead of being 110 are used to identify the register from which the value is to be taken.

The instruction is therefore; ASSEMBLER DECIMAL HEX BINARY LD A, B 120 78 01 111 000

If you remember the three bits for each of the general purpose registers or if you look back at them you should now be able to give the binary instruction for loading any register from any register.

Bits 7 and 6 will always be 01 bits 5, 4 and 3 will be the register to be loaded and bits 0, 1 and 2 the register to be loaded from.

LD H, A would therefore be 01 100 111. What would LD A, H be? Or LD B, D?

Now you have two ways in which you can put numbers into registers and you are no doubt realising that the instructions are really quite logical in the way that they are made up, and hence not too difficult to follow.

All of the general purpose registers have special things that they can do and these will be introduced at various stages in this book. Unfortunately though, unlike BASIC variables, their limitations as to use are fixed, not decided by the user, and are much more subtle, or rather devastating in their effect.

Don't worry, the resemblance between the registers in the CPU, and BASIC variables which has been emphasised, still holds true, but whereas on the Amstrad, when you turn the computer on, any variable can be used for any purpose, be it string, integer or real, and each numeric variable could be used in place of any other numeric variable, in Z80 machine code there are things which can only be done with particular registers.

This is rather like the effect of adding the following line to the program in Chapter 2: 21 DEFSTR A. Now when you RUN the program you will get a type mismatch error when line 30 tries to add numeric information to a variable that can only be a string. It has already been explained that a general purpose register can only hold an 8 bit value but, apart from this limitation, any can be used to represent a number, as the B register in the program in Chapter 2, or a letter, as the A register in the same program.

Were you to make the statement 8 = 9 it would be utter balderdash, we all know that 8 = 8 and 9 = 9. If you type into your computer 8 = 9 followed by enter you do not get an error message, but only because the computer has interpreted the first 8 as a line number, and if you list the program you will find line number 8. If you change this to 88 = 9 and try to execute it, the computer will point it out as a syntax error, the same applies if you try to make a number equal to a variable, for instance by the statement 8 = HL.

No matter what you do (short of redefining the key), typing ?8 will always give the answer 8. But change this to ? PEEK (8) and you will get the answer 195. This is because by adding the PEEK function you are now asking the computer 'what is the contents of the memory location at address 8?' instead of just 'what is 8?'.

When writing machine code there is no need for the PEEK function, or the corresponding POKE command since you are already at machine level. But it is still necessary to be able to access memory locations.

The A register is explained in the next chapter in its role as the accumulator, but has some other special instructions which are relevant to this chapter. This is due to it being the only 8 bit register that can be loaded direct from a memory location, the equivalent to the BASIC:

A = PEEK (nn)

where nn is any 16 bit number.

At first thought the machine code instruction to load the 'A' register with the contents of the memory location at address 8 might be LD A,8, but you will immediately see that this would put the value 8 into A, so a way of differentiating is required.

Each memory location can be thought of as a box, divided into eight smaller boxes, and the PEEK function in BASIC goes some way towards reinforcing this visualisation, by requiring brackets – which look a little like a box – round the number of the box which is to be inspected. (All right, very little like a box!)

You have probably already worked it out, and don't need to be told, but just to confirm how clever you are; the machine code mnemonic for 'with the contents of' requires brackets round whatever is representing the address of the memory location. Hence the instruction to load register 'A' with the contents of memory at address 8 is LD A,(8) and to load into memory at address 40000 the contents of the 'A' register the instruction is LD (40000), A.

If you don't have an assembler things become a little more complicated, but not much.

| ASSEMBLER | DECIMAL | HEX    | BINARY     |     |

|-----------|---------|--------|------------|-----|

| LD A,(nn) | 58 n n  | 3An n  | 00 111 010 | n n |

| LD (nn),A | 50 n n  | 32 n n | 00 110 010 | n n |

It is vital to remember that the 2 'n's in each of the above instructions occupy a memory location and they are calculated by the formula:

n1 = number MOD(256) and n2 = INT (number/256)

This is because of the internal operation of the CPU and there is no alternative but to have the two bytes with the low byte before the high byte. The opposite way to which you would expect. All 16 bit numbers are stored in memory in this manner, be they as part of an instruction or just data in memory put there by the CPU.

It should have been possible to use the above equation directly on your computer to save having to work n1 and n2 for each new number, but due to considerable inconsistencies in Amstrad's BASIC, which sometimes uses 2s complement notation and sometimes normal integer representation, the MOD function is useless with values over 32767.

The following BASIC line however will do the job for you, and you can add it to the program already in memory.

```

1010 N2= INT (NUMBER/256): N1 = NUMBER - N2*256: ? "N1 =";N1;"

N2 =";N2

```

If you now type

```

NUMBER = 40000: GOTO 1010 followed by [ENTER]

```

you should get the answer N1 = 64 N2 = 156. So the full instruction for each of the latest opcodes, with the address to be loaded from and to as 40000 in each case, will be:

| ASSEMBLER    | DECIMAL      | HEX   |

|--------------|--------------|-------|

| LD A,(40000) | 58 64 156 3A | 40 9C |

| LD (40000),A | 50 64 156 32 | 40 9C |

#### BINARY

| LD A, (40000) | 00 111 010 | 0100 0000 | 1001 1100 |

|---------------|------------|-----------|-----------|

| LD (40000),A  | 00 110 010 | 0100 0000 | 1001 1100 |

or for address 8;

| ASSEMBLER | DECIMAL | HEX      |

|-----------|---------|----------|

| LD A, (8) | 58 8 0  | 3A 08 00 |

| LD (8),A  | 5080    | 32 08 00 |

#### BINARY

| LD A,(8) | 00 111 010 | 0000 1000 | 0000 0000 |

|----------|------------|-----------|-----------|

| LD (8),A | 00 110 010 | 0000 1000 | 0000 0000 |

You can test this out for yourself if you wish by changing the program which printed the 'A's.

Line 60 has to be changed to:

60 ? CHR\$ (PEEK (8));: A = A - 1: IF A <> 0 THEN 60

And the second machine code instruction in the DATA statement in line 90 must be changed from LD A,65 to LD A,(8).

This will make it read:

```

90 DATA 6,255,58,8,0,205,90,187,16,251,201

```

The checksum in line 40, if it is still there, must be changed to 1277.

Most important line 30 must be changed to:

40 FOR N = 43880 TO 43890: READ D: POKE N, D: A = A + D: NEXT

This is because there is now one extra byte of code that needs to be POKEd into memory.

If you added line 21 earlier (DEFSTR A) remember to remove it!

Now when you RUN the program, instead of getting 'A's you should get\s (backslashes).

Perhaps the next most useful thing about the general purpose registers, is that each pair can be used together, that is as BC, DE and HL. When used this way they can be treated as 16 bit registers.

Whereas with a single register you are limited to numbers that can be represented in eight bits, in other words between 0 and 255, with a register pair you can use any whole number from 0 to 65535, because you now have sixteen bits to play with. There are however penalties to be paid for the ability to use registers in pairs as if they were just one 16 bit register.

You have seen that, when used on their own, ALL general purpose as well as the 'A' or accumulator registers can:

- 1) be loaded from any other general purpose register;

- have a number loaded directly into them;

but that the 'A' register alone can be loaded directly from or to, a numbered memory location, as in the LD A,(nn) or the LD (nn),A instructions.

With register pairs however, there is no machine code instruction for LD rr,rr' (load one register pair with the contents of another register pair). You can however load a number directly into any register pair.

For those of you with an assembler, nothing could be simpler. You probably don't even need to be told what the instruction is! It's LD rr,nn; rr is any of the register pairs, BC, DE or HL and nn is any 16 bit integer.

The instruction to put the value 40000 into the BC register pair would therefore be:

LD BC,40000

or to put the value 8 into the HL register pair:

LD HL,8

If you remember the construction of the binary instructions to load a number into a single register you almost certainly can guess the first two bits of the binary instruction to load a register pair. If you don't remember then turn back and have a look.

Right first time (I hope)! The first two bits are 00.

The remainder of the instruction is made up in much the same way. After the initial 00 the next two bits are used to determine which register pair is to be loaded.

00 for the BC register pair.

01 for the DE register pair.

10 for the HL register pair.

(These two bit codes are always the same for each register pair, and are used whenever an instruction can be performed on any of the register pairs.)

The next bit is 0 and the last three bits are 001.

The full instruction for each register pair is therefore:

| ASSEMBLER | DECIMAL | HEX    | BINARY     |     |

|-----------|---------|--------|------------|-----|

| LD BC,nn  | 1 n n   | 01 n n | 00 000 001 | ΠN  |

| LD DE,nn  | 17 n n  | 11 n n | 00 010 001 | n n |

| LD HL,nn  | 33 n n  | 21 n n | 00 100 001 | n n |

n1 and n2 are calculated in the same way as for the LD A,(nn) instructions. Therefore:

| ASSEMBLER   | DECIMAL       | HEX      | BINARY               |           |

|-------------|---------------|----------|----------------------|-----------|

| LD BC,40000 | 1 64 156      | 01 40 9C | 00 000 001 0100 0000 | 1001 1100 |

| LD HL,8     | 33 <b>8</b> 0 | 21 08 00 | 00 100 001 0000 1000 | 0000 0000 |

Knowing how to load a register pair with a sixteen bit number is a waste of time if there is no use for the register pair once loaded. One of the most common uses of a register pair is as a variable to point to a memory location.

In the BASIC earlier PEEK (8) was used to find the contents of memory location 8, and the machine code equivalent using the 'A' register was explained. This type of instruction is very limiting, especially if a series of locations need to be read from or written to. In BASIC the way to handle the problem would be to use a variable. For example if the variable HL was made equal to 8 it would have been possible to use PEEK (HL) instead.

In machine code the same applies, but this is where the idiosyncrasies of the Z80 CPU start to gain prevalence.

With a general purpose register, not only is it impossible to use the LD r,(nn) or the LD (nn),r constructions, but only the HL register pair can be used as a pointer. You have seen the elusive 110b code, missing from the series of three bit values used to represent the general purpose registers, used at the end of a LD r,n instruction code starting with 00b. Here it indicates that the next byte (the one after the instruction) is to be used as a number.

Used in the middle of the LD r,n instruction or in the LD r,r' instructions, beginning with 01b, it has a different interpretation. It would be impossible for the 110b to have the same meaning since, as has already been demonstrated earlier, a number always has the same value. All that happened when it was tried to change the value from BASIC was a syntax error. But there is a way in which a number can be changed, and that is when it is used as an address.

Wherever the 110b code is used in a load instruction in place of a code representing a register, it is taken by the CPU to refer to the memory location whose address is held in the HL register pair.

Therefore to load the D register with whatever is in memory location 40000 you would write:

| ASSEMBLY    | DECIMAL   | HEX      | BINARY                         |

|-------------|-----------|----------|--------------------------------|

| LD HL,40000 | 33 64 156 | 21 40 9C | 00 100 001 0100 0000 1001 1100 |

| LD D,(HL)   | 86        | 56       | 01 010 110                     |

or to load the contents of memory at address 8 into the B register:

| ASSEMBLY  | DECIMAL | HEX      | BINARY               |           |

|-----------|---------|----------|----------------------|-----------|

| LD HL,8   | 33 8 0  | 21 08 00 | 00 100 001 0000 1000 | 0000 0000 |

| LD B,(HL) | 70      | 46       | 01 000 110           |           |

Note the brackets round the HL in the assembly language instruction, meaning 'with the contents of the address at'.

It is perfectly in order to reverse this process and, instead of loading a register with the contents of a memory location, load a memory location with the contents of a register. The instruction then becomes:

LD (HL),r

As with the LD  $r_{r}$ (HL) any general purpose register or the 'A' register can be used, and the binary instruction opcode is about as predictable as it could be.

To load a register with the contents of the memory location at address HL the opcode is:

[01] [the three bit code for the register] [110]

so, to load the memory location at address HL with the contents of a register it becomes:

[01][110][the three bit code for the register]

You didn't really need this book to tell you that, did you?

If you change the DATA statement in line 90 of your BASIC program to:

90 DATA 33,8,0,70,58,8,0,205,90,187,16,251,201

change the checksum in line 40 to 1127 and change the number after the TO in line 30 to 43892 you can now see the LD B,(HL) and the LD HL,nn in action. The BASIC equivalent would be to change the end of line 50 from B = 255 to HL = 8 : B = PEEK (HL).

When run the machine code routine will now load the HL register pair with 8 and then load B with whatever is in location HL. The start of the routine is now:

| ASSEMBLY  | DECIMAL |

|-----------|---------|

| LD HL,8   | 33 8 0  |

| LD B,(HL) | 70      |

| LD A,(8)  | 58 8 0  |

When the 110b code is used in the LD r,n opcode for the r part, giving the binary opcode 01 110 110, this gives the assembly language instruction: LD (HL),n which will put into memory at address HL the number in the location following the instruction.

With the 'A' register it is possible to use any register pair as a variable, or pointer. The assembly language instructions are pretty obvious. They are LD A,(rr) or LD (rr), A where rr is any

register pair. For example using the 'A' register it is quite acceptable to write:

LD DE,8 LD A,(DE)

The opcode for LD A,(HL) has already been explained and you have no doubt noticed that all possible combinations of instruction starting with 01 are allocated. It is necessary to use a different construction for the instructions LD A,(BC) LD A,(DE) LD (BC),A and LD (DE),A.

One clue to how these instructions are made up is to be found in the LD A,(nn) and LD (nn),A opcodes, and another is in the codes for the register pairs.

Have you noticed that the 3 bit codes for the general purpose registers share their high two bits with the 2 bit codes for the register pairs that use them. B has the code 000 and C 001, BC the code 00. D has the code 010 and E 011, DE is 01, H is 100 and L is 101, making HL 10.

The opcode for LD A, (nn) in binary is 00 111 010 and it has been pointed out that, in the instructions to load a number into a register pair, bits 5 and 4 tell the CPU which register pair to use. The only opcode missing from the set is 11. Lo and behold! What do we have in bits 5 and 4 of the LD A, (nn)? And what *do* you suppose the instruction LD A, (BC) will be, in binary?

Well done, but it didn't really require you to be a genius, did it? The binary opcode for LD A,(BC) is 00 001 010, for LD A,(DE) it would be 00 011 010.

The opcode for LD A,(HL) is *not* 00 101 010, it is 01 111 110 and was explained earlier, so what do you suppose happens in response to 00 101 010? Stay tuned and all will be revealed. First though there is the question of the LD (rr),A opcodes to be resolved, and be warned! These are almost as complicated as the LD A,(rr) opcodes.

LD (nn), A in binary is 00 110 010, again the missing 11b from the set of codes for register pairs is present in bits 5 and 4. Here, as in the previous instructions, to change (nn) to (BC) or (DE) all you do is alter the 11b to 00b or 01b. The opcode for LD (BC), A is therefore 00 000 010 and for LD (DE), A 00 010 010. But as with the previous instructions the HL code 10b used to make the opcode 00 100 010 doesn't mean LD (HL), A.

All the above opcodes, which load the 'A' register from or to a

memory location pointed at by a register pair, are single byte instructions. The codes 00 100 010 and 00 101 010, which use the HL code 10, are made up of three bytes. The first is, of course, the opcode. Either 00 100 010 or 00 101 010, and the next two are the operand. (Remember, the operand is information needed for the opcode to be able to perform its task.) These two opcodes are used to load the HL register pair either to, or from, the memory location addressed in the next two bytes. They work in the same manner as the LD (nn), A which loads the A register to, and LD A,(nn) instruction which loads the A register from, a memory location addressed by the (nn).

Here are the assembly language and binary instructions in full.

| ASSEMBLER  | BINARY         |  |  |  |  |

|------------|----------------|--|--|--|--|

| LD HL,(nn) | 00 101 010 n n |  |  |  |  |

| LD (nn),HL | 00 100 010 n n |  |  |  |  |

Assume that the address (nn) is 8, as has been used in the previous load instructions. This will make n1 0000 1000 and n2 0000 0000 in both the binary examples above and the assembler will become:

LD HL,(8) and LD (8),HL

In the first case the HL register pair will be loaded with a sixteen bit number from memory at the specified address, and in the second the sixteen bit number in HL will be loaded into memory at the specified address.

One problem though, only one memory address has been defined by the operand, and a single memory location is only eight bits, so how can a 16 bit number be condensed into eight bits? The short answer is, it can't. The way the CPU copes with

Figure 5.6

this is to use the memory location specified, for the low byte, and the memory location one above, for the high byte. Being logical, because logic is what computers are all about, the high byte comes from the H register and the low byte from the L register, and the low byte is in the lower memory location.

The CPU always starts at the bottom and works up and this is why, when you are loading machine code into memory, all 16 bit numbers are reversed. If you think of HL as high low, and remember to start from the bottom and work up it may help you to avoid any mistakes when writing code. When using an assembler it does all the reversals for you so, if you are using one, there is no need to change numbers from their normal form.

The last load instructions to be explained in this chapter are those which work in the same manner as above but for the BC and DE register pairs. These are less used than the instructions using the HL register pair because they use two bytes of memory to hold the instruction. The assembly language for these instructions is just what you would expect:

LD BC,(nn) LD DE,(nn) LD (nn),BC and LD (nn),DE

If you cast your mind back to when you were reading Chapter 2, you may recall that, in the analogy to English and Chinese language words, it was shown how the addition of an extra word could change the meaning of a word. Well, the opcodes for the four instructions above all have the prefix (in Hex) ED. (1110 1101b or 237 decimal but ED is much easier to remember.) All the comments regarding the instructions just explained, using the HL register pair, also apply to these instructions. It is considered good practice to use instructions which use the HL register pair, where possible, as these take half the amount of memory for the opcode. The actual opcodes are made up as follows:

| ASSEMBLER  | DECIMAL    | HEX       | BINARY               |     |

|------------|------------|-----------|----------------------|-----|

| LD BC,(nn) | 237 75 n n | ED 4B n n | 1110 1101 01 001 011 | n n |

| LD DE,(nn) | 237 91 n n | ED 5B n n | 1110 1101 01 011 011 | n n |

| LD (nn),BC | 237 67 n n | ED 43 n n | 1110 1101 01 000 011 | n n |

| LD (nn),DE | 237 83 n n | ED 53 n n | 1110 1101 01 010 011 | n n |

Figure 5.7

There is a summary of all the instructions starting with LD at the end of this chapter, and a graphic representation is given in Zilog's summary in the appendix.

### **The Program Counter**

All the time your computer is turned on, unless someone has stopped the CPU for some reason, the program counter register is chuntering away quite happily, with only one aim in life, which is to get to the top and start again. Its purpose is to keep track of the program being run, and it will always hold the address in memory of the program instruction which is currently being executed. When you first turn on the computer the PC is forced to hold address 0, so that the first instruction is fetched from here. This means that a program to set the computer into a known state can be automatically executed at turn-on. This is known as a Cold Start or Early Morning or Wake Up, and on the unexpanded Amstrad this puts the computer into the BASIC programming mode and displays the Amstrad and Locomotive copyright.

As already mentioned, the computer is always running a program whenever it is switched on but, since the computer does not know what it is going to be asked to do next, it is essential to have some control over the program counter. Imagine what it would be like if the computer's memory were a piano keyboard, and all you could do was play each note in turn, from the bottom of the keyboard to the top, and then start over again. Some interest could be added by tuning the strings in the piano to play a short tune, but this would soon become boring, and all the strings would need to be retuned every time a new melody was required. This is similar to what would happen if the computer's program counter could not be altered. The way the strings were tuned would be the program, and each key a memory location.

Fortunately it is possible to alter the PC, and in BASIC this is achieved by the GOTO and GOSUB and RETURN commands. The GOTO forces the execution of the program to jump to the line nominated, and the GOSUB calls a subroutine at the line chosen. When the subroutine has completed its task, control is returned (by the RETURN command) to the main program, which carries on at the instruction after the GOSUB.

The machine code equivalents to these BASIC commands

perform exactly the same tasks but their names are slightly different, as with the assembler LD mnemonic, which describes the action performed by the equivalent BASIC command. (LD is spoken as 'load', which you undoubtedly remembered.)

Can you guess what the machine code instructions are? GOTO becomes JUMP and GOSUB becomes CALL, RETURN stays the same. The return instruction is abbreviated to RET when using an assembler but CALL is written in full. Jump is a little more complicated so this will be explained later in the chapter, after the use of CALL and RET has been defined.

The CALL and RET instructions exactly duplicate their BASIC equivalents but, since machine code does not have line numbers, the CALL is made to the address holding the start of the first instruction of the subroutine.

The CALL instruction is made up of three bytes, the first is the opcode, and the next two are the address of the subroutine to be called. The two bytes holding the address are made up in normal Z80 manner, low byte first. If you are using an assembler it will do the calculation for you, as it did for the LD instructions.

The CALL and RET opcodes are as follows:

| ASSEMBLY | DECIMAL | HEX  | BINARY         |

|----------|---------|------|----------------|

| CALL nn  | 205 n n | CDnn | 11 001 101 n n |

| RET      | 201     | C9   | 11 001 001     |

If you look back to Chapter 2 and look at the program you typed in, or if you are in front of your computer and have entered the programs so far, list line 90. You will find that the numbers immediately after those that you have experimented with, are 205, 90, 187.

You should now know what these are telling the CPU to do. The 205 is a CALL instruction and the address CALLed can be worked out by adding the next number to 256 \* the third.

187 \* 256 = 47872. 47872 + 90 = 47962 or BB5Ah

So now you know that the start of the routine you have written first loads the A register with the code of the character to be printed, then loads the B register with the number of times the character is to be printed, and then CALLs a subroutine starting at address 47872 (BB5Ah). This subroutine is part of the operating system of the computer, and is probably the subroutine that you will use more than any other. Amsoft have called it TXT OUTPUT, and it will print the character whose code is held in the 'A' register to the current window, at that window's current cursor position. The subroutine will also obey control codes, and these are explained in Chapter 9 of the Amstrad User Instruction book.

To give a brief example of how a control code is responded to change line 90 to: 90 DATA 62,7,205,90,187,201 and change the number after the TO in line 30 to 43885. If line 40 is still present then the checksum must be changed to 752. In assembly language the program now reads:

LD A,7 CALL 47962 RET

When RUN all that the machine code will do is sound the bell, emitting a bleep from the computer. If you hear nothing try turning the volume up and typing CALL 43880 followed by [ENTER]. This will call the machine code directly, instead of it being called by the BASIC program.

Unlike load (LD) instructions it is not possible to nominate an address by pointing to it with a register pair, the address to be called must always be in the two bytes following the CALL opcode. The RETurn at the end of a subroutine will be to the address immediately after the three bytes of the CALL (one byte for the opcode and two for the operand).

To be able to make a RETurn the CPU has to know where the subroutine was CALLed from, and it accomplishes this by using something called the Machine Stack, or just the stack for short. A brief explanation of what this is, and how it is used when a CALL or a RETurn instruction is encountered in a program, follows. Use of the stack will be discussed in detail in Chapter 9.

The stack can be compared to a spike on the ceiling, and each byte of information being saved on it, can be thought of as a piece of paper. When the piece of paper is put on the stack, the stack grows downwards, and the only information that can be taken off the stack is the piece on the bottom. In order to get something not on the bottom location, everything below will have to be taken off first.

The stack occupies an area of memory, and the address of the

bottom of the stack is always held in the 16 bit Stack Pointer register. The area of memory chosen for the stack must be protected from being used by the program, because if corrupted it would almost certainly cause the program to crash. Normally this is achieved by placing the stack at the top of a large area of free memory, as this allows it the maximum space to grow down without trespassing on anything else.

Whenever a CALL instruction is encountered in a program, the CPU, once it has found out the destination of the CALL, places the address currently in the PC (the address of the next instruction to be fetched) onto the stack, and replaces it in the PC with the address of the subroutine. This causes the next instruction to be fetched from the address of the CALL, and the subroutine is then executed. At the end of the subroutine, when the RET is executed, the CPU collects the return address from the stack, and puts it into the PC, thereby making program execution continue at the address after the original CALL.

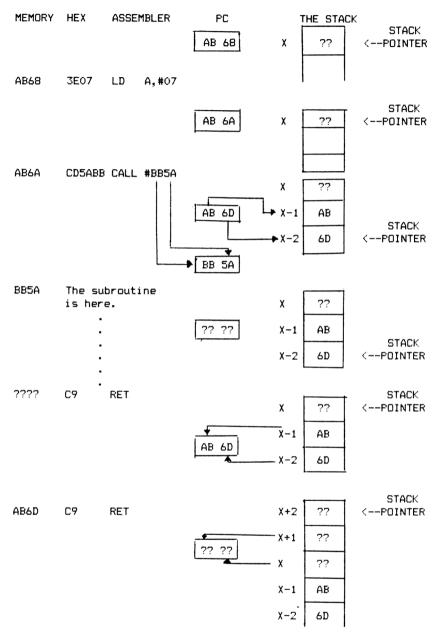

The diagrams overleaf shows the sequence of events when a subroutine is CALLed and when the RETurn is executed. The assembler listing for the program is given in Fig. 5.8. The first column is the memory address of the start of the instruction, in Hex, the second column is the Hex code of the instruction and the third column is the actual assembler listing, again Hex numbers have been used. The reason for the use of Hex numbers is that they demonstrate much more clearly what is happening, since each byte of memory or single register can hold a two digit Hex number.

The example used is the program given above to sound the bell.

Every time anything is put onto the stack it grows down by two bytes, and each time something is taken off the stack it shrinks by two bytes. It is therefore very important to make sure that a program does not put more onto the stack than it takes off. This could make the stack either grow down so much that it starts to use memory used to hold a program, or have the wrong information on the bottom when something is to be taken off. Between information being put onto the stack and its being required again, there *must* be an equal number of things put onto and taken off the stack. This is absolutely vital and cannot be stressed too much, especially since there are instructions explained later, other than CALLs and RETurns which use the stack for storage of information. An imbalance of the stack is the single most

Figure 5.8

common cause for a program crashing. Unlike with BASIC, it is often the case that all one can do when a program crashes, is switch off and start again.

## Jumps

There are two types of jump instruction, the first one to be explained imitates the BASIC GOTO almost exactly. With this instruction the absolute destination is given after the command. Consider for example the BASIC command GOTO 100. There must be a line in the program with the number '100' and when the GOTO 100 is executed control is transferred to line 100. In machine code, as you know, there are no line numbers, so instead of transferring control to a line number control is transferred to an address.

The mnemonic for this instruction is JP, short for JUMP, and it is normally followed by two bytes giving the address to jump to. The actual jump is made in exactly the same way as the CALL instruction transfers control to a subroutine, except that, as there is to be no RETurn, the stack is not used. The mnemonic for this type of jump is JP nn, and it allows a jump to any location in the memory currently paged in. The instruction comprises three bytes, constructed as the three bytes for a CALL instruction, but the first byte, instead of being 11 001 101 for CALL, becomes 11 000 011 for JP. If the CALL in the last program is changed to a JP it will become:

ASSEMBLER DECIMAL HEX BINARY JP 47962 195 90 187 C3 5A BB 11 000 011 0101 1010 1011 1011

The JP instruction can also be used with the HL register pair containing the address to be jumped to. In this case the instruction only takes one byte and the jump is made to the address contained in the HL register pair. If you recall how assembly language represents 'contained in' you should already know the mnemonic. The full opcode is given below:

| ASSEMBLER | DECIMAL | HEX | BINARY     |

|-----------|---------|-----|------------|

| JP (HL)   | 233     | E9  | 11 101 001 |

This is one of the most useful instructions in the Z80 CPU and is often used in conjunction with a CALL to achieve an equivalent to an ON GOSUB command in BASIC. This is explained in the next chapter.

Most jumps are made to an instruction very close to the address from which the jump is being made, and the Z80 CPU has an instruction that allows a jump to be made to a location relative to the address in the program counter. Surprisingly this instruction is called a Jump Relative! In assembly language this is shortened to JR.

The JR instruction consists of just two bytes, the first is the opcode and the second, the distance of the jump from the address the program counter expects the next instruction to come from, in twos complement notation, as explained in Chapter 3. This allows a jump to be made +127 to -128 relative to the PC. The opcode for JR is:

| ASSEMBLER | DECIMAL | HEX  | BINARY     |   |

|-----------|---------|------|------------|---|

| JR n      | 24 n    | 18 n | 00 011 000 | n |

Normally when using an assembler there is no need to calculate the length of a JR. Instead a LABEL is used, either by making the LABEL EQUal to the address to be jumped to in the program or, more usually, by defining the LABEL within the program (EQU is a pseudo operation and was explained in Chapter 3).

To help explain this consider the example below:

| ADDRESS       | LABEL  | ASSE | MBLER | DECIMAL    | HEX      |

|---------------|--------|------|-------|------------|----------|

| 43880 (AB68h) |        | LD   | A,7   | 62 7       | 3E 07    |

| 43882 (AB6Ah) | PRINT: | CALL | 47962 | 205 90 187 | CD 5A BB |

| 43885 (AB6Dh) |        | LD   | A,65  | 62 65      | 3E 41    |

| 43887 (AB6Fh) |        | JR   | PRINT | 24 249     | 18 F9    |

The 249 after the 24 opcode of the JR instruction tells the CPU to transfer execution to an address -7 from the current PC. The PC is already pointing to the next instruction since the read of the JR n has been completed, and therefore contains the address 43889. 43889 - 7 = 43882. The jump will therefore be made to the start of the CALL instruction.

| ADDRESS       | LABEL  | ASSEI | MBLER | DECIMAL    | HEX      |

|---------------|--------|-------|-------|------------|----------|

| 43880 (AB68h) |        | JR    | GO    | 24 5       | 18 05    |

| 43882 (AB6Ah) |        | LD    | A,7   | 62 7       | 3E 07    |

| 43884 (AB6Ch) | PRINT: | CALL  | 47962 | 205 90 187 | CD 5A BB |

| 43887 (AB6Fh) | GO:    | LD    | A,65  | 62 65      | 3E 41    |

| 43889 (AB71h) |        | JR    | PRINT | 24 249     | 18 F9    |

If the program had been:

Then instead of the bell being sounded followed by 'A's until you reset the computer, the JR GO would make the PC jump the LD A,7 and the CALL 47962 and the first thing to be printed would be an 'A'. Note that the jump is only 5 which skips the five bytes *after* the JR GO.

It is possible to use calculated relative addressing with an assembler, but this is unnecessary except with very long programs where it is important to save space by not using labels. The Highsoft Devpac slightly complicates matters, in the way the GENSA3 assembler operates. Jump distances are calculated relative to the assembler's location counter and *not* the PC. This is explained on page 2.6 of the manual which comes with the Devpac cassette. In essence the location counter will be at the start of the JR instruction, when the calculation is made, and therefore you will need to add 2 to the jump distance worked out the proper way, to make the correct jump. The location counter is addressed by use of the \$ symbol. The JR PRINT instruction in the routine above would be rewritten:

JR \$-5

and not the more logical JR -7.

The Picturesque assembler, which is to be available shortly, will employ the standard Z80 method of calculation, and the instruction using this, therefore becomes the expected JR -7.

If, as will most often be the case, except when space is at a premium, you are using labels none of this will affect you, and there is no need to worry about which assembler you are using. Any relative jump to an offset indicated by a label, will always be made to the instruction immediately following the label.

There is one last instruction to be described in this chapter, and

it is one of the simplest but most useful instructions available. It enables the contents of the DE register pair to be exchanged with the contents of the HL register pair. This is extremely useful if the HL register pair is being used to point to an address in memory, but is then needed for another purpose. You will find out why this situation is likely to arise in the next chapter. As you might expect the mnemonic for the instruction is: EX DE,HL the EX being the abbreviation for EXchange. The full opcodes are given below:

| ASSEMBLER | DECIMAL | HEX | BINARY     |

|-----------|---------|-----|------------|

| EX DE,HL  | 235     | EB  | 11 101 011 |

If DE held 10 and HL 37 before the EXchange DE will hold 37 and HL 10 afterwards.

There now follows a very brief résumé of the instructions you have learnt in this chapter:

```

r = a single 8 bit register A, B, C, D, E, H or L

rr = a register pair being used as a 16 bit register

n = an 8 bit number 0 to 255

nn = a 16 bit number 0 to 65535

() round a number or register pair = the address at

PC = Program Counter

SP = Stack Pointer.

```

## LD means LOAD

Any r can be loaded with any n. The instruction has the form LD r,n.

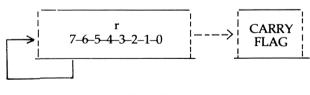

Any r can be loaded from any other r. The instruction has the form LD r,r'.