#### The Blacksburg Continuing Education<sup>™</sup> Series

The Blacksburg Continuing Education Series<sup>™</sup> of books provide a Laboratory—or experimentoriented approach to electronic topics. Present and forthcoming titles in this series include:

- DBUG: An 8080 Interpretive Debugger

- Design of Active Filters, With Experiments

- Design of Op-Amp Circuits, With Experiments

- Design of Phase-Locked Loop Circuits, With Experiments

- Design of Transistor Circuits, With Experiments

- Design of VMOS Circuits, With Experiments

- The 8080A Bugbook®: Microcomputer Interfacing and Programming

- 8080/8085 Software Design (2 Volumes)

- 555 Timer Applications Sourcebook, With Experiments

- Guide to CMOS Design Basics: Circuits and Experiments

- Interfacing and Scientific Data Communications Experiments

- Introductory Experiments in Digital Electronics and 8080A Microcomputer Programming and Interfacing (2 Volumes)

- Logic & Memory Experiments Using TTL Integrated Circuits (2 Volumes)

- Microcomputer—Analog Converter Software and Hardware Interfacing

- Microcomputer Interfacing With the 8255 PPI Chip

- NCR Basic Electronics Course, With Experiments

- NCR Data Communications Concepts

- NCR Data Processing Concepts Course

- NCR EDP Concepts Course

- Programming and Interfacing the 6502

- 6800 Microcomputer Interfacing and Programming, With Experiments

- 6502 Software Design

- TEA: An 8080/8085 Co-Resident Editor/Assembler

- TRS-80 Interfacing

- Z-80 Microprocessor Programming & Interfacing (2 Volumes)

In most cases, these books provide both text material and experiments, which permit one to demonstrate and explore the concepts that are covered in the book. These books remain among the very few that provide step-by-step instructions concerning how to learn basic electronic concepts, wire actual circuits, test microcomputer interfaces, and program computers based on popular microprocessor chips. We have found that the books are very useful to the electronic novice who desires to join the "electronics revolution," with minimum time and effort.

Additional information about the "Blacksburg Group" is presented inside the rear cover.

#### Jonathan A. Titus, Christopher A. Titus, and David G. Larsen "The Blacksburg Group"

Bug symbol trademark Nanotran, Inc., Blacksburg, VA 24060 Bugbook is a registered Trademark of E & L Instruments, Inc., Derby, CT 06418

# Z-80 Microprocessor Programming & Interfacing

Book 1

by Elizabeth A. Nichols, Joseph C. Nichols, and Peter R. Rony

Howard W. Sams & Co., Inc. 4300 WEST 62ND ST. INDIANA POLIS, INDIANA 46268 USA Copyright © 1979 by Elizabeth A. Nichols, Joseph C. Nichols, and Peter R. Rony

#### FIRST EDITION SECOND PRINTING-1980

All rights reserved. No part of this book shall be reproduced, stored in a retrieval system, or transmitted by any means, electronic, mechanical, photocopying, recording, or otherwise, without written permission from the publisher. No patent liability is assumed with respect to the use of the information contained herein. While every precaution has been taken in the preparation of this book, the publisher assumes no responsibility for errors or omissions. Neither is any liability assumed for damages resulting from the use of the information contained herein.

International Standard Book Number: 0-672-21609-4 Library of Congress Catalog Card Number: 79-63822

Printed in the United States of America.

### Preface

The microelectronics revolution is here, and gaining momentum. It all began 30 years ago with the development of the transistor. The transistor, a physically small, low-power amplifier, replaced the large, power-hungry vacuum tubes of the first generation computers. Due to a natural synergism between transistors and digital logic, their small size and low cost, transistors have become the basic building blocks for computer circuits. Transistors combine to form gates; gates combine to form flip flops, counters, adders, and other logic functions; and these, in turn, combine to form the memory, control, arithmetic, and logic units which make up the central processing unit (cpu) of a computer. Thus, the number of transistors in a logic circuit has become a reasonable measure of its functional complexity. In 1959, the first integrated circuits consisting of small groups of planar transistors were developed on thin wafers of silicon or germanium. This began the era of Small Scale Integration (SSI) in which 12 or fewer gates could be incorporated into a single integrated circuit (IC). Since 1959, the number of transistors in advanced ICs has been at least doubling every year. Today, circuits containing 262,144 elements are available and the technology is still far from its theoretical limits. The Z-80 CPU and support chips, introduced by Zilog in 1976, represents the state-of-the-art in 8-bit microprocessors. Zilog is currently developing a successor to the Z-80 line, the Z-8000 series of cpu and support chips. However, the Z-8000 will be a 16-bit cpu with computational capacity comparable to mid-range minicomputers, a significant jump in capability. And this is only the be-ginning. The real revolution will be manifest in the exponential pro-liferation of products and services dependent on microelectronics. This book is one of two volumes on Z-80 microprocessor programming and interfacing. Book 1 is on Z-80 software—assembly and machine language programming. Book 2 covers interfacing digital circuits with the Z-80 CPU, PIO, and CTC chips. These books are laboratory oriented texts that are designed to give an integrated approach to microcomputer programming and interfacing. The strong emphasis is on learning through experimentation. Each topic introduced is reinforced with laboratory work that shows not only how ideas succeed, but also where they fail, and what the pitfalls are.

Book 1 requires no background in computer science, programming, or digital electronics. Book 2 however, assumes familiarity with the topics covered in Book 1. In both books, topics are presented in the order that the authors feel is most conducive to learning in a selfstudy environment. Answers are provided for all the exercises, and every attempt is made to anticipate questions and logical extensions to the experiments.

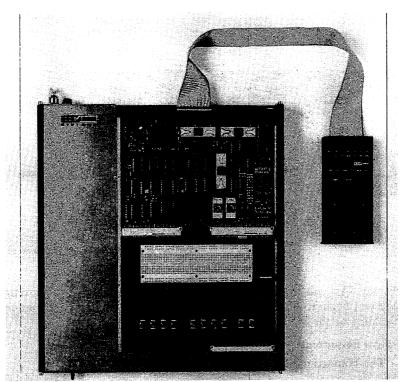

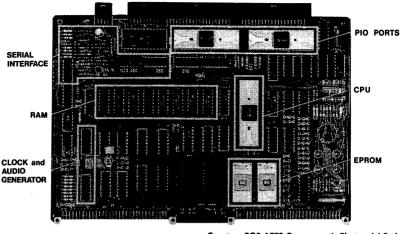

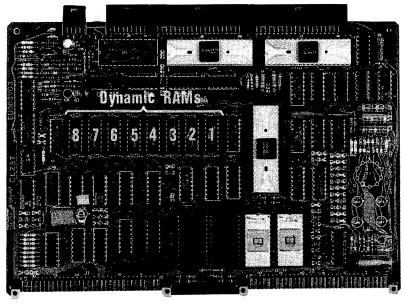

To enhance the laboratory orientation in the books, the experiments use a sophisticated Z-80-based single-board microcomputer manufactured by SGS-ATES, called the Nanocomputer. The Nanocomputer is an excellent educational computer because it is simple for a novice to use, but incorporates enough options, flexibility, expandability, and sophistication to keep the interest of the most experienced user. For more information on the Nanocomputer, contact SGS-ATES Semiconductor Corp., 240 Bear Hill Road, Waltham, MA 02154.

The authors are indebted to many members of the staff at SGS-ATES in Milano, Italy: R. Baldoni, A. Cattania, B. Facchi, F. Luraschi, C. Wallace, and especially A. Watts whose many ideas and technical expertise on the Nanocomputer tremendously improved these books. Also we wish to thank C. Edson and U. Broggi of SGS-ATES in the USA who greatly expedited progress by acting as liasons between the US and Italian efforts on this project. Finally, much credit is due to J. Titus and D. Larsen of the Blacksburg Group for their efforts in coordinating with Howard W. Sams & Co., Inc. to bring about the publication of these books.

> ELIZABETH A. NICHOLS JOSEPH C. NICHOLS PETER R. RONY

### Contents

#### CHAPTER 1

9

21

#### **CHAPTER 2**

AN INTRODUCTION TO MICROCOMPUTER PROGRAMMING . . . Objectives — What Is a Computer? — What Is a Microcomputer? — What Is a Computer Program? — Instructions — Mnemonics — Instructions — Machine Language — A Simple Program — Memory — Memory Address — Range of Memory Locations — Hi and Lo Memory Addresses — Demonstration No. 1 — Review

#### CHAPTER 3

#### **CHAPTER 4**

THE NANOCOMPUTER (NBZ80) AND THE SUPER NANO 47

COMPUTER (NBZ80S)

47

Objectives — The Nanocomputer — Central Processing Unit (CPU)

47

— Rules for Setting up Experiments — Experiment Instructions

47

Format — A Word of Caution — Introduction to the Experiments

47

— Experiment No. 1 — Experiment No. 2 — Experiment No. 3 —

47

— Experiment No. 4 — Experiment No. 5

47

Some Simple Z-80 Microcomputer Programs 79 Objectives — Review of Several Z-80 Instructions — Programming Languages and Listings — Assembly Language Programming — Introduction to the Experiments — Experiment No. 1 — Experiment No. 2 — Experiment No. 3 — Experiment No. 4 — Experiment No. 5 — Review

#### **CHAPTER 6**

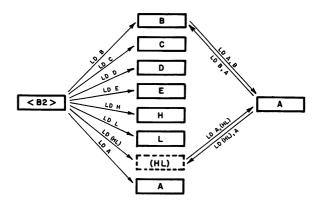

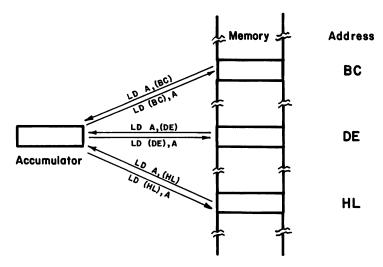

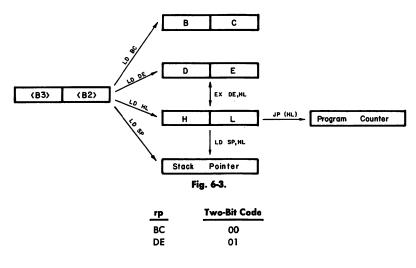

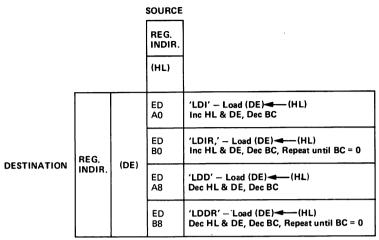

**REGISTERS, MEMORY, AND DATA TRANSFER** Objectives - Z-80 Instruction Set - Z-80 Addressing Modes - Single Register Load Instructions: Register Addressing Mode LD d.s -Load Immediate to Register - Register Indirect Load With Accumulator LD A, (rp); LD (rp), A - Load Immediate Extended Pair LD rp <B3><B2> — Load Extended Pair LD rp, (addr); LD (addr), rp - Increment Register - Decrement Register - Jump if not Zero JP NZ, <B3><B2> — Block Data Transfers LDD, LDI, LDDR, LDIR - Introduction to the Experiments - Experiment No. 1 — Experiment No. 2 — Experiment No. 3 — Experiment No. 4 — Experiment No. 5 — Experiment No. 6

#### **CHAPTER 7**

Z-80 Addressing Modes

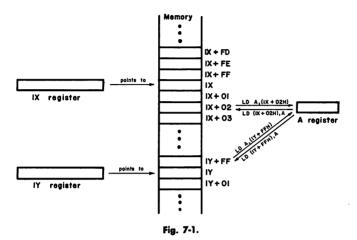

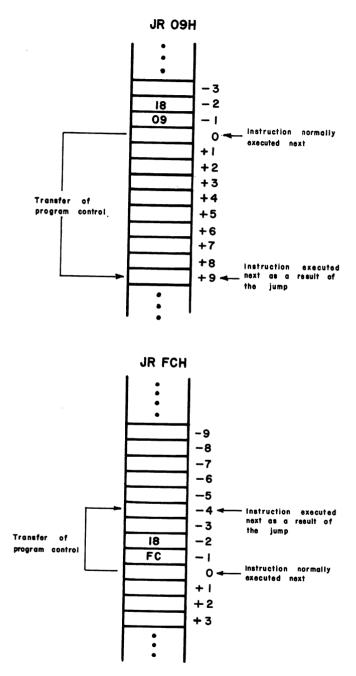

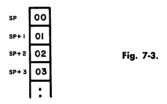

Objectives — What Is an Addressing Mode? — Two's Complement Binary Representation - Two's Complement Addition and Subtraction - The Z-80 Address Modes - Register Addressing - Immediate Addressing - Immediate Extended Addressing - Register Indirect Addressing - Extended Addressing - Modified Page Zero Addressing — Implied Addressing — Bit Addressing — Indexed Addressing — Relative Addressing — The Instruction Group Tables - The 16-Bit Load Group - Block Transfer and Exchanges - Introduction to the Experiments and Exercises - Review - Experiment No. 1 — Experiment No. 2 — Experiment No. 3

#### CHAPTER 8

#### JUMPS, CALLS, AND RETURNS .

Instructions — Flags and Conditional Jumps — Calls and Returns - Introduction to the Experiments - Experiment No. 1 - Experiment No. 2 — Experiment No. 3 — Experiment No. 4 — Experiment No. 5

#### **CHAPTER 9**

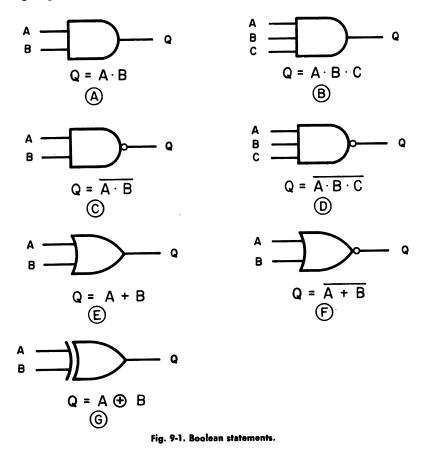

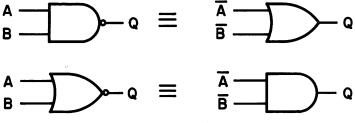

LOGICAL INSTRUCTIONS . What Is a Logical Instruction? — Boolean Algebra — Multibit Operations - NOT - De Morgan's Theorem - Z-80 Logical Instruction Group — Complement Accumulator: CPL — AND With Accumulator: AND - Exclusive-or With Accumulator: XOR - OR With Accumulator: OR — Logical Instructions and External Device Monitoring — Introduction to the Experiments — Experiment No. 1 — Experiment No. 2 — Review

139

205

175

99

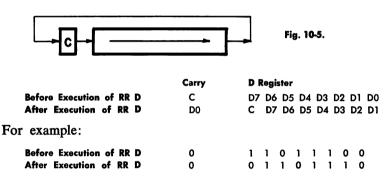

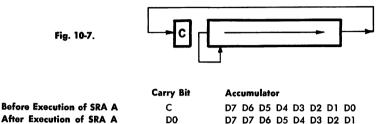

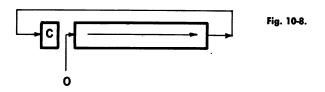

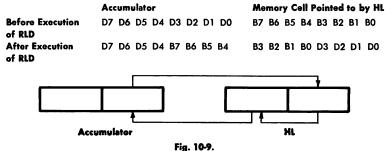

BIT MANIPULATION, ROTATE AND SHIFT INSTRUCTIONS . . 223 Objectives — Bit, Set, Test and Reset Process — ROTATE and SHIFT Instruction Group — ROTATE Instructions — SHIFT Instructions — Introduction to the Experiments — Experiment No. 1 — Experiment No. 2 — Experiment No. 3

#### CHAPTER 11

#### APPENDIX A

| SUMMARY OF Z-80 OP CODES AND EXECUTION TIMES | • | • | . 267 |

|----------------------------------------------|---|---|-------|

| APPENDIX B                                   |   |   |       |

| Z-80 CPU INSTRUCTIONS SORTED BY MNEMONICS .  | • | • | . 279 |

| APPENDIX C                                   |   |   |       |

| Z-80 CPU INSTRUCTIONS SORTED BY OP CODE      | • | • | . 283 |

| APPENDIX D                                   |   |   |       |

| COMPUTATION OF EXECUTION TIMES               | • | • | . 287 |

| APPENDIX E                                   |   |   |       |

| PRECAUTIONS WHILE HANDLING MOS DEVICES       | • | • | . 291 |

| APPENDIX F                                   |   |   |       |

| Master Symbol Table                          | ٠ | • | . 293 |

| APPENDIX G                                   |   |   |       |

| <b>References</b>                            | • | • | . 295 |

| INDEX                                        |   |   | . 297 |

### **Digital Codes**

#### INTRODUCTION

Before you begin to program your microcomputer, it is necessary that you understand how to convert 8-bit binary numbers into hexadecimal code, and vice versa, as well as know certain basic facts about digital codes.

#### **OBJECTIVES**

At the completion of this chapter, you will be able to do the following:

- Discuss what is meant by the term communication.

- Define bit.

- Define binary code.

- Define digital code.

- Define hexadecimal code.

- Convert an 8-bit binary number into a two-digit hexadecimal number.

- Convert a two-digit hexadecimal number into a binary number.

- Distinguish between the binary, hexadecimal, and decimal counting systems.

- List several different digital codes.

- List several different two-state devices.

- Provide one example where the quantity, bits per second, is a measure of information flow.

#### LANGUAGES, COMMUNICATIONS, AND INFORMATION

One of the most important characteristics that any biological organism (higher order animals) possesses is the ability to communicate with other organisms of the same species. The ability to communicate, which gives many animal organisms a definite survival advantage in the Darwinian sense of the term—is found in most multicellular creatures, starting with insects and progressing to man. With insects, there exist several modes of communication, including the dance of the bee and forms of chemical communication through remarkable chemical agents called *pheromones*. Man can communicate with the aid of his five senses, as illustrated by handicapped individuals who have lost one or more of their senses but are, nevertheless, highly communicative with those remaining.

Assuming that an individual wishes to communicate with another through the sense of hearing and the use of speech, it is clear that there must be some general agreement concerning how a spoken sound will be interpreted by the individual who hears it. Over the centuries, different regions around the world have each developed their own consensus regarding the meaning of specific sounds and their transcription onto paper. We call such a consensus a *language* or, perhaps, a *foreign language*. Thousands of different languages exist, although only a relatively modest number of them are in widespread use. The popularity of a specific language may wax and wane over the course of several hundred years. Latin, once a dominant language in Europe, is now considered to be a "dead" language, however, it clearly has influenced most of the European languages in very profound ways.

Communication can be defined as the imparting, conveying, or exchanging of ideas, knowledge, information, etc. (whether by speech, writing, or signs).<sup>1\*</sup> It is one of the most important and characteristic activities of mankind. As pointed out by James Martin in his excellent book, *Telecommunications and the Computer*,<sup>3</sup> the capacity of major telecommunication links, as measured by a quantity called *bits per second*, has paralleled the advance of civilization over the past one hundred years. The capacity of such links has changed from a rate of 1 bit/second in 1840 to 50,000,000 bits/second in 1970, i.e., a doubling every 5.08 years. Martin has also pointed out that the sum total of human knowledge changed very slowly prior to the relatively recent beginnings of scientific thought. By 1800, it has been estimated that the sum total was doubling every 50 years; by 1950, doubling every 10 years; and that by 1970, it will be doubling every 5 years.

A language, which can be defined as the whole body of words and of methods of combination of words used by a nation, people, or race,<sup>1</sup> is just one form of communication. Egyptian hieroglyphics, choreographic scores, mathematical symbols and equations, Ameri-

<sup>\*</sup> See Appendix G for all references.

can Indian smoke signals, the sign language employed by the deaf, and the Morse code are other forms of communication used by man.

#### **BINARY CODING**

The "information explosion" would have inundated mankind, at least in the more advanced countries, had it not been for the use of Two-State Coding to represent all kinds of information. such as the ten decimal numerals (0 through 9), the twenty-six letters of the English alphabet (A through Z), operations, symbols, motions, and the like. We call such two-state coding Off-On or binary coding. Binary coding can be represented or manifested by any type of twostate device, such as an on or off light, an open or closed switch, a punched or nonpunched computer card, a "north" or "south" magnetized magnetic core or region of magnetic tape or disc; two different voltage levels, two different current levels, two different frequencies; the words YES and NO; or the abstract symbols 0 (off) and 1 (on). The importance of binary coding resides in the fact that it is possible to construct devices that will change state very quickly, in times as fast as 5 nanoseconds (0.000000005 second). Such a device could, in principle, manipulate, transmit, or receive information at the rate of 200 million bits per second. Thirty-two such devices, operating simultaneously, could manipulate 6.4 billion bits per second. This is the basic capability that has permitted society to store, manipulate, and communicate enormous quantities of information.

#### BIT

The elementary unit of information is called the bit, which is an abbreviation for **BI**nary digi**T**. You can think of a bit as being a light bulb that can be lit (on) or unlit (off) at any given time. Thus, a bit can be pictured as a light bulb that is ON or a light bulb that is OFF. Rather than drawing pictures of light bulbs, we can represent each bulb that is in the lit state by the symbol 1 and each bulb in the unlit state by the symbol 0.

So, a bit is equal to one binary decision, or the designation of one of two possible and equally likely values or states (such as 0 or 1).

Information is typically represented by a series of bits. Thus,

1000

represents decimal 8 in binary code. The series of bits,

11000001

represents the letter A in 8-bit ASCII code. We shall discuss these two codes shortly.

#### **DIGITAL CODES**

A *digital code* is defined as a system of symbols that represent data values and make up a special language that a computer or a digital circuit can understand and use.<sup>3</sup> Digital codes can be considered to be the digital "languages" that permit information to be stored, manipulated, and communicated. Just as there are numerous spoken languages, there also exists a variety of digital codes. Such codes can be subdivided into several important categories:

- Category 1. Codes employed by electronic circuitry to perform various digital operations. Example: binary code.

- Category 2. Codes employed to convert the decimal numbers 0 through 9 into digital form. Examples: binary code, binary coded decimal (bcd), and gray code.

- Category 3. Codes employed to convert decimal numbers, the 26letter English alphabet, symbols, and operations into digital form. Examples: ASCII code, EBCDIC code, and Baudot code.

- Category 4. Instruction codes employed by large computers, minicomputers, and microcomputers that cause the computers to perform a prescribed sequence of operations. Examples: IBM 370 instruction code, PDP 8/E instruction code, Z-80 instruction code.

In this series of modules, we shall pay particular attention to four codes: binary code, binary coded decimal (bcd), ASCII code, and the instruction code for the Z-80 microprocessor chip.

#### **BINARY CODE**

The simplest digital code is a two-state, or binary, code that consists of a 0 (off) and a 1 (on) state. We call these two states *logic 0* and *logic 1*. In binary code, decimal 0 is represented by a logic 0 and decimal 1 by a logic 1. This should be quite clear. How, on the other hand, are higher decimal numbers, such as 3, 17, 568, etc., represented using binary code? The answer is that we use a series of bits to build a *binary counting system* that is formed on a *base*, or *radix*, of two. For example, the binary number  $11101_2$ , where the subscript (2) represents the binary counting system, is equivalent to

$11101 (2) = (1 \times 2^{**4}) + (1 \times 2^{**3}) + (1 \times 2^{**2}) + (0 \times 2^{**1}) + (1 \times 2^{**0}) = 29 (10)$

where you should keep in mind that  $A^{**B}$  is equivalent to  $A^{B}$ . Therefore,

$2^{**4} = 16$  in decimal notation  $= 16_{10}$  $2^{**3} = 8$  in decimal notation  $= 8_{10}$  $2^{**2} = 4$  in decimal notation  $= 4_{10}$

$$2^{**1} = 2$$

in decimal notation =  $2_{10}$

$2^{**0} = 1$  in decimal notation =  $1_{10}$

Therefore,

$$11101(2) = 16(10) + 8(10) + 4(10) + 0 + 1(10) = 29(10)$$

where the subscript (10) associated with these numbers represents the decimal counting system, a system that is formed on a base, or radix, of 10. A brief table follows that allows you to convert simple decimal numbers into binary numbers.

| Decimal Number | Binary Number |

|----------------|---------------|

| 0              | 0000          |

| 1              | 0001          |

| 2              | 0010          |

| 3              | 0011          |

| 4              | 0100          |

| 5              | 0101          |

| 6              | 0110          |

| 7              | 0111          |

| 8              | 1000          |

| 9              | 1001          |

| 10             | 1010          |

| 11             | 1011          |

| 12             | 1100          |

| 13             | 1101          |

| 14             | 1110          |

| 15             | 1111          |

| 16             | 10000         |

Thus, a series of four binary digits, or bits, can represent any of sixteen different decimal numbers ranging from zero to fifteen. Decimal numbers larger than fifteen require additional bits, as shown in the following table:

| Decimal Number | Binary Number |

|----------------|---------------|

| 0              | 0             |

| 1              | 1             |

| 2              | 10            |

| 3              | 11            |

| 4              | 100           |

| 7              | 111           |

| 8              | 1000          |

| 15             | 1111          |

| 16             | 10000         |

| 31             | 11111         |

| 32             | 100000        |

| 63             | 11111         |

| 64             | 1000000       |

| 127            | 111111        |

| 128            | 1000000       |

| 255            | 1111111       |

| 256            | 10000000      |

| 511    | 11111111          |

|--------|-------------------|

| 512    | 100000000         |

| 1023   | 111111111         |

| 1024   | 1000000000        |

| 2047   | 111111111         |

| 2048   | 10000000000       |

| 4095   | 11111111111       |

| 4096   | 100000000000      |

| 8191   | 1111111111111     |

| 8192   | 10000000000000    |

| 16,383 | 11111111111111    |

| 16,384 | 100000000000000   |

| 32,767 | 1111111111111111  |

| 32,768 | 1000000000000000  |

| 65,535 | 11111111111111111 |

Therefore, an 8-bit binary number can encode two hundred and fifty-six different decimal numbers, ranging from 0 to  $255_{10}$ , or two hundred and fifty-six different "things," no matter what they may be (instructions, devices, pulses, etc.). The Z-80 is a microprocessor chip that has a 16-bit memory address and an 8-bit I/O device word. This means that it can directly address 65,536 different memory locations and can generate at least 256 different I/O pulses or device addresses.

#### **HEXADECIMAL (HEX) CODE**

It can be difficult to remember binary numbers that contain many bits. For example, can you remember the following 8-bit binary number,

#### 10011101

after having looked at it for only one second? Quick, cover it up or look away! Consider also the problem of remembering a list of such 8-bit numbers:

You probably will conclude that there must be a better way to remember 8-bit binary numbers. We are using 8-bit numbers here because you will encounter them frequently when you begin to program the 8-bit Z-80 microcomputer.

One approach to remembering multi-bit binary numbers is the use of *hexadecimal code*. The term *hex* is simply an abbreviation for the word *hexadecimal*. Hexadecimal code refers to the *hexadecimal counting system*, a system that is formed on a base, or radix, of 16. The hexadecimal counting system consists of sixteen different symbols: 0,1,2,3,4,5,6,7,8,9,A,B,C,D,E, and F. Just as we did with decimal numbers, it is possible to convert hexadecimal numbers into binary numbers:

| Decimal Number | Hex Number | Binary Number |

|----------------|------------|---------------|

| 0              | 0          | 0000          |

| 1              | 1          | 0001          |

| 2              | 2          | 0010          |

| 3              | 3          | 0011          |

| 4              | 4          | 0100          |

| 5              | 5          | 0101          |

| 6              | 6          | 0110          |

| 7              | 7          | 0111          |

| 8              | 8          | 1000          |

| 9              | 9          | 1001          |

| 10             | Α          | 1010          |

| 11             | В          | 1011          |

| 12             | С          | 1100          |

| 13             | D          | 1101          |

| 14             | E          | 1110          |

| 15             | F,         | 1111          |

| 16             | 10         | 0001 0000     |

| 17             | 11         | 0001 0001     |

| 18             | 12         | 0001 0010     |

| 19             | 13         | 0001 0011     |

| 20             | 14         | 0001 0100     |

| 21             | 15         | 0001 0101     |

| 22             | 16         | 0001 0110     |

| 23             | 17         | 0001 0111     |

| 24             | 18         | 0001 1000     |

| 32             | 20         | 0010 0000     |

| 40             | 28         | 0010 1000     |

| 48             | 30         | 0011 0000     |

| 56             | 38         | 0011 1000     |

| 63             | 3F         | 0011 1111     |

We have grouped the 8-bit binary numbers into two groups of four bits each to help you understand how the hexadecimal number to binary number conversion was made. While the space between each 4-bit group does not affect the value of the number, it does make the binary number easier to read and has become a standard convention.

We now address the question of how to convert an 8-bit binary number into hex code. The procedure to accomplish this conversion requires three steps:

- 1. Write down the full 8-bit binary number.

- 2. Split this 8-bit binary number into two groups with four binary digits in each group.

- 3. Substitute the equivalent hex digit

0,1,2,3,4,5,6,7,8,9,A,B,C,D,E,F

for each group of four bits.

Having done this you will have converted an 8-bit binary number into a two-digit hex code. Each group of four binary digits is converted independently of the other.

As an example, consider the 8-bit binary number,

First, split this binary number into two groups of four binary digits each

#### 1001 1101

Finally, substitute the equivalent hex digit for each of these two groups.

#### 9 D

This is the correct answer, 9D (16), where the subscript (16) means "relative to" the hexadecimal counting system. Some additional hex numbers and their corresponding 8-bit binary numbers are listed below:

| Decimal Number | Binary Number | Hex Number |

|----------------|---------------|------------|

| 64             | 0100 0000     | 40         |

| 72             | 0100 1000     | 48         |

| 73             | 0100 1001     | 49         |

| 74             | 0100 1010     | 4A         |

| 96             | 0110 0000     | 60         |

| 120            | 0111 1000     | 78         |

| 127            | 0111 1111     | 7F         |

| 128            | 1000 0000     | 80         |

| 160            | 1010 0000     | A0         |

| 184            | 1011 1000     | B8         |

| 191            | 1011 1111     | BF         |

| 248            | 1111 1000     | F8         |

| 255            | 1111 1111     | FF         |

#### A NOTE ON NOTATION

It may have occurred to you that dealing with all of these different methods of number representation—binary, hex, and decimal—that there is a possibility for some confusion. For example, the number 10 can be a decimal or a hex or a binary number. To remedy this problem, whenever there is any possibility for ambiguity, all hexadecimal numbers will be followed by the letter H, e.g., 10H, all decimal numbers will be followed by a period or decimal point, e.g., 10., and all binary numbers will appear without any special notation, e.g., 10 or 0110.

#### DEMONSTRATIONS

In the first three chapters we have included a collection of exercises that we have called demonstrations. These demonstrations are designed to encourage you to operate the Nanocomputer immediately, even though you may not completely understand the Nanocomputer at this time. It is important that you work through these demonstrations even though you may feel at times that you are only pushing buttons and not understanding what is happening.

#### DEMONSTRATION NO. 1

#### Step 1

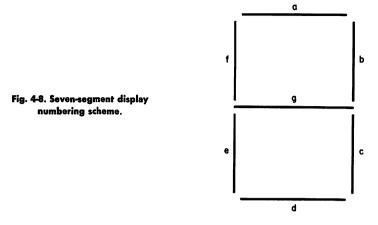

Referring to the Nanocomputer Instruction Manual, apply power to your Nanocomputer. Press the RESET key. Several seven-segment display digits should become lit. If not, press RESET again. If repeated depressions of the RESET key do not "bring up" your Nanocomputer, you have a problem.

#### Step 2

Notice that the Nanocomputer keyboard has two keys with arrows on them. Press one of these keys several times and observe what happens.

We observed three things. First, we observed that the red selector lamp cycles among eleven different possible positions. We also observed that the red lamp can be moved one step at a time by quickly touching and releasing the key; alternatively, the red lamp can be made to cycle automatically by holding down the key and then releasing the key when the selector lamp reaches the desired location.

Finally, we observed that the digits appearing on the red digit displays changed according to the position of the red selector lamp.

#### Step 3

Press the other key that is labeled with an arrow and observe what happens.

We observed that the red selector lamp cycled among the eleven different possible positions in the opposite direction from that observed in STEP 1.

#### Step 4

Position the selector lamp at the position labeled MEM. Notice what appears on the four leftmost red digit displays.

We observed 0000.

#### Step 5

Press the key labeled INC several times and notice what happens. We observed the following sequence of digits appearing on the leftmost red digit display:

0000

0001

0002

0003

0004

0005

0006

0007

0008

0009

000A

000b

000C

000d

000E

000F

0010

0011

0012

0013

and so on.

Notice that the hexadecimal digit sequence 0,1,2,3,4,5,6,7,8,9,A, b,C,d,E,F is displayed, right justified, in each group of four digits. Notice also that the hexadecimal digits A,C,E, and F appear as capital letters, but that the hexadecimal digits b and d appear as lower case letters. This is simply an artifact of the seven-segment display that is being used to represent the letter, and henceforth will be represented by B and D, respectively. The four place hexadecimal digits 0000 through 000F represent the decimal digits 0 through 15, the hex digit 0010 represents the decimal digit 16, 0011 represents 17., and so on. Thus, we have a hexadecimal display. The conclusion is that the Nanocomputer is going to talk to us using the hexadecimal representation of numbers so it makes sense that we will talk to the Nanocomputer using the same hexadecimal (hex) representation.

#### Step 6

Press the button labeled RESET. Notice that the selector lamp has moved. Move the selector lamp back to the location labeled MEM. We now have 0000 displayed once again, so that subsequent pushing of the INC key will cause the Nanocomputer to begin displaying successive hex digits. What is the largest hex number that the Nanocomputer will be able to display using only these four hex digits? What is the decimal equivalent of this number?

Answer: The largest hex number that the Nanocomputer can display is FFFF. The decimal equivalent of this number is 65,535.

#### REVIEW

The following questions will help you review digital codes.

- 1. What is a digital code?

- 2. List several different types of digital codes.

- 3. How many bits are there in the following binary numbers?

- a. 11010011

- b. 10000000000011

- c. 1001

- 4. To what decimal numbers do the following binary numbers correspond? a. 11101

- Ь. 11111111

- c. 1111111111111111

- d. 1001

- e. 11010011

- f. 10011

- 5. To what hexadecimal numbers do the following binary numbers correspond? a. 11010011

- b. 00111110

- c. 01110110

- d. 00111100

- e. 11111111

- f. 00110010

- g. 11000011

- h. 00000010

- i. 110

- 6. To what binary numbers do the following hexadecimal numbers correspond? a. D3H

- b. FFH

- c. 32H

- d. 3EH

- e. 76H

- f. 02H

- g. 5H

- h. 3CH

- i. **00H**

#### 7. What is meant by the following subscripts?

- a. (16)

- b. (10)

- c. (2)

- 8. Define the following terms.

- a. hexadecimal counting system

- b. bit

- c. binary code

- d. communication

- e. language

- 9. Are the following numbers binary, hex, or decimal?

- a. 1111

- b. 1101.

- c. 1100H

#### ANSWERS

- 1. A digital code is a system of symbols that represent data values and make up a special language that a computer or a digital circuit can understand.

- 2. Binary code. Binary coded decimal. Gray code. ASCII code. EBCDIC code. Baudot code. IBM 370 instruction code. Z-80 instruction code.

- 3. a. Eight

- b. Sixteen

- c. Four

- 4. a. 29.

- b. 255.

- c. 65,535.

- d. 9.

- e. 211.

- f. 19.

- 5. a. D3H

- b. 3EH

- c. 76H

- d. 3CH e. FFH

- e. FFH f. 32H

- 1. 32H g. C3H

- b. 02H

- i. 06H

- 6. a. 11010011

- b. 11111111

- c. 00110010

- d. 00111110

- e. 01110110

- f. 00000010

- g. 101

- h. 00111100

- i. 00000000

- 7. a. Refers to the hexadecimal counting system

- b. Refers to the decimal counting system

- c. Refers to the binary counting system

- 8. a. A counting system that is based on a base, or radix of 16

- b. An elementary unit of information that is equal to one binary decision, or the designation of one of two possible and equally likely values or states of anything used to store or convey information.

- c. A code in which each code element is one of two different states, which are commonly known as logic 0 and logic 1.

- d. The imparting, conveying, or exchanging of ideas, knowledge, information, etc., (whether by speech, writing, or signs).

- e. The whole body of words and of methods of combination of words used by a nation, people, or race.

- 9. a. binary

- b. decimal

- c. hexadecimal

## An Introduction to Microcomputer Programming

In the chapters that follow, you will perform two different kinds of experiments: (a) experiments that require only microcomputer programming, and (b) experiments that require both microcomputer programming and *interfacing*, i.e., the wiring of circuits that connect the microcomputer to some kind of external device. Since a common denominator of all experiments is programming, we would first like to introduce you to the basic principles of programming and the characteristics of the *programming language* that you will use in this text: the instruction set for the Z-80 microprocessor chip. Along the way, we shall define a variety of important terms, including *computer*, *mnemonic language, machine language, microcomputer*, and many others. This introduction to programming will occupy twelve chapters. We prefer to give you new programming instructions in groups of five to ten, rather than all of them at once.

#### **OBJECTIVES**

At the end of this chapter, you will be able to do the following:

- Define *digital computer*.

- Define *microcomputer*.

- Distinguish between microcomputer instructions written in binary code, hex code, or mnemonic code.

- Distinguish between mnemonic representations and machine language.

- Define byte.

- Convert a 16-bit memory address into HI and LO address bytes.

- Convert 8-bit binary-coded instructions into hex-coded instructions, and vice versa.

- Distinguish between read/write memory and read-only memory.

- Define *memory*.

- Define computer program.

- State the range of memory locations, in binary or hex code, for your microcomputer.

- Identify 8-bit bytes in a list of binary numbers.

#### WHAT IS A COMPUTER?

There are many different types of computers in the world—DIGI-TAL COMPUTERS, ANALOG COMPUTERS, FLUIDIC COM-PUTERS, MECHANICAL COMPUTERS. In this book, you will be concerned only with DIGITAL COMPUTERS, which comprise probably 99% of all of the computers in use today. A digital computer can be defined as follows:

Digital computer—An electronic device that is capable of accepting, storing, and arithmetically manipulating information, which includes both data and the controlling program. The information is handled in the form of coded binary digits (0 and 1) that are represented by dual voltage levels.<sup>4</sup>

—Any device, usually electronic, capable of accepting information, comparing, adding, subtracting, multiplying, dividing, and integrating this information, which is in the form of coded binary digits (0 and 1), and then supplying the results of these processes in acceptable form. The major elements of a digital computer usually include memory, control, arithmetic, logical, and input and output facilities.<sup>2</sup>

It should be emphasized that a digital computer manipulates *binary information*, of the kind that we discussed in Chapter 1. The binary information is usually in the form of *digital codes:* instruction codes; codes used to represent decimal numbers in digital form; codes employed by electronic circuitry to perform various digital operations; and codes used to represent in digital form the alphabet, decimal numbers, symbols, and other operations.

#### WHAT IS A MICROCOMPUTER?

A microcomputer is a fully operational digital computer that is based on a microprocessor chip. A microprocessor is a single integrated-circuit chip that possesses at least 75% of the computing and data manipulation power of a digital computer. It usually cannot function without the aid of support chips and memory. An *integrated-circuit chip* is an electronic device in which both active (i.e., transistors) and passive (i.e., resistors) elements are contained within a single package. In digital electronics, the term chiefly applies to circuits containing semiconductor elements.<sup>2</sup> The microprocessor chip is a product of advanced technology in the semiconductor industry, basically the capability that manufacturers now have to fabricate thousands of transistors on a single silicon chip no larger than 60 to 80 square millimeters.

#### WHAT IS A COMPUTER PROGRAM?

A computer program can be defined as a series of instructions or statements prepared in a form acceptable to the computer, the purpose of which is to achieve a certain result.<sup>2</sup> This definition does not imply what the desired result may be. For example, you may simply be interested in rearranging input digital data into a more convenient form, which is either stored or provided as output. With microcomputers, you will be increasingly interested in writing microcomputer programs that control the operation of a device or machine. In a home clothes washer, you may wish to control the amount of water used, the temperature of the water at different washing cycles, the number and kinds of cycles used to wash a particular type of fabric, and the time duration of each cycle. All this can be done with a properly written computer program.

#### INSTRUCTIONS

A computer *instruction* can be defined as a set of characters that define an operation. Either alone, or with other information, an instruction causes a digital computer to perform the operation or manipulate the indicated quantities.

A character is one symbol of a set of elementary symbols, such as those corresponding to typewriter keys. Symbols usually include the decimal digits 0 through 9, the letters A through Z, punctuation marks, dollar signs, commas, operation symbols, and any other single symbols that a computer may read, store, or write.<sup>5</sup> In computer programming, it is not uncommon for one to use the entire typewriter keyboard, including symbols such as @, #, \$, %, &, \*, (, ), /, and possibly others.

Computer instructions may be expressed in a variety of forms. They may be expressed as binary numbers,

11010011 00111110 hex numbers,

D3H 3EH

mnemonic code,

#### OUT 3EH LD A,02H

full words,

#### OUTPUT ACCUMULATOR DATA TO DEVICE #3E (HEX) LOAD DATA 02 HEX INTO REGISTER A

or full mathematical expressions,

$X = A^{**2} + B^{*y} + C$

In this book, we will express instructions at the level of binary numbers, hex numbers, and mnemonic representations.

#### **MNEMONICS**

Mnemonic is a term that describes something used to assist the human memory. In view of this definition, we have the following:

- *mnemonic code*—Computer instructions written in a form the programmer can easily remember, but which must be converted into machine language later by a computer or by the user.<sup>2</sup>

- mnemonic language—A programming language that is based on easily remembered symbols and that can be assembled into machine language by a computer.<sup>2</sup>

- mnemonic operation—Computer instructions that are written in a meaningful notation, for example, ADD, LD, and OUT.<sup>2</sup>

#### INSTRUCTIONS

In this series of chapters, we shall occasionally employ the mnemonic codes for the instructions that you will use when you program the microcomputer. The mnemonic codes will be those suggested by the ZILOG Corporation for its Z-80 microprocessor instruction set, which contains 158 different machine instruction types. With time, you should be able to readily convert from machine language (i.e., binary code) to mnemonic code, and vice versa.

#### **MACHINE LANGUAGE**

The modern electronic digital computer is capable of performing manipulations using binary electronic signals, typically two voltage levels (+5 volts and ground potential) that represent the logic states 1 and 0, respectively. Thus, each computer instruction is written as a series of 1s and 0s that specifically characterize that instruction and no other. Such a binary representation of a computer instruction is called *machine language* or *machine code*. For example, the machine language instruction 00000111 rotates the contents of the accumulator within the Z-80 microprocessor chip one bit to the left. The instruction, 00001111, rotates the contents of the accumulator one bit to the right.

In this series of chapters, you will be drilled in the use of machine language instructions for the Z-80 microprocessor. The instructions will be given to you in HEX CODE in order that you may remember them easier. Some hex instruction codes that you will soon use in simple microcomputer programming experiments include:

| СЗН | Unconditional jump instruction         |

|-----|----------------------------------------|

| 76H | Halt instruction                       |

| 3CH | Increment contents of accumulator by 1 |

| 3EH | Load accumulator immediate instruction |

All of the new phrases that have been used in this section—unconditional jump, load, halt, increment, etc.—will be discussed shortly.

#### A SIMPLE PROGRAM

Let us examine the following simple Z-80 program.

| <b>00H</b> | No operation                                    |

|------------|-------------------------------------------------|

| 3EH        | Load the contents of the next program byte into |

|            | the accumulator                                 |

| FFH        | Data byte                                       |

| 76H        | Halt                                            |

It contains three instructions and one data byte. In this case, the program has been written in hex code, which you have studied in Chapter 1. This very same program also could have been written in binary code, as shown below.

| 00000000 | No operation                               |

|----------|--------------------------------------------|

| 00111110 | Load the contents of the next program byte |

|          | into the accumulator                       |

| 1111111  | Data byte                                  |

| 01110110 | Halt                                       |

Alternatively, it could have been written in mnemonic code and later converted to machine code with the aid of a special program called an *assembler*. Thus, we have the following mnemonic program:

| NOP      | No operation                               |

|----------|--------------------------------------------|

| LD A,FFH | Load the data byte FF into the accumulator |

| HALT     | Halt                                       |

Note that the mnemonic code program is mainly words or word abbreviations, such as NOP, HALT, and LD.

How does the microcomputer execute this program? It does so step by step, with the first instruction, NOP, being the first executed. The following sequence of operations occurs:

- 1. The microcomputer executes the NOP instruction, which causes the computer to "pause" for one *instruction cycle*. The computer then advances to the next instruction. There is an important use for the NOP instruction, which you will see in a later program.

- 2. As the microcomputer executes the LD instruction, which has the 3E hex code, it looks at the next memory location to determine what value to load into the accumulator.

- 3. The microcomputer goes to the next memory location, where it finds an FF. It takes this value and stores it in the accumulator of the microcomputer.

- 4. The microcomputer executes the final instruction, HALT. This causes the computer to stop.

The above program may seem straightforward, or it may not. What is *memory*? What is a *byte*? How does one distinguish between an *instruction* and a *data byte*? Where is the accumulator? All of these are very reasonable questions, some of which you may have asked yourself as you studied the above program.

Let us proceed to answer some of these questions.

#### BYTE

A byte is a group of eight contiguous bits that occupy a single memory location in a Z-80 based microcomputer. By "contiguous," we mean adjacent or neighboring, or one-after-the-other. A byte can be any of the 256 possible different arrangements of eight binary digits each of which is either a 0 or a 1. The only restriction is that a byte contains exactly eight bits. Thus, the binary number,

#### 01101001

is a byte, whereas the binary number,

#### 101001

is not a byte since it contains only six bits. The term, byte, has become popular because many digital computers have word lengths that are multiples of eight bits. To easily reference bits within a byte, the bits are numbered from 0 through 7:

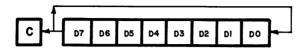

D7 D6 D5 D4 D3 D2 D1 D0

The "D" (probably short for Data) is sometimes not present. The most significant bit (MSB) is D7. The least significant bit (LSB) is D0.

In general, a *word* is the number of bits that a computer can manipulate simultaneously. If the number of bits in a *word* is eight, we usually employ the term byte rather than *word*. In any case, the Z-80 has an 8-bit *word* length. The word length for a PDP 8 minicomputer is twelve, which means that the PDP 8 minicomputer manipulates twelve bits at a time when it is executing a program. The PDP 11 minicomputer has a word length of sixteen bits, and large computers generally have word lengths of 32 bits, 36 bits or 60 bits.

#### MEMORY

*Memory* can be defined as any device that can store logic 1 and logic 0 bits in such a manner that a single bit or group of bits can be accessed and retrieved.<sup>6</sup> There are many different types of memory that satisfy this requirement; in your microcomputer, however, you have only two different kinds of memory:

read/write memory—A semiconductor memory into which logic 0 and logic 1 states can be written (stored) and read out again (retrieved).<sup>6</sup> These are also called *random access memories* (RAM). read-only memory—A semiconductor memory from which digital data can be repeatedly read out, but cannot be written into as in the case for read/write memory.<sup>6</sup> Abbreviated ROM.

Actually, the read-only memory in your microcomputer may be a special kind of memory called an *erasable programmable read-only memory*, or EPROM. We shall talk about EPROMs in a subsequent chapter.

The important point here is that your memory consists of semiconductor devices. They are fast and relatively inexpensive, have no mechanical parts, and do not take up much room on your printed-circuit board. They are one reason why computer technology has advanced as fast as it has.

How much memory do you have? The simplest Nanocomputer that you can use contains 4096 bytes of read/write memory and 2048 bytes of read-only memory. The program which allows you to enter data on the keyboard and displays information on the seven-segment displays is loaded into the 2048 bytes of read-only memory. We will refer to this program as the Nanocomputer operating system.

Since a byte contains eight bits, this means that you have at least a total of 49,152 bits of memory in your microcomputer. This is sufficient for all programming and interfacing experiments that you will encounter throughout this book.

On the second level Nanocomputer you are able to increase the number of bytes of read/write memory to 16,384 and increase the number of bytes of read-only memory to 8192. A Nanocomputer with

this memory capacity has a total of 24,576 bytes of memory. It is known as a 24K microcomputer, where the "K" represents roughly one thousand (exactly 1024) different memory locations. A 4K microcomputer would contain 4096 bytes of memory. A 64K micro-computer would contain 65,536 bytes of memory.

#### **MEMORY ADDRESS**

*Memory address* is defined as the storage location of a memory word. Note that we said word, not byte. For some computers, a word may contain 32 bits, so each different memory location will contain 32 bits. For the Z-80 microcomputer, each memory location contains a single byte, i.e., eight bits.

With the standard Nanocomputer that you can use, there are 6144 different memory locations. These memory locations are subdivided into two groups, which can be described as follows:

- Memory group 1: The first group of 4096 (4K) memory locations, each containing eight bits. This is the read/write memory that you will normally use when you program your microcomputer.

- Memory group 2: The second group of 2048 (2K) memory locations, each containing eight bits. This memory region is occupied by read-only memory, or perhaps by erasable programmable read-only memory, which contains the Nanocomputer operating system that makes your microcomputer operate. YOU CANNOT CHANGE THE CONTENTS OF THIS MEMORY GROUP.

#### RANGE OF MEMORY LOCATIONS

The Z-80 microprocessor chip is quite remarkable, it can address up to 65,536 (64K) different memory locations, each containing eight bits. The chip contains a 16-bit memory address word. If you perform a simple calculation, you will conclude that 2 raised to the 16th power ( $2^{**}16$ ) does indeed equal 65,536.

As indicated above, your Nanocomputer may have only 6144 (6K) memory locations available on the basic card. You might ask, which locations among the possible 65,536 locations are they? Our answer: the first 4K locations together with the last 2K locations.

Stated in another way, the possible range of usable memory addresses for the standard Nanocomputer is:

00000000000000 (BASE 2) to 000011111111111 (BASE 2) R/W Memory 111110000000000 (BASE 2) to 1111111111111 (BASE 2) ROM This is a cumbersome notation, one that is very difficult to remember. There is an easier way to identify memory locations and the range of your microcomputer. This is discussed in the next section.

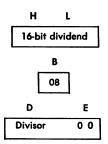

#### HI AND LO MEMORY ADDRESSES

It is difficult to remember a 16-bit memory address, considerably more so than an 8-bit instruction code or data byte. The Z-80 microprocessor chip treats a 16-bit memory address as two 8-bit memory address bytes, an 8-bit HI byte and an 8-bit LO byte. These are defined as follows:

- HI address byte—The eight most significant (or left-most) bits in the 16-bit memory address word for the Z-80 microprocessor chip. Abbreviated H or HI.

- LO address byte—The eight least significant (or right-most) bits in the 16-bit memory address word for the Z-80 microprocessor chip. Abbreviated L or LO.

Therefore, the possible range of read/write memory locations for your microcomputer is

Recall that you learned how to convert an 8-bit binary number into a 2-digit hex number. Applied to the above HI and LO memory addresses, you should obtain the following range of read/write memory locations:

Keep in mind the following rule: To specify a memory location, you must specify both the HI address byte and the LO address byte, which together comprise a memory address word of 16 bits.

#### **DEMONSTRATION NO. 1**

At each step in this demonstration, you should have the selector lamp located at the MEM position. Notice in Fig. 2-1 that there are four hex digits displayed on the left-hand side of the red digit displays,

Fig. 2-1. Memory location demonstration.

and that there are two hex digits displayed on the right-hand side. The four hex digits displayed on the left represent the address of a memory location. The two hex digits displayed on the right represent the contents of the memory location whose address is displayed on the left. You could think of memory as being a collection of boxes. Each box has a label permanently printed on it. These labels are actually hexadecimal numbers starting with 0000,0001,0002,0003, and so on. Inside each box you can put exactly one byte of information in the form of exactly two hex digits. Using the Nanocomputer keyboard you can examine individual memory locations and change the contents of a given memory location.

#### Step 1

Set the selector lamp on MEM. We observed that the memory address displayed in the left-most four hex digits, called the *address display*, was 0000. The contents of memory location 0000, displayed in the right-most two hex digits, called the *data display*, was 00.

Let us change the contents of 0000H from 00H to 23H. Push the hex key labeled 2, then push the hex key labeled 3, and finally, push the key labeled st. ST is a shorthand notation for the word STORE. By pressing st., you will STORE 23H in location 0000H. Notice that now the address has automatically increased to 0001. So you are now "looking" at memory location 0001H. Store 24H in this location.

#### Step 2

Now examine memory locations 0000H and 0001H to verify that you have actually stored 23H and 24H in them, respectively. Press 0,0,0,0 in sequence on the keyboard followed by the key labeled LA]. LA is shorthand for LOAD ADDRESS. You are loading the hex address 0000 into the address display. Now you should observe that 23 is displayed on the data display as the contents of memory location 0000H. Press the key labeled INC. Notice that the memory address is incremented by one and that the contents of memory location 0001H are indeed 24H. You now should be able to determine the contents of any memory location and to change the contents of any READ/ WRITE memory location to any value that you desire.

#### Step 3

You will look at the contents now of a memory location in ROM (Read-Only Memory) and attempt to write into Read-Only Memory. Look at the contents of FC00H (press F,C,0,0 in order and then press LA). We observed that the contents of FC00H was 31H. Attempt to store the hex value FF at this memory location (press F,F and then press the <u>sr</u> key). Now examine the contents of FC00H again. We observed that the contents of FC00H had not been changed, and are

still 31H. Thus we have NOT been able to write into read-only memory.

#### REVIEW

- 1. Identify the following instructions as to whether they are in binary code, hex code, or mnemonic code.

- a. HALT

- b. 11010011

- c. 3E

- d. LD

- e. INC

- f. 00111100

- g. 76

- 2. Write the following binary instructions in hex code.

- a. 11010011

- b. 01110110

- c. 00111100

- d. 00110010

- e. 00000000

- f. 11000011

- g. 11111111

- 3. Which of the following is a byte?

- a. 1001

- b. 011

- c. 0000001100000011

- d. 1110001101

- e. 111000

- f. 0100110

#### 4. Write the following 16-bit memory addresses as HI and LO hex bytes.

- a. 0000001111111111

- b. 0000000011111111

- c. 0000000111111111

- d. 0000001011111111

- e. 00000000000000000

- f. 00000010000000

- g. 00000100000000

- h. 0000001100000000

- 5. Which of the following instructions are in machine language?

- a. NOP

- b. HALT

- c. LD

- d. INC

- e. 3EH f. 76H

- g. 11010011

- h. 00H

- i. 00111100

- 6. In terms of the HI and LO memory address bytes, write the memory range of the following memory groups in the Z-80 microcomputer.

- a. The first 4K bytes of memory (read/write)

- b. The first 16K bytes of memory (read/write)

- c. The last 4K bytes of memory (read only)

- d. The last 8K bytes of memory (read only)

- 7. Define the following terms.

- a. byte

- b. memory address

- c. mnemonic code

#### ANSWERS

- 1. a. mnemonic code

- b. binary code

- c. hex code

- d. mnemonic code

- e. mnemonic code

- f. binary code

- g. hex code

- 2. a. D3

- b. 76

- c. 3C

- d. 32

- e. 00

- f. C3

- g. FF

- 3. None of the examples is a byte. A byte must contain exactly eight bits.

- 4. a. HI=03 LO=FF

- b. HI=00 LO=FF

- c. HI=01 LO=FF

- d. HI=02 LO=FF

- e. HI=00 LO=00

- f. HI=01 LO=00

- g. HI=02 LO=00

- h. HI=03 LO=00

- 5. Examples g and i are in machine language.

- 6. a. The Range is HI=00 and LO=00 to HI=0F and LO=FF

- b. The Range is HI=00 and LO=00 to HI=4F and LO=FF

- c. The Range is HI=F0 and LO=00 to HI=FF and LO=FF

- d. The Range is HI=E0 and LO=00 to HI=FF and LO=FF

- 7. a. A group of eight contiguous bits that occupy a single memory location in a Z-80 microcomputer.

- b. The storage location of a memory word.

- c. Computer instructions written in a form that the programmer can easily remember, but which must be converted into machine language later to be in computer readable form.

## Some Z-80 Microprocessor CPU Instructions

In this chapter, we shall define several important terms, including *operation, data byte, address byte,* and *device code*. We will also introduce you to several simple Z-80 microprocessor instructions that you will use in the programs provided in Chapter 5. Our objective is to gradually introduce you to the entire Z-80 instruction set and to provide programs that permit you to see how some basic instructions are used.

#### **OBJECTIVES**

At the end of this chapter, you will be able to do the following:

- Define computer program.

- Define operation.

- Provide simple representations for single-byte, two-byte, threebyte and four-byte instructions.

- Explain the differences between the following kinds of program bytes: operation code, data byte, device code, HI address byte, LO address byte, and displacement byte.

- Define register.

- List the two sets of six general-purpose registers, and the six special-purpose registers in the Z-80 microprocessor chip.

- List which of the general-purpose registers are used as register pairs.

- Define accumulator.

- Define *increment*.

- Explain the operation of five common Z-80 microcomputer instructions: NOP, HALT, INC A, LD A, data, and JP address.

- Define the immediate addressing mode.

- For a 2.5-MHz Z-80 microcomputer, list the execution times of the following microcomputer instructions: NOP, HALT, INC A, LD A, data, and JP address.

#### WHAT IS A COMPUTER PROGRAM?

A computer program can be defined as a sequence of instructions that, taken as a group, allow the computer to perform a sequence of operations to accomplish a desired task. What is the task? It could be anything within the capability of the computer, associated external input-output devices, and memory.

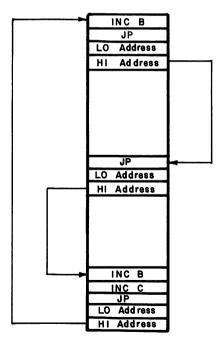

Programs are stored in memory as a sequence of 0's and 1's (bits) that the computer can read, interpret, and execute in sequence, one at a time. For the Z-80, these bits are stored in 8-bit groups called bytes. A single instruction may occupy one, two, three, or four consecutive bytes of memory. The Z-80 executes a program by reading an instruction, interpreting the bit patterns, and then performing the tasks necessary to complete the operation defined by the instruction. Consecutive memory locations are read until an instruction is reached that tells the computer to halt or jump to another memory location for the next instruction.

Programs do not include just instruction bytes. Data bytes must also be included in programs to provide needed information. For example, a program designed to add two numbers must include the numbers to be added (data bytes) as well as the instructions to perform the addition operation (instruction bytes). Other types of bytes that make up a program include address bytes, device code bytes, and displacement bytes. These are discussed later in this chapter.

The minimum Nanocomputer configuration provides 4K bytes of read/write memory for user program storage. This is sufficient to store highly complex programs. Two very critical terms in our definition of computer programs are "instruction" and "operation." Now let us investigate their meaning further.

#### INSTRUCTIONS AND OPERATIONS

An *instruction* is a set of characters that defines an operation, alone or together with other information, and which together causes the computer to perform the operation. An *operation* is defined as a specific action which a computer performs whenever an instruction calls for it (e.g., division, addition, subtraction, ORing, etc.). The number of different operations that a computer can perform and the speed with which it can perform such operations provide a measure of how "powerful" the computer is. The operations that the Z-80 microprocessor chip can perform can be subdivided into the following groups:

> Data transfer group Arithmetic and Logic group Rotate and Shift group Bit Manipulation group Jump, Call, and Return group I/O and machine control group.

# MULTIBYTE INSTRUCTIONS

Many instructions within the Z-80 instruction set require only a single byte, but others require two, three, or even four successive bytes before they can be executed. We call these latter instructions *multi-byte instructions*. A few definitions are in order:

- single byte instruction—An instruction consisting of eight contiguous bits that occupy a single memory location. two-, three- or four-byte instruction—An instruction consisting of in-

- two-, three- or four-byte instruction—An instruction consisting of information that occupies two, three, or four successive memory locations.

The number of bytes required for an instruction is closely related to the complexity of the instruction and the information that it requires. The Z-80-instruction set was designed as an extension of the instruction set for a microprocessor, the 8080, manufactured by Intel Corporation. To maintain consistency between the two instruction sets, certain compromises in the definition of the new Z-80 instructions were necessary. This has resulted in making the structure of the Z-80 instructions a bit more complicated than that of the 8080. However, this sacrifice more than compensated by the fact that almost any program written for an 8080 microprocessor can be executed on a Z-80 microprocessor without any changes. The 8080 microprocessor is historically a very important microprocessor chip, for which a lot of software already exists. Hence, this "upward compatibility" is especially beneficial.

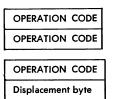

Simple representations for one-byte, two-byte, three-byte, and fourbyte Z-80 instructions are given in the following paragraphs. Note that in all but one four-byte instruction type, the first one or two bytes are operation codes which specify what the instruction does, and the last bytes are information needed to carry out the instruction. We shall discuss this in great detail when we introduce specific instructions. The instruction formats are presented here merely as a preview of things to come. Since operation codes follow each other sequentially in memory at numbered addresses, we write them down in vertical columns like a table, unlike the page you are reading which is written horizontally.

Single-byte instructions require only on operation code and no auxiliary information.

OPERATION CODE

Two-byte instructions have four forms:

| OPERATION |      | CODE |

|-----------|------|------|

| Data      | byte |      |

| OPERATION   | CODE |

|-------------|------|

| Device code |      |

We shall explain shortly what is meant by the terms data byte, device code, and displacement byte.

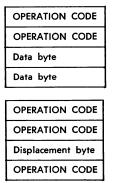

Three-byte instructions have three forms:

| OPERATION CODE |  |

|----------------|--|

| Data byte      |  |

| Data byte      |  |

| OPERATION CODE  |

|-----------------|

| LO address byte |

| HI address byte |

| OPERATION CODE    |

|-------------------|

| OPERATION CODE    |

| Displacement byte |

We have previously discussed the concepts of LO and HI memory address bytes.

OPERATION CODE

LO address byte

HI address byte

Four-byte instructions have four forms:

| OPERATION CODE    |

|-------------------|

| OPERATION CODE    |

| Displacement byte |

| Data byte         |

As you may well guess, the last two four-byte instruction types represent fairly complicated instructions. Several examples of these instruction types are discussed in detail later.

# TYPES OF INFORMATION STORED IN MEMORY

The memory in a Z-80 microcomputer consists of a sequence of successive 8-bit locations. Everything that the microcomputer does with respect to the memory is done eight bits at a time. There exist six different kinds of information that can be stored in memory:

8-bit operation codes

8-bit data bytes

8-bit device codes

8-bit LO address bytes

8-bit HI address bytes

8-bit displacement bytes

Therefore, in a Z-80 program, we simultaneously store instruction codes, data bytes, device codes, address bytes, and displacement bytes in the same memory. All of these kinds of information can exist side by side. It is reasonable to inquire how the microcomputer is able to distinguish among them.

The basic answer is that the order in which the information appears dictates what type of information it is. Computer programming is a precision activity: ONE programming mistake and your program will not operate correctly. A microcomputer program starts at a chosen memory address and then proceeds operation by operation to a final memory address. The operation codes always tell you what to expect in the program, i.e., whether the next memory byte is a data byte, address byte, device code byte, another operation code, or a displacement byte.

#### **OPERATION CODE**

The first byte of a Z-80 instruction is always an operation code. Note that some instruction types begin with two operation code bytes. These instructions are extensions of the old 8080 instruction set. If the first byte of an instruction is CB, DD, ED, or FD, then the second byte must also be an operation code. The operation code byte(s) define the specific action that the Z-80 microprocessor chip will perform. Specific actions include data transfer, arithmetic operations, logical operations, branch instructions, stack operations, I/O operations, and machine control operations. If you desire to know what the microcomputer will do next, the operation code(s) of the following instruction will tell you. Synonyms for operation code are op code and *instruction code*.

#### DATA BYTE

Data byte is defined as the 8-bit binary number that the Z-80 microprocessor chip will use in an arithmetic or logical operation or to store in memory. The eight bits can be in any kind of digital code: binary code, binary coded decimal, ASCII code, etc. When we use the term data byte, we mean that the eight bits are not an operation code, memory address, device code, or displacement byte. When you do microcomputer programming, you will find it very convenient to include data in your program where and when you need it, rather than having to refer to a remote memory location for the eight or sixteen bits of data that you need.

# **DEVICE CODE**

Device code, for a Z-80 based microcomputer, is the identifier for the specific input or output device with which you desire to exchange eight bits of information and a device select pulse. We shall talk about the details of how this is done later. The important point is that the device code is an 8-bit code, which means that you can address two to the eighth power, (2\*\*8), or 256 different output devices. On your microcomputer, output device codes 04 and 07 are reserved for the Nanocomputer operating system.

As you proceed through this text, we encourage you to study carefully what is meant by device code and *device select pulse*, and how to use the latter to force input-output devices to operate in synchronization with your microcomputer program.

#### HI AND LO ADDRESS BYTES

We would like to remind you again that the *HI address byte* is the eight most significant bits, or highest value bits, and the *LO address byte* is the eight least significant bits, or lowest value bits, in the 16-bit Z-80 microprocessor memory address word. Since the Z-80 is an 8-bit microprocessor chip, which obtains data or instructions from memory eight bits at a time, it has no choice but to handle the 16-bit memory address information as a pair of 8-bit address bytes.

#### **DISPLACEMENT BYTE**

Displacement bytes appear in instructions which use Indexed Addressing. Indexed Addressing is a technique for defining a two-byte memory address by adding a Displacement to a 16-bit number which resides in a special location on the microprocessor chip called an Index Register. A Displacement is a signed two's complement number. We will not attempt to define signed two's complement now. Suffice it to say that it is a method of representing binary numbers which facilitates manipulation of negative numbers. This will be carefully explained later.

Do not feel overwhelmed if many of the above terms appear unfamiliar. A complete understanding of all these terms will come only from experience in using instructions to program your Z-80.

# WHAT IS A REGISTER?

A register is a short-term storage circuit the capacity of which is usually one computer word. Single registers in the Z-80 microprocessor chip store a single byte, i.e., eight contiguous bits. A variety of registers exist within the Z-80 chip, some of which you use to store digital information and others which are used by the chip itself as it performs instructions. In general, we can subdivide the registers of the chip into two different sets: those that you can address from a program and those that you cannot address from a program. The program-addressable registers include:

• two sets of 8-bit general-purpose registers addressed singly or in pairs,

| Set | 1: B register | Set 2: B' register |

|-----|---------------|--------------------|

|     | C register    | C' register        |

|     | D register    | D' register        |

|     | E register    | E' register        |

|     | H register    | H' register        |

|     | L register    | L' register        |

Set 2 is referred to as the alternate register set (ARS).

- an 8-bit ACCUMULATOR for each set, also known as registers A and A'.

- an 8-bit FLAG register for each set, also known as registers F and F'.

- the 16-bit STACK POINTER register (SP).

- the 16-bit PROGRAM COUNTER REGISTER (PC).

- two 16-bit INDEX REGISTERS (IX) and (IY).

- the 8-bit INTERRUPT PAGE ADDRESS register (I).

- the 8-bit MEMORY REFRESH register (R).

These are the only registers with which you can directly exchange information with the aid of a suitably written microcomputer program.

#### **GENERAL-PURPOSE REGISTERS**

The two sets of six general-purpose registers—B, C, D, E, H, and L, and B', C', D', E', H', and L',—temporarily store single bytes of

information. Since they are located within the Z-80 microprocessor chip, the exchange of information from one general-purpose register to another can be very fast. The exchange of information between any of these general-purpose registers and the accumulator is also fast. These registers can be used singly or in pairs. For Set 1, the three 16-bit register pairs are:

- the 16-bit general-purpose register consisting of the B register and the C register. When used for memory addressing, the B register corresponds to the HI memory address and the C register to the LO memory address.

- the 16-bit general-purpose register consisting of the D register and the E register. When used for memory addressing, the D register corresponds to the HI memory address and the E register to the LO memory address.

- the 16-bit memory address register and general-purpose register consisting of the H register and the L register. When used for memory addressing, the H register corresponds to the HI memory address and the L register corresponds to the LO memory address.

The registers are similarly paired for set 2.

#### ACCUMULATOR

The accumulator is an 8-bit register within the Z-80 microprocessor chip in which the result of most arithmetic and logical operations are placed. In the case of the Z-80 microprocessor chip, the accumulator register is located within the chip and contains a single byte of memory storage capacity, i.e., eight bits. Pay particular attention to what you can do to the contents of the accumulator. For example, you can add, subtract, or compare data with the contents of the accumulator. You can increment or decrement its contents by one. You can exchange the contents of the accumulator with a memory location, or with inputoutput devices. You can rotate the bits in the accumulator either to the left or to the right. You can perform logical operations on the accumulator, including AND, OR, and exclusive-OR. You may not understand some of these terms at the moment. Be patient, we shall get to all of them. The other registers within the Z-80 microprocessor chip will be discussed in more detail later.

#### SOME Z-80 INSTRUCTIONS

In Chapter 5, you will begin to test microcomputer programs. The programs that you will try will contain some single-byte, two-byte, and three-byte instructions, including the following:

| 00            | NOP         | No operation                                   |

|---------------|-------------|------------------------------------------------|

| 3C            | INC A       | Increment contents of accumulator by 1         |

| 76            | HALT        | Halt the microcomputer                         |

| 3E            | LD A,data   | Move the immediately following data byte       |

| <data></data> |             | <data $>$ to the accumulator                   |

| 32            | LD (addr),A | Store the contents of the accumulator in the   |

| LO            |             | memory location addressed by the               |

| HI            |             | following two bytes (addr) in this three-byte  |

|               |             | instruction.                                   |

| C3            | JP addr     | Unconditional jump to the memory address given |

| LO            |             | in the following two bytes in this three-byte  |

| HI            |             | instruction.                                   |

Please note that the above list contains instructions with only singlebyte operation codes, i.e., the first byte in each instruction. The hex operation code appears in the first column next to its associated mnemonic.